前面曾提到过,传输线的容性负载会降低信号在传输线中的传播速度(v)和Z0。许多传输线方程,计算程序,以及文章和教科书中都是以PCB为一个没有通孔,连接器或ICs的理想PCB假定为前提的。对这些因素的忽略是造成PCB设计迭代增加的一个最普遍原因。虽然,裸板计算结果往往会告诉我们有些线条并不需要采用传输线。但在实际应用中,却都要求使用传输线技术。有些线条则需要通过改变它们的几何参数或终端电阻才能获得较好的匹配。为了缩短产品进入市场的周期和改善它们的可靠性,我们必须在考虑到容性负载的条件下来设计工程实践中所需要的传输线。

引起容性负载的一个原因是IC的插针或其他元器件(如二极管、晶体管等)连接到一个传输线的结果。在一个线条的每个端头上总会存在有这样或那样的元器件。虽然它们的电容会对传输线终端的质量产生某些影响,但并不会改变传输线的Z0或v。引起线阻抗Z0或v降低的真正原因是沿着线长度上所连接的元器件插针的存在。诸如,一个典型的多点总线(比如,微处理器的记忆和地址总线)。

我们也不能忽视杂散的寄生电容的影响。在每一个通孔上的杂散寄生电容(典型值为0.2~2pF之间)都会引起阻抗的局部降低(请参阅图2-5-5)。一个传输线线条上面通常都会有许多通孔。它们的存在会大大降低所预期的平均Z0和v。有关通孔电容的更为详尽的讨论可以参阅有关文献中的“通孔电容”内容。

在原丛书所附的文献“短路传输线谐振”一文中曾描述了在一个线的端头的容性负载是如何在线条中引起数量巨大的振铃和上冲的。倘若下列将要讨论的一些基本指导原则在设计初期就已经给予关注的话,上述这类现象将基本上不会发生。

假如一个金属体,如一个散热器或一个罩壳的壁这类薄金属板被置于靠近一根微带传输线时,它也会增加线条的杂散寄生电容。塑料体或其他薄板、电缆或聚合物靠近一根微带线时,也同样会增加它的杂散寄生电容。在一根微带线周边5mm距离之内唯一允许存在的是空气或类似气体和真空状态。

在一根带状线两边的参考面可以对它附近的金属或塑料所形成的杂散寄生电容构成某种程度的屏蔽。但它仍然会受到沿着它的长度上所连接的元器件插针的电容的影响。

在有些情况下,容性负载的影响可以通过在受影响区段内缩小线条宽度来加以补偿。在文献(路面上的)坑洼的一文中提供了一些适用于“点”电容(如,通孔或器件连接)补偿的计算方法。

更为实际的做法是使用微波RF设计工程师所使用的技术。通过调节平面上所钻有的通孔的直径以及它们焊盘和净空孔(阻焊盘)的大小来保持跨越通孔所要求的Z0值。一般地说,有相当一部分RF设计技术并无益于EMC性能的改善,甚至会影响到EMC性能。就上面所讨论的情况来看,在参考面上形成大直径的孔洞就会给返回电流造成问题。它们的存在还会增加平面阻抗,导致较高的CM发射电平和较差的抗扰度。

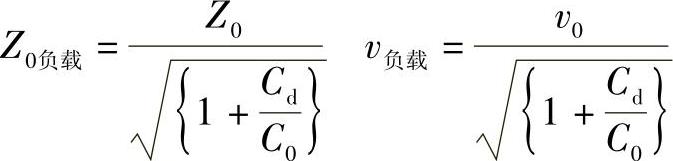

用于计算传输线容性负载影响的简单公式如下:

这里,Cd——单位长度上的负载电容;

C0——单位长度上的本征(裸板)线电容;

v0——本征(裸板)线速度。

Cd可以很容易地从一个PCB电路设计中计算获得。例如,若在一个150mm长的线段上连接有10个IC的10个插针。而又假设每个通孔、焊盘和IC插针的总电容为10pF,那么,我们在沿着该线条的150mm线段上分布着的电容则为100pF。这使得Cd为100/150或0.667pF/mm(66.7pF/m)。(https://www.xing528.com)

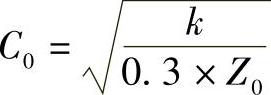

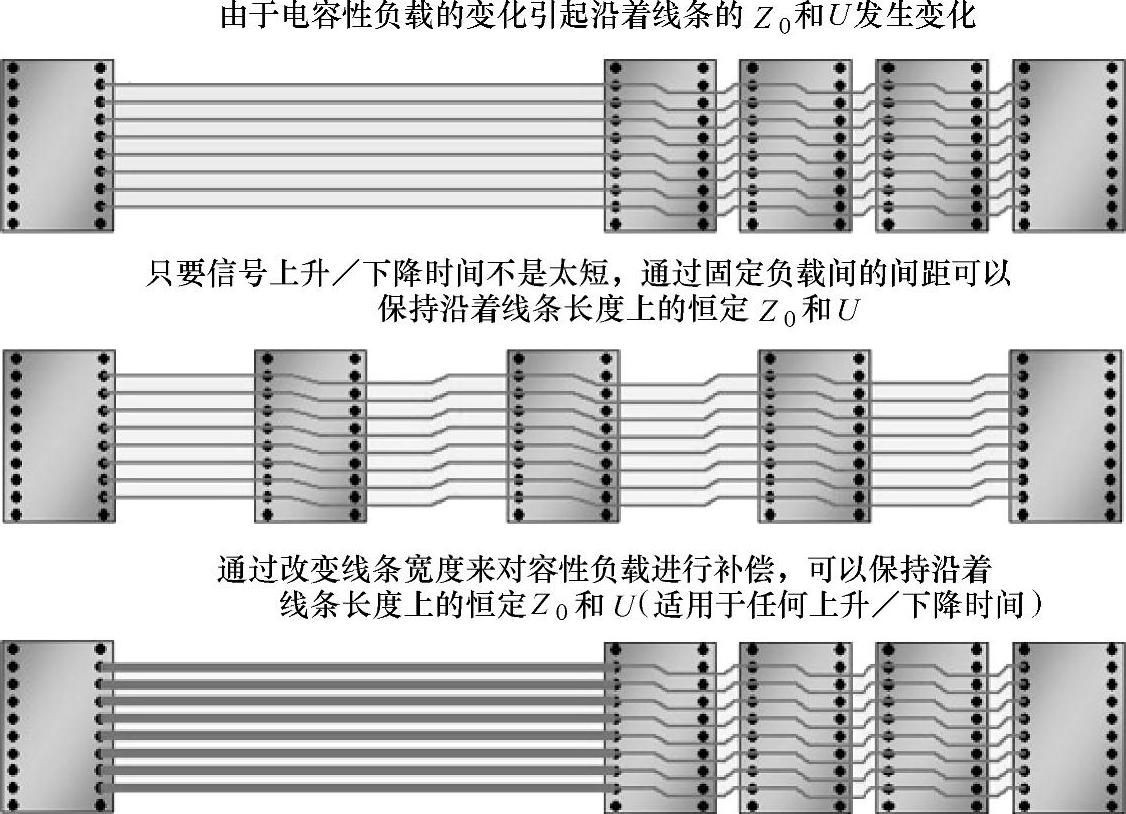

C0和v0可以从IEC 61188-1-2:1998给出的公式中求得。就我们的例子,因为v0和Z0是已知的,所以,它的C0可以从下式求得

因此,以pF/mm为单位的C0可以改写为

但是,一般地说,使用一个场求解器(程序)对一根线条的每个线段分别进行求解所获得的C0和v0要远优于或精确于上述的计算值。

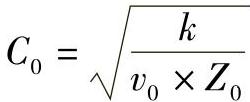

上列表达式所适用的线条长度则取决于要控制信号或噪声的上升/下降时间(或所关心的最高频率)。在上升/下降时间长到一根线条的整个长度和它的容性负载(由IC插针、通孔或其他物理特性所引起的)可以用一个平均值来代表的话,上列表达式则适用于整根线条长度(例如,图2-5-5中的1ns曲线)。

但是,在上升/下降时间短到(或频率高到)在一根线条长度中出现明显的阻抗不连续时(例如,图2-5-5中的300ps曲线),上列表达式仅适用于线条线段短到它的阻抗可以用一个平均阻抗值来代表的情况。而每一个线段中的线条宽度可以根据该线段的电容负载来进行调整。以使每个线段都有着相同的阻抗,如图2-5-12所示。

图2-5-12 在一个线条上的电容性负载

(图中没有显示线终止电阻)

但在上升/下降时间非常短的场合(或频率非常高时),以致在短到只有1mm长的线段中也会形成不可接受的阻抗非连续性(图2-5-5中的150ps曲线)。此时,上列的表达式已完全不再适用。假如这些信号或噪声不能通过低通滤波器滤去,唯一解决办法恐怕是只有设计不同的电路。例如,使用点到点串行数据总线来代替多点并行设计(电路设计将在后面的有关小节中讨论)。一个有用的技术是把线条布线于单一层面上。以使沿着它的长度上没有通孔存在。

因为数字器件的上升/下降时间是基于现代硅处理工艺水平这样一个基本事实。所以,上升/下降时间很自然地就会非常短。并且,随着时间的推移会变得更短。而由此所造成很高频率的核心噪声泄漏并进入它们的I/O插针很自然的也会随之变得很高,并将会变得越来越高。在这样的前提下,要想设计出在线条的整个长度上都匹配良好的传输线也就变得越来越困难。除非,如上所指出的,这些信号或噪声可以通过低通滤波器滤去。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。