当数字信号或噪声的上升和下降时间短于约150ps,或模拟信号或噪声频率高到2GHz以上时,阻抗匹配将会成为PCB结构和它的线条布线的至关重要的一个问题。对于这类信号或噪声,在过去的实践中,即便PCB线条布线中存在有如通孔等结构,我们也大都能够不必过于担心。但现今,则需要把它们作为沿着传输线所形成的阻抗非连续性来处理。

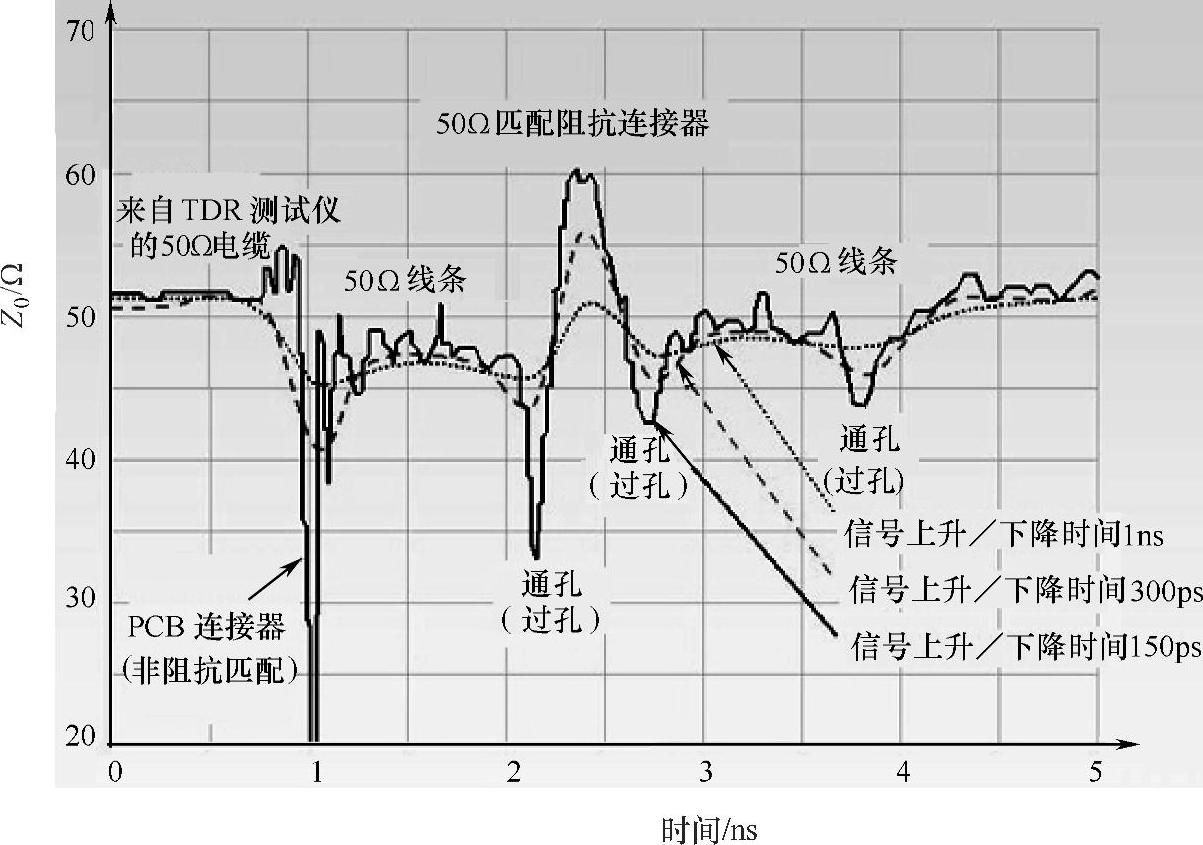

时间域反射计(TDR)是一个用来模拟或直视观察这个现象以及对真实PCB进行测量,以发现它们的设计是否正确或存在有线条错误的重要工具。将信号输入到一个被模拟的或真正的PCB结构中,并对所模拟的或测量的反射幅值进行测量和计时。最后,采用阻抗的时间域响应曲线来显示和分析其结果。使用这个TDR曲线的好处是,它们为设计工程师显示了在沿着一个线条长度上的什么位置出现了阻抗问题以及这个问题的严重程度。图2-5-5显示了用三个不同上升/下降时间的TDR测量的结果。

图2-5-5 使用具有不同上升时间的信号,在一个PCB上的TDR测量结果

图2-5-5显示了一个具有1ns上升和下降沿的数字信号所看到的一个PCB线条的平均阻抗的时间域响应。图中还告诉我们,连接器和通孔对特性阻抗的影响会随着上升和下降时间的延长逐渐趋于平滑。反过来说,当一个信号的上升和下降时间缩短时,由于连接器,通孔和其他结构所造成的阻抗非连续性会变得更为明显。图中的上升/下降时间分别为300ps和150ps的曲线就是说明这个变化的很好例子。(https://www.xing528.com)

使用非-返回-到-零(NRZ)编码的2.5GHz/s速率的串行数据所采用的基频为1.25GHz。这提示我们,为了获得一个合理振福的眼孔图,最大上升(和下降)时间不会高于200ps。在今后的几年里,已有打算将串行数据速率提高到5~10GHz。很明显,这不得不使我们必须考虑在上升和下降时间短于150ps情况下的传输线匹配问题。此时,连接器和通孔的存在会成为更为严重的问题。如何处理其中的一些这类问题和所需要采用的技术将在下面逐个讨论。

在图2-5-5的150ps曲线中,TDR上与阻抗匹配连接器位置相一致的曲线形状显示它的阻抗大约为60Ω。它的非尖锋形的顶部启示我们,即便在信号采用更短的上升/下降时,这个阻抗也不会有太大的改变。对一个50Ω传输线来说,显然,60Ω并不是最佳匹配。它所形成的反射系数为+0.09,但显然要远远优于把信号电缆直接连接到PCB的连接器。

但是,从TDR的显示中,我们仍可以看到,相对应一个携载上升/下降时间为150ps信号的通孔位置上的曲线仍然是相当尖锐。对这个信号来说,为了显示该信号的任何平坦或平滑顶部分,一个通孔本身是太短了。这提示我们,它的实际阻抗不再会被上升时间所平滑掉。因此,在存在通孔的情况下,我们有理由预期,对具有短于150ps上升/下降时间的信号将会经历甚至更低的阻抗、更高的反射系数和更差的SI和EMC性能。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。