最为普遍采用的掩埋电容技术称之为Zycon掩埋电容(Zycon Buried Capacitance,ZBC)。这个技术已被若干个计算机、手机和其他制造厂商使用多年了。在PCB中的每个0V或电源参考面都被转换成由非常薄介质所隔离的一对0V/电源参考面。这个技术由Zycon公司首先发明。后来Hadco公司将该公司收购,而Hadco又被Sanmina-SCI所并购。

Sanmina-SCI公司供应两类产品:ZBC1000和ZBC2000。ZBC1000使用了两层厚度仅为0.001in的FR4介质材料所隔离的一个铜质层构成的核。ZBC1000获得了900pF/in2的电容量(在公制系统中,这相当于大约为25μm的厚度的介质获得了140pF/cm2的电容量)。在ZBC2000产品中,使用的是厚度为0.002in的FR4介质材料。所获得的是500pF/in2的电容量(这相当于在公制单位系统中,51μm厚度获得了77.5pF/cm2的电容量)。但在实际应用中,当前似乎只看到ZBC2000在批量使用。

使用这些产品既不需要对PCB布局做任何的修改,也不需要由PCB设计工程师对它的Ger-ber文件做任何改动(一种用来计算体积的计算机软件)。PCB裸板制造厂商只是简单地使用一个ZBC1000核来代替在PCB上的每个0V或电源参考面即可。核的一面连接到0V参考面,另一面接到电源参考面。在原始PCB仅有单个0V参考面和单个电源参考面的场合,增设两层ZBC2000可以获得1000pF/in2的一个分布电容(150pF/cm2)。在频率为500MHz以上时,这个电容值是提供良好去耦合的最低要求。

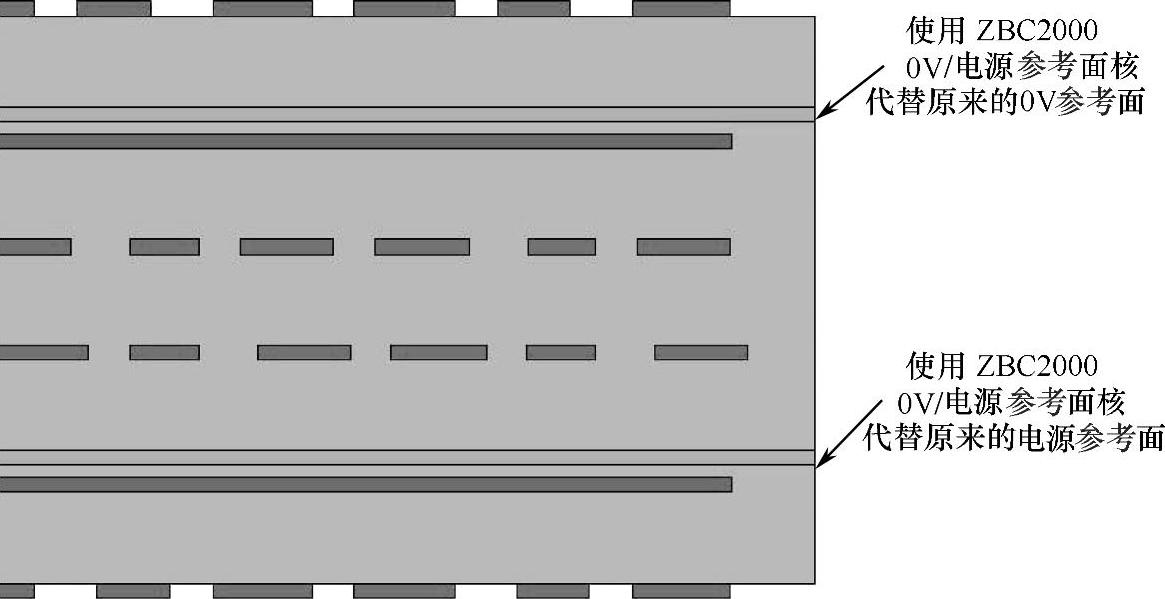

图2-4-23图示了一个具有相等层距的6层叠层的PCB。这类PCB在上世纪九十年代使用的非常普遍。但是在安装有现代IC以及它们所具有的快速开关沿情况下,由于它们的高阻抗电源总线,恐怕不可避免地会有很差的EMC性能。用层距很小的平面对,如ZBC2000,来代替每个参考面将会明显地降低它们的电源总线阻抗。并且至少在高到1GHz频率以内都会因此而降低它们的发射。图中显示了已在其中嵌入了两个0V/电源参考面核的PCB。

图2-4-23 使用ZBC的一个典型六层叠层的PCB

从EMC性能来说,图2-4-23中所示的叠层方式并非最佳形式。例如,通过把两个新的0V/电源参考面对分别移至更靠近PCB的两个外部表面或缩短携载电源总线电流的通孔长度都将会使它的EMC性能得以进一步改善。这个问题还会在本篇的第6章中做更为详细的讨论。

通过使用一个0.002in厚的FR4核在一个PCB中提供掩埋电容的技术是受到专利权保护的。因此,希望使用这个技术的PCB制造厂商的唯一合法途径是从Sanmina-SCI公司购买ZBC材料。虽然材料本身并不十分昂贵,但必须支付购买应用它的技术费用。这样就增加了产品的成本。但由于省掉了大多数/全部去耦电容(大容量去耦电容除外),在批量生产中的PCB的净成本与原先的相比仍然可以基本上持平,甚至还会有少许下降。再加上该技术的采用不仅还会节省电路在PCB上所占有的面积以及现场生产产量的提高和可靠性的进一步改善,而且还具有减少了所使用的元件数量的优点。因此,不论是从技术观点出发还是从经济效益考虑,都有充分的理由去促使我们采用ZBC产品。

然而,倘若你使用一个具有不同厚度的核,或使用50μm的预浸处理层来形成你自己的掩埋电容时,就完全有可能避免侵犯专利权问题。但在这样做以前,最好咨询一下专利权律师较为稳妥。从工艺上来说,在经手和处理这样微薄的FR4材料时,材料的质量和精确度以及清洁程序极为重要。特别是假如产品产量很高的情况下尤为如此。所以,假如计划选用这个技术的话,就不再应该按照正常采购步骤或仅仅根据所报最低价格来作为唯一选择PCB供应商的依据。

最初,ZBC只是打算用来降低在PCB上元器件的数目而研制的。所以,它能有效地减小电路的尺寸和提高产品的可靠性(这是因为焊接数量的减少,而不可靠焊接也就会成比例下降)。Hadco公司曾指出:他们的客户声称,在正常情况下,ZBC的使用可以使EMC的发射降低6~16dB之间。但是要想从掩埋电容技术获得最佳EMC性能,就应该提供足够的电容量以避免还要使用任何分立式去耦电容(“大容量”电容除外。典型的如4.7μF或更大者),以避免由于它们的并联谐振形成电源总线阻抗中峰值的出现。

可惜的是,在频率为500MHz以下时,150pF/cm2(1000pF/in2)可能不足以提供良好的去耦性能。当然这还需要取决于IC和其他元器件所要求的瞬态电流。因此,为了能够做到完全消除分立式去耦电容的使用,并从而消除它们的并联谐振,我们可能需要选用比FR4的k值更高的材料。

目前,在掩埋电容技术领域中,研制和开发工作都正在大规模地进行着。正在发展的用以代替FR4的材料包括有:

1)填充有环氧树脂的EMCap®(Sinmina公司)陶瓷粉末。k=36。(https://www.xing528.com)

2)填充有聚亚胺的Hi-KTM(Dupont公司)陶瓷粉末。k=12。

3)填充有环氧树脂的C-Ply(3M公司)陶瓷粉末。k=21,5.5nF/in2(850pF/cm2)。

4)改进过的FR4 FaradFlexTM(Oak-Mitsui Technology公司)。k=4,具有12μm、16μm和21μm的不同厚度。该公司还在研制具有更高k值的不同材料。据称,能给出高达40nF/in2(6nF/cm2)的电容值。

5)没有黏合剂的陶瓷粉末(Fujitsu公司)。k=400,300nF/cm2。

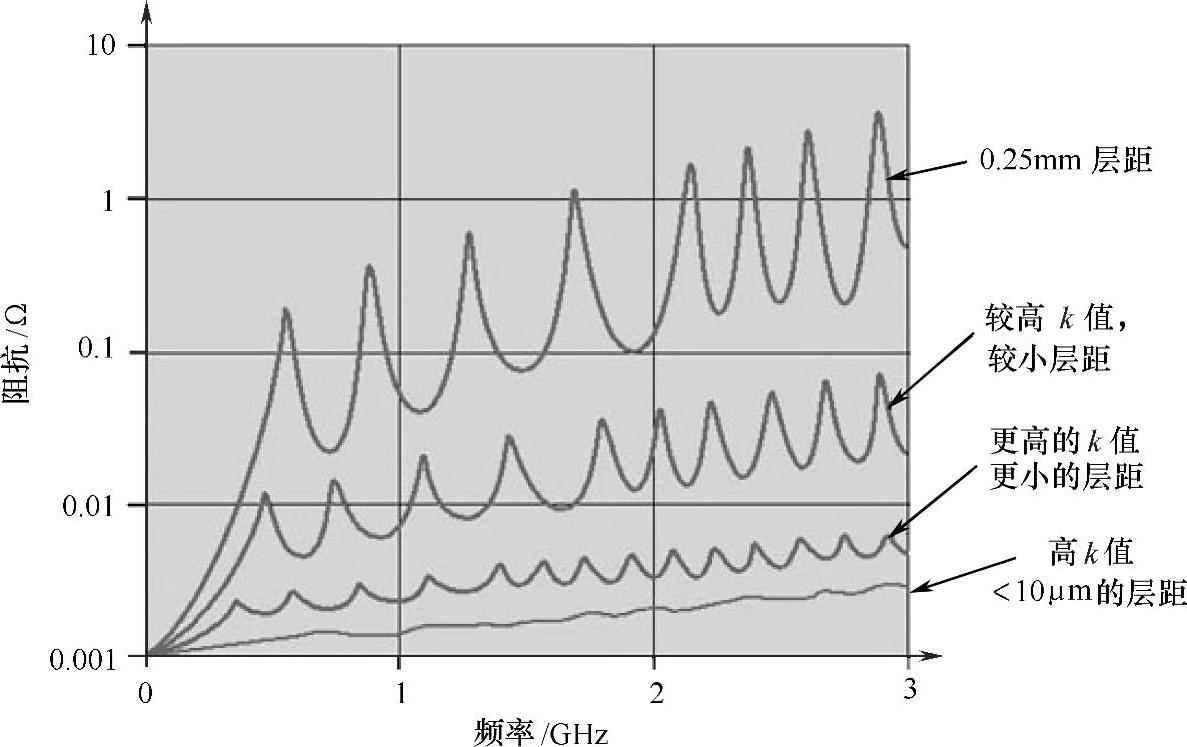

图2-4-24 掩埋电容对0V/电源参考面对空腔谐振的典型影响

(作为一个例证,仅适用用没有安装分立式去耦电容的PCB)

对平面来说,使用高k介质可以降低传输速度,但也会下推它们的空腔谐振频率——这恰恰是我们所不希望的。因为它会引起更多的谐振峰值出现在一个给定的频率范围——这恰恰也是我们所不希望的。但较小的层距增加了空腔中的耗散,降低了它的Q值因数以及降低了谐振的峰值幅度,特别是在层距为50μm(0.002in)或更短的层距时。图2-4-24所示为降低平面对层距对电源总线阻抗的影响以及增加它们之间介质的相对介电常数k对电源总线阻抗的影响。

使用厚度为5μm(0.002in)的C-Ply进行测试发现,在0V/电源参考面空腔中的Q质因数为1。这意味着临界阻尼或衰减——完全不产生谐振。因为该测试材料的k值为21,这样一个薄层所获得的4nF/cm2电容值给出了远远高于在实际PCB上使用分立式元器件所能获得的去耦性能。

使用这样微薄的介质层,会很自然地关心它的击穿电压。有趣的是,我们发现ZBC1000的额定电压为大于2500V,但测试则是在DC 250V条件下进行的。而ZBC2000则是在DC 500V下完成的。在一个用10μm厚的FaradFlex制成的样品上进行的测试发现,它的耐压为500V。从材料的耐压角度出发,恐怕人们最为关心的就是在制造过程中如何在工艺上保证处理这样微薄介质时,周围环境的超净程度以及(当使用预浸处理层来代替核时)层间校准和定位的精度。

最近有报道指出,已有获得50nF/cm2的技术不久就可以商品化。Fujitsu公司也声称,它们的新的陶瓷粉末技术将会比陶瓷/聚合物合成涂层的价格便宜40%。所以可以预见,掩埋电容的使用很可能将会很快的完全取代分立式的去耦元件的使用(低于4.7μF)。新技术使用的层距仅为25μm(0.001in)或更小,并具有更高的k值。在这样的PCB中,并联去耦元件的谐振将仅倾向于发生在10MHz以下。而在这样的频率上,大部分实用尺寸的PCB都是效率低下的辐射器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。