在本章4.2节中,我们曾建议使用小面积电源平面来帮助降低去耦电容的互连接电感。而在使用多个并联电容时,它又能帮助降低IC的电源总线阻抗。当一个电源平面延伸进入并包围了所有它的电源总线所供电的IC以及所有它们的去耦电容时,我们发现,这时所拥有的并联电容的数目会远超过我们所想象的数目。

正如在本章4.2.9节中所描述的,当使用不同电容值的并联去耦电容时,大面积电源平面的使用提供了在频谱上如此靠近的许多串联谐振,从而使得由并联谐振所引起的高阻抗却变得非常低了。

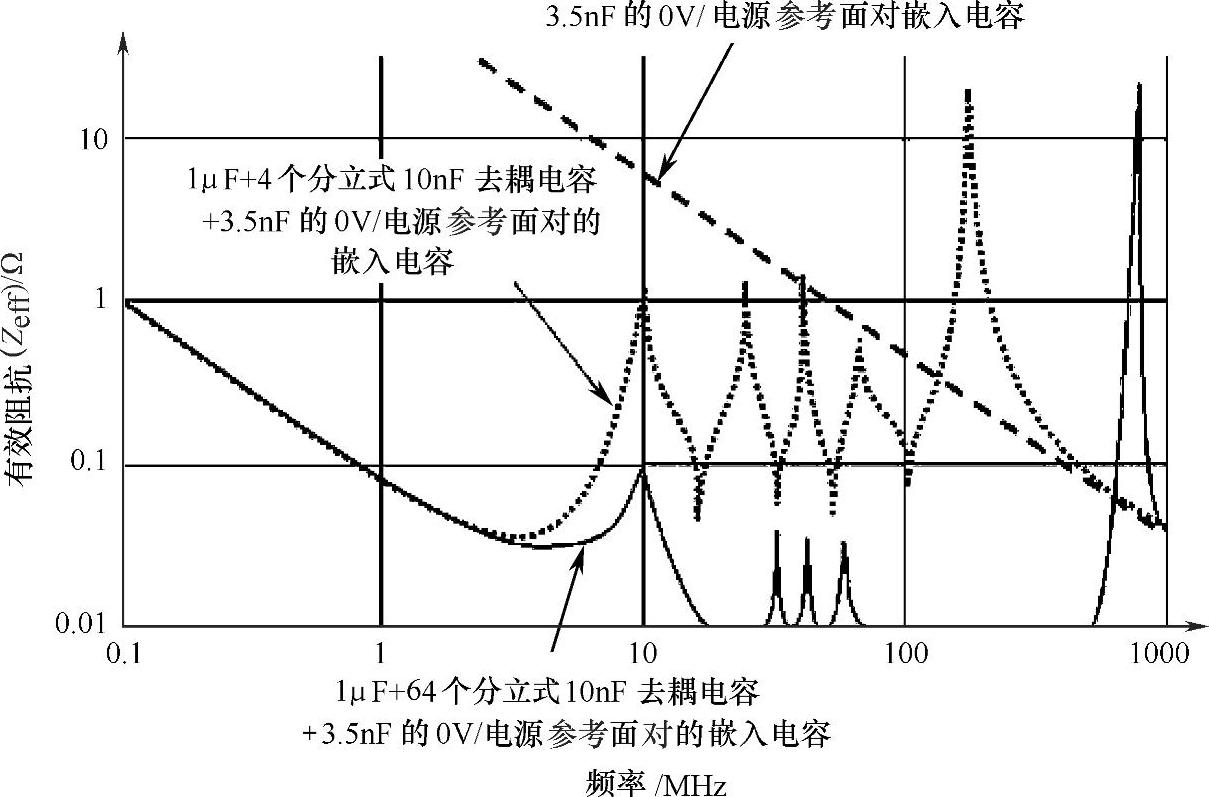

为了利用这个优点,以及帮助防止在0V/电源参考面对中的空腔谐振,我们建议把去耦电容分散安置在整个电源平面范围,而不仅仅只是在接近IC的位置上。但去耦电容间的间距不应大于25mm以及通过仔细的布局使每个去耦电容的个体电感降至最低(请参阅本篇第3章的图2-3-8)。最后,还要对所使用的去耦电容本身进行仔细选择。从电流通路的阻抗角度出发,这个做法就是在接近每个高阻抗电流通路(并联谐振)的地方形成了另一个低阻抗的电流通路。由此,IC的电源总线电流总是能找到一个低阻抗通路。下面的图2-4-20显示了选自UMR的与上述完全相同的一个例子。

图2-4-20显示了密苏里大学,诺拉分校(University of Missouri-Rolla)的一些实验结果。它揭示了在把10nF去耦电容的数目从4个增加到64个的情况下,大大地降低了大多数并联谐振的幅值。然而,最高频率谐振(由0V/电源参考面电容和它的很小的ESL所引起的)在幅度上却并没有减小,只不过是把它推移至更高的频率位置上而已。

(https://www.xing528.com)

(https://www.xing528.com)

图2-4-20 多个去耦电容和一个0V/电源参考面对篏入电容的组合使用

我们观察到一个有趣的现象:当0V/电源参考面对之间的层距小于250μm(0.001in)时,去耦电容相对于它所去耦的IC的位置设置变得不再那么重要了。这也就会给PCB布局的设计带来了一些便利之处。

虽然图2-4-20的曲线来自实验的结果,并使用的是大量相同(除了一个以外)电容值的电容(10nF)。但有关文献告诉我们,每一个电容都有着与它本身有关的不同互连接电感(大约在1~8nH之间)。因此,这些去耦电容都有着各自不同的SRF。正像假如它们的电容值各不相同,但它们的互连接电感都相同的话,它们也将会有着不同的SRF。光从这一点出发,我们可能得出的一个结论是:假如所有的电容元件都选用不同的值,但只要它们各自的布局上都获得了最低可能的互连接电感的话,则在200MHz和最后(大的)谐振之间将可能形成较小的阻抗。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。