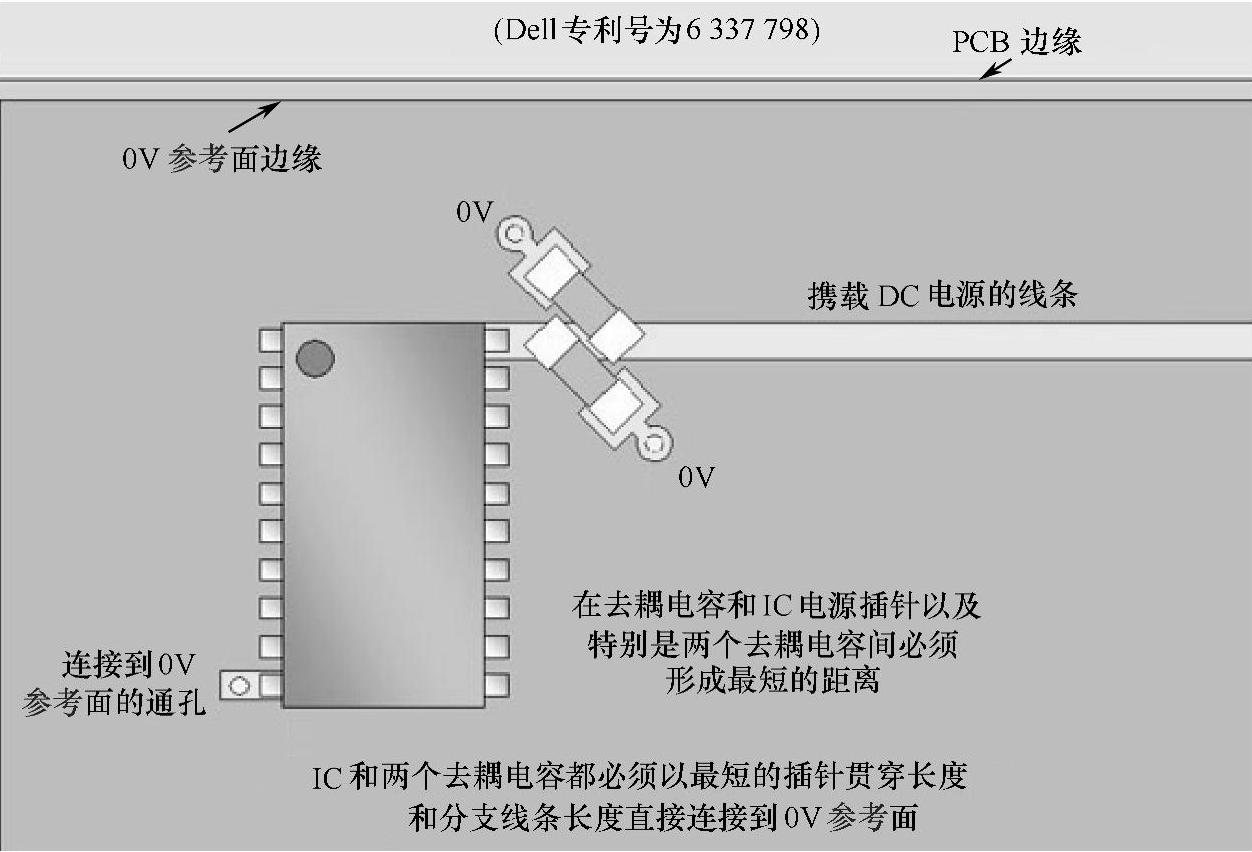

一个去耦电容的ESL是由于在它内部流动的电流所引起的。如前所述,降低ESL的一个方法是把两个去耦电容以相反走向安置在一起,从而使它们的内部电流所引起的磁通相互抵消。图2-4-14中所示的就是这种方法。显然,这个技术可以用于任何数目的去耦电容。这里再次强调,假如有读者打算采用这个技术,请注意不要侵犯到Dell公司的专利权(专利号为:6337798)。

表面安装三端馈通电容和特别是X2Y®衰减器都具有一个位于它几何中部的,接到它们的0V参考面的通孔(或两个相互对称位置上的通孔)。两者都有着比类似尺寸的两端电容要低的ESL。这是由于在电容器内部的磁场被部分抵消的缘故。而磁场之所以会被部分抵消则是由于其内部有两个相反方向的电流通路,而且这两条通路至少部分是通过元器件结构本身的。对于一个给定的电容值和封装尺寸,结果是形成了较高的SRF以及在SRF以上形成的较低阻抗。X2Y®衰减器具有一个特殊的三电极内部结构,从而使它可以获得要比普通的三端电容更好的内部磁通相互抵消的效果。

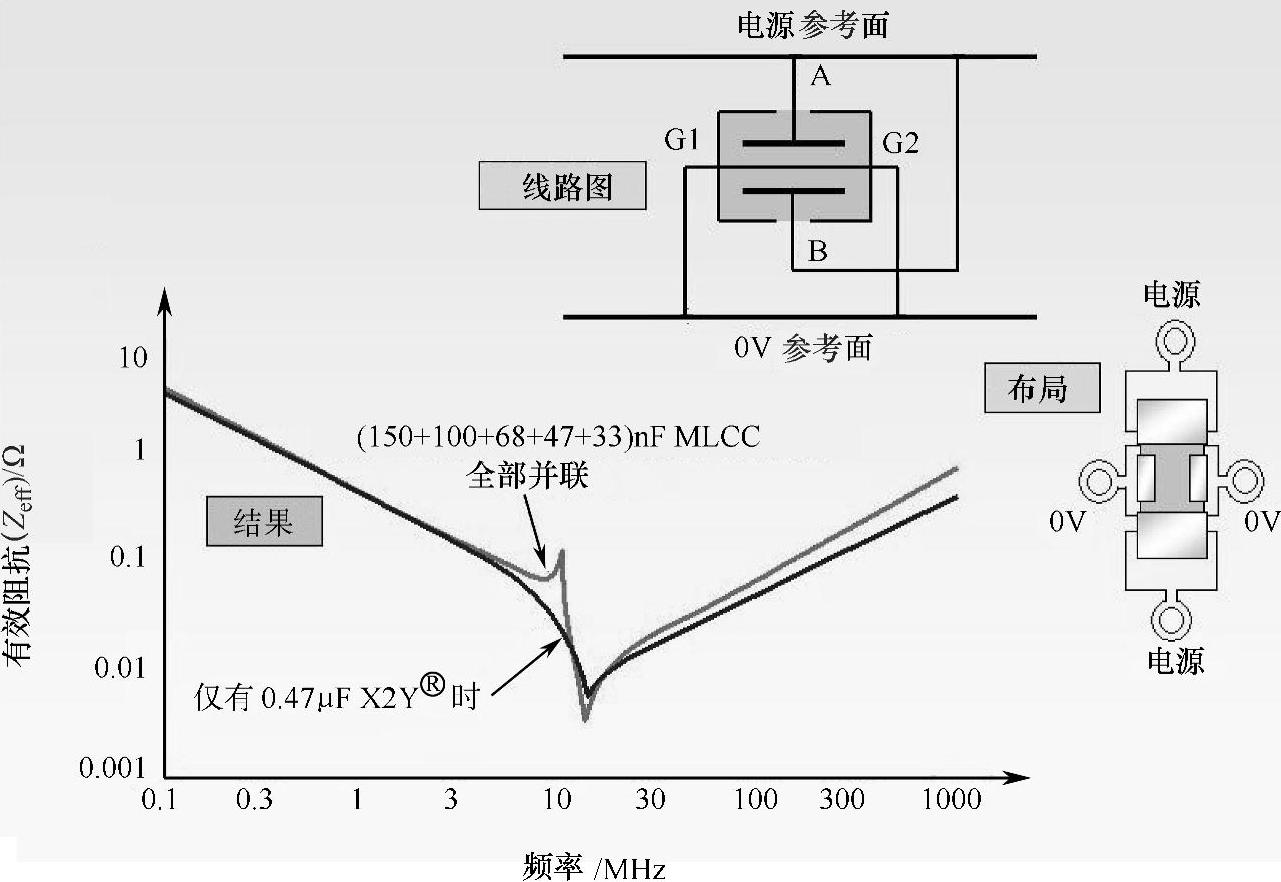

图2-4-15所显示的是把一个X2Y®衰减器与0V和电源参考面一起使用时的电路图和焊盘设计。图中还插入了用于对照的阻抗响应曲线。其中的一个是470nF的X2Y®衰减器的频率阻抗曲线。与其相对照的是由5个普通两端MLCC去耦电容(150nF+100nF+68nF+47nF+33nF)相并联所获得的频率-阻抗曲线。对照结果显示,单个X2Y®衰减器具有一个控制较好的阻抗曲线。并且在SRF以上时,它的阻抗也较低。这提示我们(至少在这个案例中),X2Y®衰减器以及它的内部互连接获得的电感要比5个并联的MLCC的来得低。

图2-4-14 通过磁通相互抵消降低ESL(https://www.xing528.com)

图2-4-15 用一个X2Y®衰减器来完成去耦合

(这个例子假定同时使用了0V和电源参考面)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。