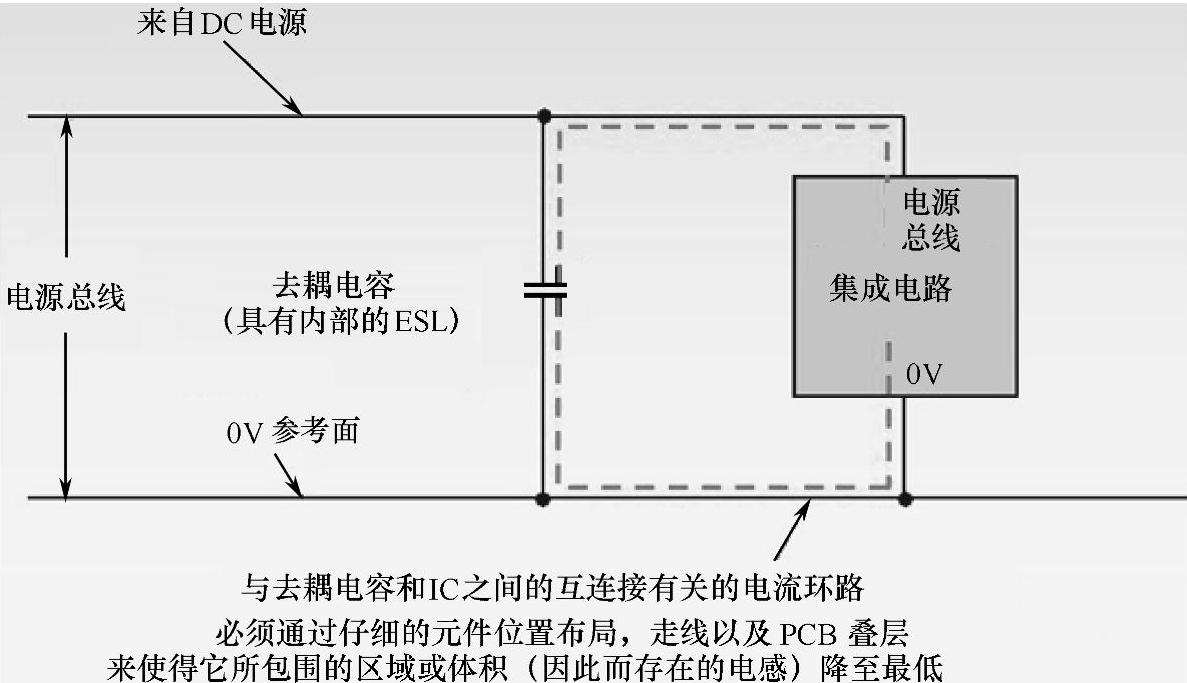

为了最大限度地降低磁场和电场的发射,由去耦电容和元件的电流环路所包围的面积必须最小化。

因为这里讨论的是PCB的高级设计技术,所以,我们在这里假定,PCB上使用的是高度完整的0V参考面。图2-4-3显示了我们所关心的电流环路的电路图。而图2-4-4所示的是一个相应的布局。

正如前面所提到的,重要的是在去耦电容和IC之间形成完整的电源电流环路。该环路还应将引线框、搭接导线以及IC的硅材料包括在内。由于通常情况下,我们无法得知在IC内部电源电流的通路,所以这里的讨论并不考虑它的影响。但是,当选择元器件或设计FPGA或ASIC时,重要的是要确保不会由于它们内部电源总线的存在而使得PCB设计工程师无法设计出足够良好的去耦合系统来保证在PCB层次上获得良好的EMC性能。有时仅仅就为这个目的而在网格焊球阵列(BGA)上设计上百个插针专门用于0V和电源连接。扁平封装IC(比如BGA)或包括有内部0V参考面的IC,通常都会有助于PCB的去耦合。一般地说,不应该使用IC插座,这是因为它们在IC和去耦电容之间所增加的电感会影响EMC目的的PCB去耦合效果。

简单形状的两维电流环路的电感可以很容易地使用标准方程求解。我们在这里之所以没有给出这些方程是因为使用免费的在线计算程序来进行和完成这类计算要快得多。实际应用中的真正去耦电容和IC电流环路通常都是三维结构,试图不使用场求解器程序要对它们所形成的复杂形状的电感进行计算是相当困难的。降低去耦电容和IC电流环路电感的方法以及有关分立式去耦电容内部电感的问题将在本章的后面部分给予逐个介绍。

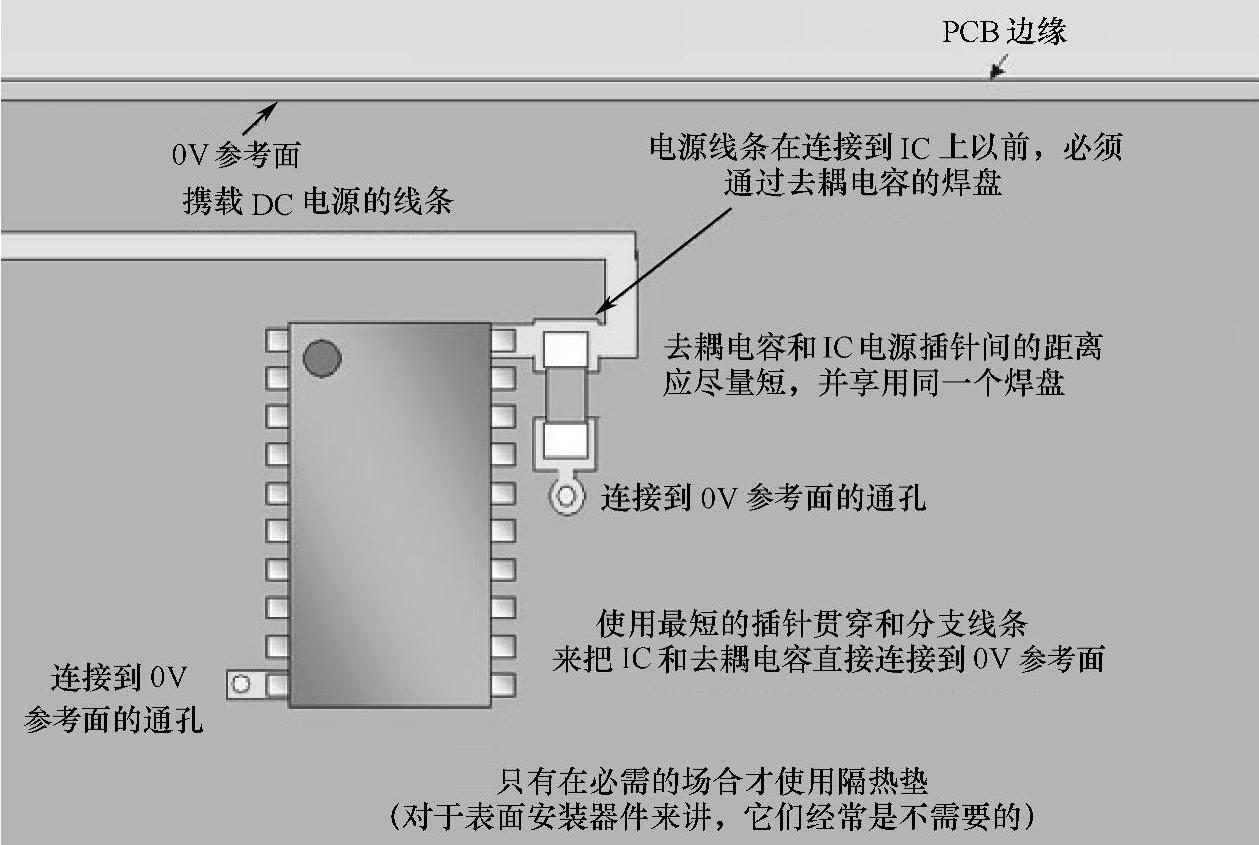

通过选择具有低值ESL的去耦电容和最小化它与IC(或元器件)间的互连接电感可以获得最小的去耦电容-IC电流环路电感。图2-4-4中所示的是在一个0V参考面和电流线条的情况下获得最小互连接电感的布局。

图2-4-3 我们所关心的去耦电容和IC电流环区域的例子

图2-4-4 仅具有一个0V参考面PCB的去耦合

(没有电源平面)

去耦电容的电源端与IC的电源插针享用同一个焊盘,使得IC和去耦电容之间形成的间隔距离最小。0V参考面应该设置在与安装元件的PCB表面层直接相邻的层次上,并且所有的元件都应该使用最短、最宽的线条与它相连接(只要是在现行技术可行的地方,都应使用焊盘中通孔)。0V参考面越是靠近PCB元件面,互连接电感就会降得越低。为了帮助去耦电容从电源总线中除去噪声,应该让来自电源的电流先流经并穿越去耦电容的焊盘后再接到IC上。

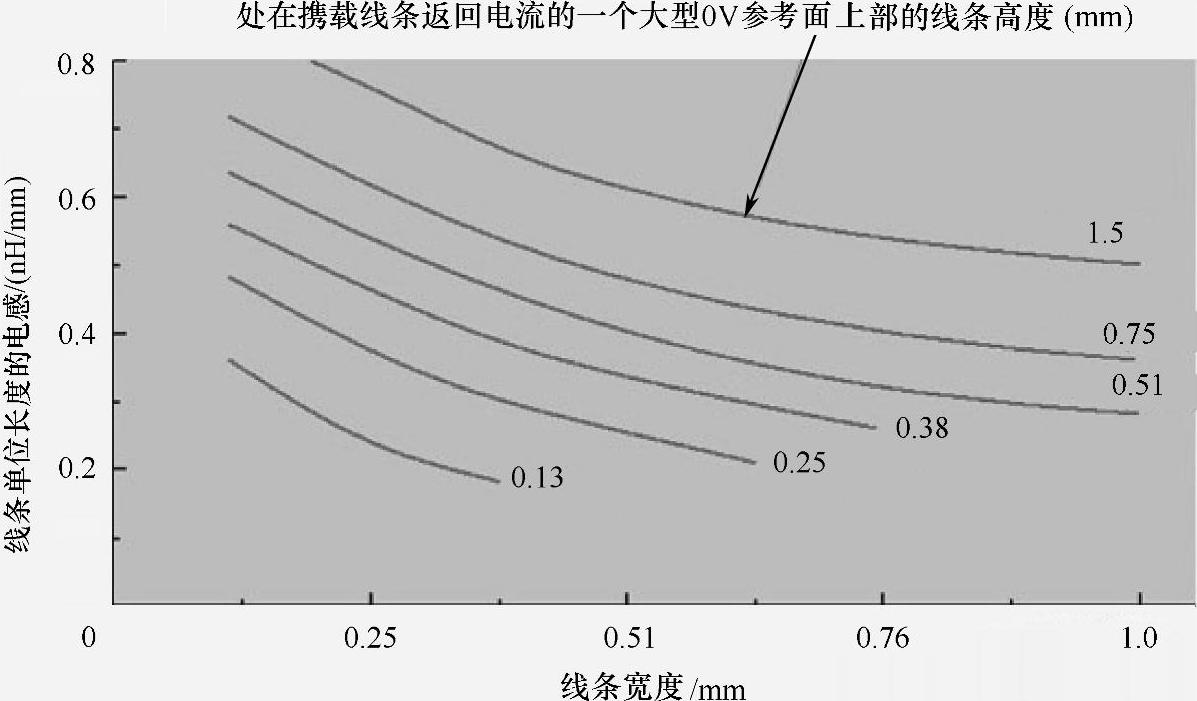

为了帮助在设计中对一个去耦电容进行布局,图2-4-5显示了在一个与0V参考面相邻的层面上走线的一个线条的局部电感是如何随着线条宽度和与平面的间距变化而变化的。(https://www.xing528.com)

图2-4-5 在FR4中PCB线条的局部电感

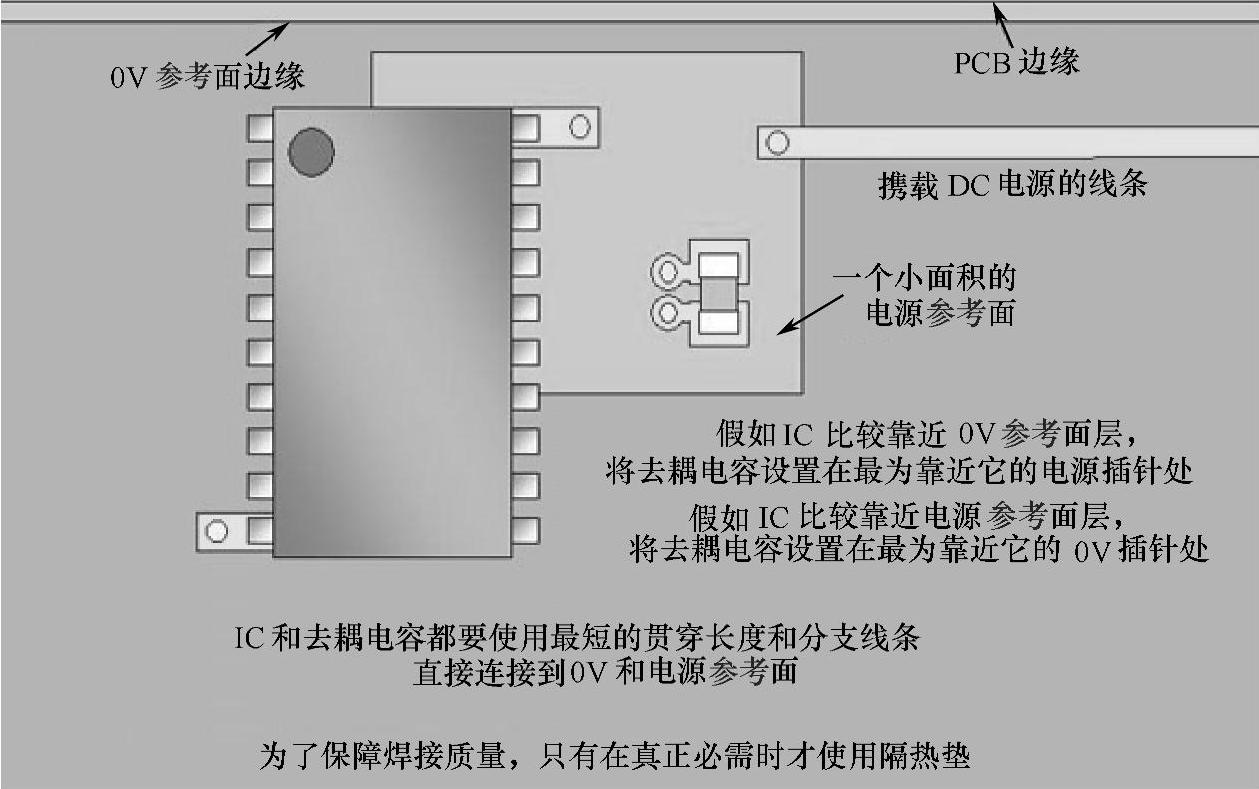

在由于某种原因去耦电容必须移至远离IC电源插针而无法享用同一个焊盘的场合,最好是在IC和去耦电容之间采用小面积的铜质面(一个小面积的电源平面)来代替线条,以使去耦电容的互连接电感最小化。这个做法示于图2-4-6中。正如前面所指出的,0V参考面必须设在与小面积电源平面的相邻层面上。两层面之间的较小层距将会降低互连接电感。

图2-4-6 当去耦电容无法与IC电源插针享用同一个焊盘时,要使去耦电容互连接电感最小化

在实际应用中,特别设定一个层面来作为0V参考面的原因是因为可以通过把发送和返回电流之间的互感最大化来使得去耦电容的互连接电感明显降低。这两个层面的层距的进一步缩小还会进一步增加它们间的互感,同时也就降低了整个环路的电感。这个问题还要在本章4.3节中做进一步的讨论。

为了帮助减小包括0V和电源参考面的PCB上的电流环路面积,还应采取如下措施:

1)要是被去耦合的IC最为靠近的层面是它的0V参考面层的话,它的去耦电容应该被设置在靠近它的电源插针处。

2)假如IC最靠近的是它的电源走线或电源参考面层面的话,它的去耦电容应被设置在靠近它的0V插针处。

为了进一步降低电源总线阻抗,有些制造厂商在它们的PCB内层已嵌入去耦电容。它们通常的做法是通过在铜质面积和小面积之间插入高介电常数的特制绝缘材料来形成平行板电容。其他的做法则是在PCB上铣削出一个椭圆形的孔,并在它的两端完成镀敷,然后在该椭圆形孔中焊入一个分立式去耦电容。但上述的两种技术不仅十分昂贵,而且问题很多。所以并不推荐在一般场合使用。

对任何电路类型来说(不仅仅是数字电路),降低去耦电容互连接所包括的面积(二维)或体积(三维)都是十分重要的。当对模拟电路进行去耦合时,去耦合的基本问题通常是稳定性、电源噪声的抑制和排除以及对EMI的抗扰度。在低频测试仪器和音频电路运算放大器上,通常应在每一个电源插针上设置一个100nF的多层瓷介去耦电容。在对高频和RF元器件去耦合时,则需要采用10nF或甚至仅为1nF的去耦电容来满足它们的稳定性要求。对于下面所要描写的那些电路可能需要采用类似的技术,以保持在整个宽频率范围内电源总线的低阻抗。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。