这一节的内容并不真正属于专门讨论PCB平面技术的本章的内容。但是它的内容很自然的由前面所描述的隔离环技术发展而来,所以把它包括在这里。

一个全屏蔽的PCB组件低成本快速获得产品的良好EMC性能提供了很大的帮助,并且还要感谢最新的低成本PCB技术方面的发展为此所做出的贡献。它们使得全屏蔽PCB组件的生产已不再是一件什么困难或高花费的事。而且当今的技术已允许整个PCB组件一次性自动完成焊接,而根本不需要任何后续手工装配工艺。

通过把隔离环线条进行广泛的延伸(请参阅上节),就可能使得它们形成屏蔽大部分PCB的顶部和底部0V参考面。我们将这些最大限度延伸的隔离环称之为隔离平面也许更为确切些。这样一来,使得可能引起EMC问题的仅剩下PCB上的元器件以及外部导线和电缆。

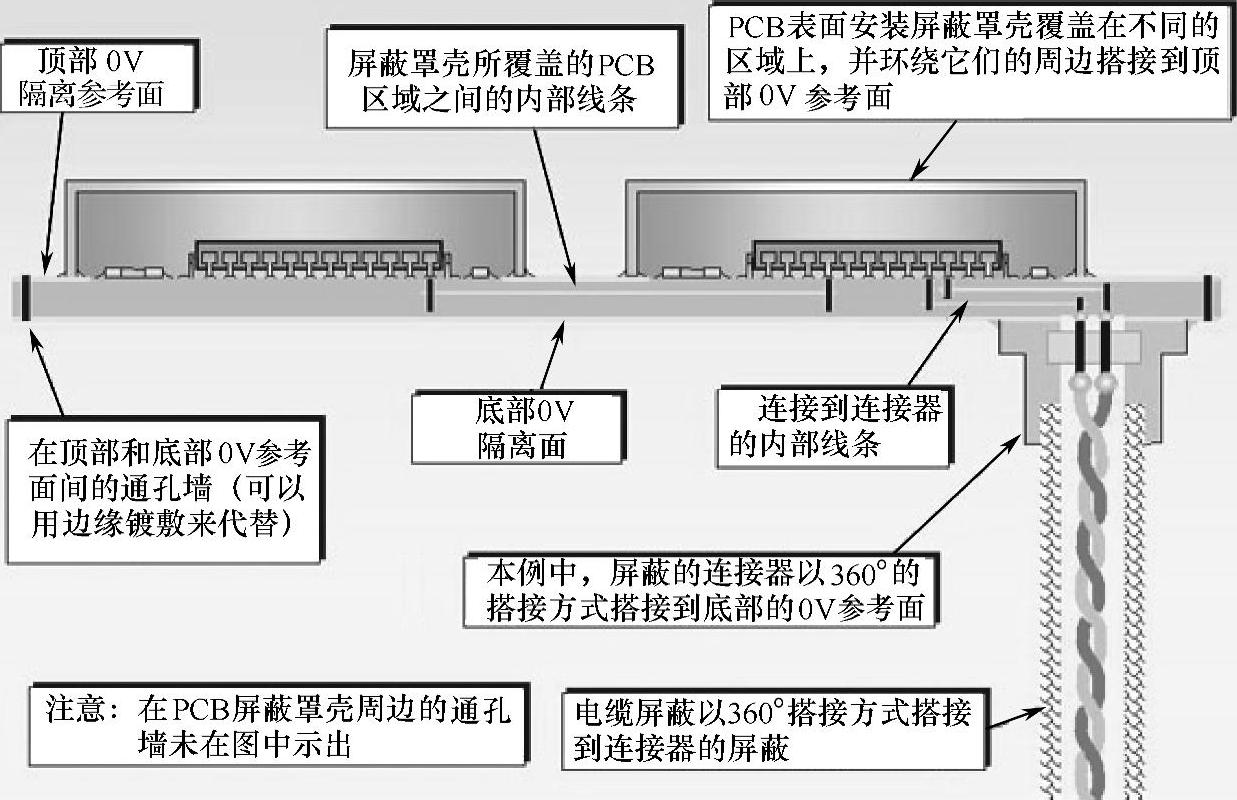

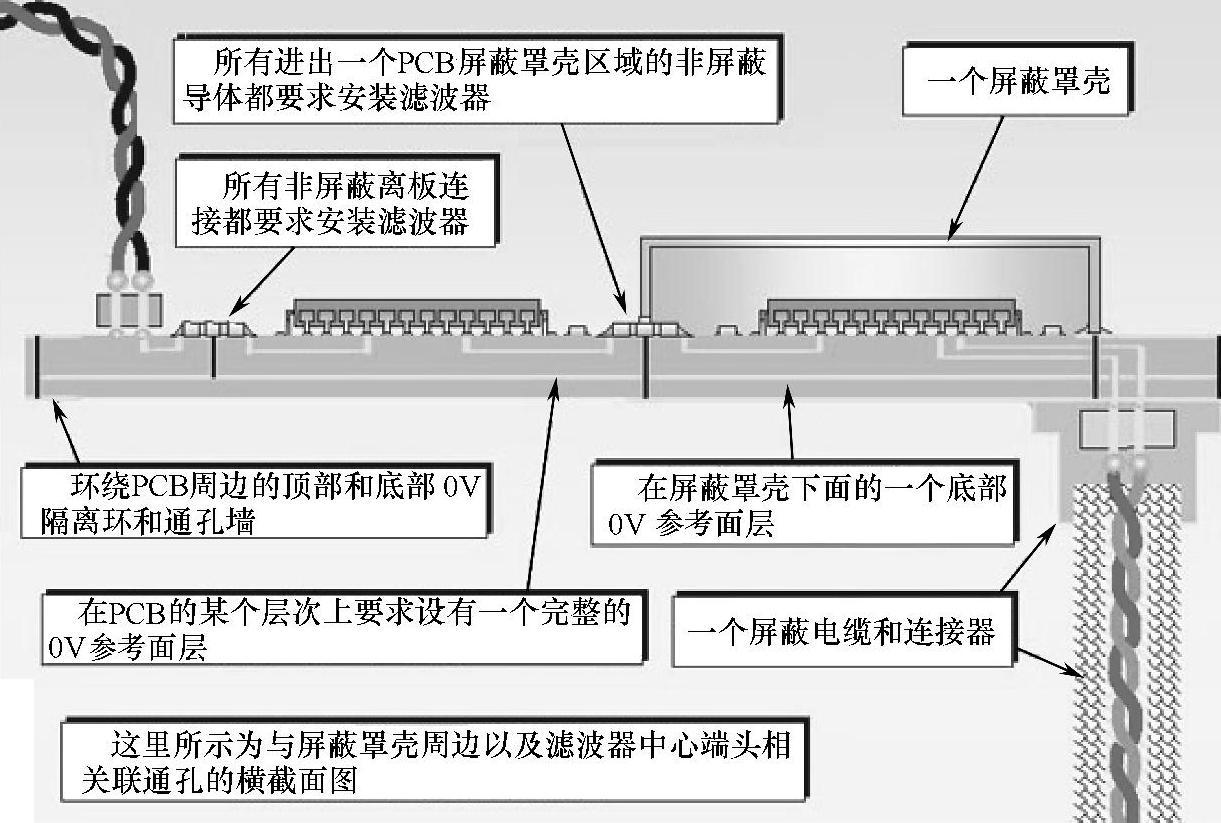

PCB安装型屏蔽罩壳以及进出一个0V参考面区域的非屏蔽电缆的滤波问题都已在本篇第1章中有所讨论。屏蔽电缆需要屏蔽良好的连接器与其配合使用,并且围绕着它们的周边搭接到0V参考面或PCB屏蔽罩壳的隔离壁上。将隔离平面与这些技术结合起来一起使用就可以形成全屏蔽PCB组件。

对PCB的顶部和底部层面上的0V参考面最大程度的延展还可以防止它们被用来布线。但是隔离平面将会在它们中形成缝隙。比如,在元件焊接到它们的焊盘以及它们的分支走线所要求的短线条和连接到内部布线层的插针引出线条都会在隔离平面上形成各式各样的缝隙。

当然,正如前面所讨论的,顶部隔离平面的所有区域都必须与底部隔离平面(和通孔壁或边缘镀敷)以及所有其他内部0V参考面通过分布在整个PCB面上的,间距为λ/10的通孔连接在一起(这里的λ仍是把PCB介质的介电常数k考虑在内的所关心的最高频率的波长),以防止谐振的发生。正如我们所知:通孔的间距越短越好。

图2-3-15和图2-3-16分别显示了通过使用前面所介绍的技术形成的全屏蔽和部分屏蔽PCB组件的例子。(https://www.xing528.com)

图2-3-15 一个带有电缆的全屏蔽PCB组件的例子

(不要求对离板电缆进行滤波)

图2-3-16 一个局部评比的PCB/电缆组件的例子

(所有未屏蔽PCB区域和未屏蔽电缆都要求进行滤波)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。