在一个PCB上采用两个或多个0V平面,使得在它的几个层面上同时使用好几个传输线线条成为可能(请参阅本篇第5章);或者使我们可以采用带状线传输线布线;或者使用铜质均衡来防止自动焊接期间PCB本身的弯曲变形。在PCB叠层中,经常把0V平面和电源平面设置为相邻的层面,以便向IC供电电源提供高频去耦合(请参阅本篇第4章)。但是,平面对也具有会形成空腔谐振这样的缺点。这一点与在本篇第2章中所描述的:在一个0V参考面和一个金属底板之间会形成空腔谐振的情况完全相同。当它们产生谐振时,它们不仅在有些位置上的阻抗可以远远大于正常值,并且在这些位置之间的电压差也要远远高于非谐振条件下的值。

给出一个矩形“平面对”的固有谐振频率所使用的公式与使用于单个矩形平面的,以及用于矩形平面—底板空腔谐振的相类似。但在“平面对”情况下,平面间的空腔填充是具有介电常数k的PCB基板,所以在空腔中电磁传播的速度要慢一些。也就是说,这使得与一个给定波长相关的频率要低一些。一个充填有介电常数k的介质的平面对的谐振频率可以由下式给出:

这里:f为平面对的谐振频率,单位为MHz;

L和W为平面对的长度和宽度,单位为m;

l和m为整数(0,1,2,3等),它们与各个不同的谐振模数相对应。

通常我们最为关心的仅是第一个(最低的一个)谐振频率。对于FR4材料而言(k=4.0),可以很容易从f=75/D求出。这里的D是平面的最长对角线(若D以m为单位,所求得的谐振频率单位为MHz;若D以mm为单位,所求得的谐振频率单位为GHz)。

对于那些非简单形状的非矩形平面而言,决定它们谐振频率的最简易办法就是使用计算机模拟(仿真)场求解器,或者对一个测试用PCB进行实际测量。但是它们的最低谐振频率仍然可以很容易地使用75/D MHz来表达。这里仍然假定使用k=4.0的FR4材料,并且平面的最大尺度仍然以m为单位。

若从EMC考虑出发,为了防止在所关心的频率范围内空腔谐振的发生,所有的0V参考面(包括所有小的或分割的平面面积)都应该通过通孔相互连接一起。而它们的间隔距离都不应大于所关心的最高频率的λ/10,并还要把PCB的介电常数k考虑在内。因此,倘若希望防止在频率高到1GHz时一个“平面对”的空腔谐振,在整个平面面积上平面连接通孔的间距不应大于15mm。通孔间的间距越短,所给出的EMC性能就越好。

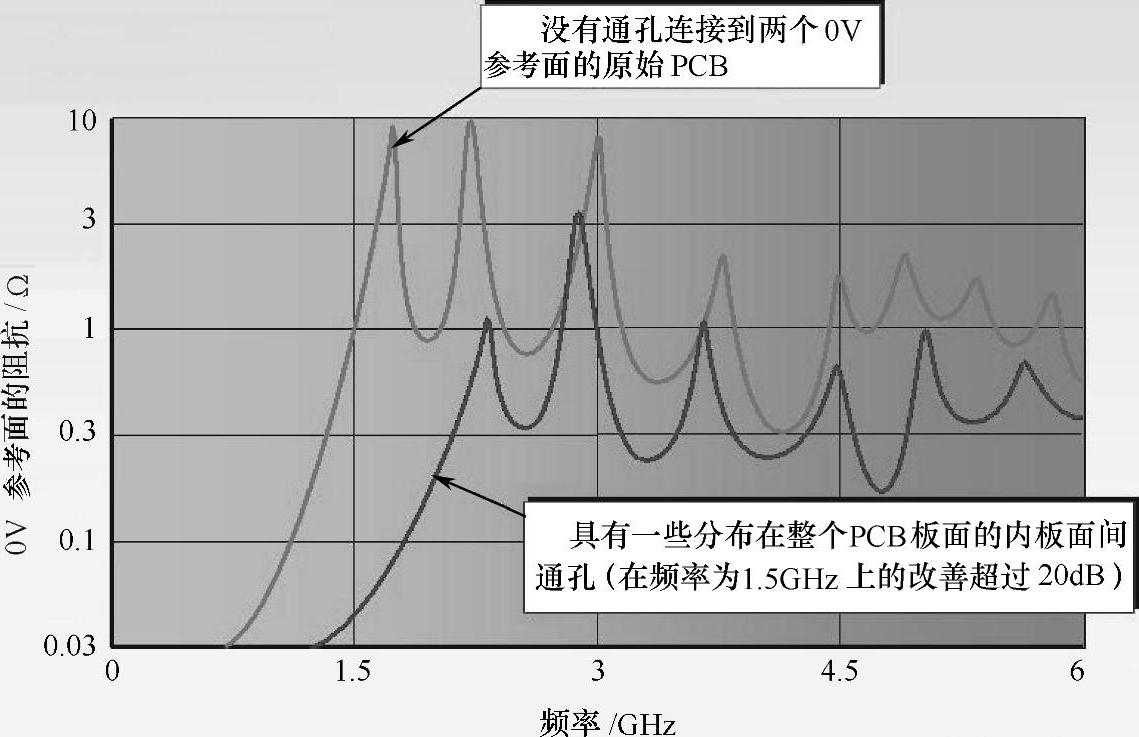

图2-3-10 在一个参考面对中空腔谐振的例子

(使一个小型PCB的顶部和底部层面构成0V参考面的情况)(https://www.xing528.com)

图2-3-10所示为对一个小型测试用PCB的测试结果。它的顶部和底部都专门留作为完整的0V参考面。它并不是一个真正的功能性PCB。只是用它来测试使用通孔把0V参考面连接在一起的做法会对空腔谐振频率产生什么样的影响。图中显示,在设置了附加的一些参考面互连接通孔后,大约为2GHz频率上的第一个谐振上移到了更高的频率上,并且在1.5GHz频率上的参考面阻抗下降了20dB。这明确地告诉我们:在高到这个频率上的EMC性能得以显著地改善。

通孔本身的局部电感(每毫米长度,大约为1nH)限制了它们在0V参考面之间形成理想的短路。特别是要考虑到现代PCB中所使用的频率往往是非常高频率的情况。例如,一个1.5mm的通孔在1GHz频率时的阻抗大约为10Ω。将这个阻抗值与在1GHz频率上的一个实心0V参考面的远离谐振频率下的0.03Ω,以及它处在谐振峰值时的10Ω阻抗相对照,读者将会对它们各自的阻抗值得出一个基本的数量级概念。

显然,我们不能把0V/电源平面对通过通孔把它们缝合在一起。我们代替使用的是经常称之为“退耦电容”的去耦合电容器。可惜的是,分列式去耦电容在500MHz频率以上时的效果会受到严重限制。这是由于它们的内部自身电感以及组成它们的电流环路中所存在的焊盘、线条以及把它们连接到0V和电源平面的通孔,再加上它们所包括的面积的电感所造成的。

然而,我们可以在PCB的叠层中把0V和电源平面设置得尽可能靠近些,以此来降低围绕它们边缘的边缘场。这类边缘场是引起一个“平面对”发射的主要原因。一般地说,在其他条件都完全相同的情况下,把0V/电源平面间的间距减半,发射也可以降低一半。况且,减小0V/电源平面之间的间距还可以降低一个给定电路的发射(或改善抗扰度)。这一点还要在本篇第4章中做进一步的讨论。环绕一个“平面对”的边缘场有时也称之为“侧面射击”发射。

将0V/电源“平面对”的间距设置为0.05mm(2‰in)或更靠近的结果之一是它们在谐振频率上的阻抗峰值幅度有所下降。换一种提法就是空腔的“品质因数(Q)”下降了。在THP PCB中,通过使用远远薄于正常使用的介质层有可能把品质因数降低至1。也就是说,在这一点上(Q=1),由平面所形成的空腔,不论它是什么尺寸或形状根本就不会产生谐振。在本篇第4章中将就这个问题做更为详尽地讨论。

由一个“平面对”形成的空腔具有高Q的原因之一(在它们的间距大于1.5mm的场合)是因为在空腔中几乎没有任何损耗来提供衰减(阻尼)。事实上,真正PCB的谐振峰值通常都会有比简单计算或测试板所给出的谐振峰值要低一些。这是因为板面上所存在的电子元件的损耗会形成阻尼的缘故。经过慎重考虑的设计,可以通过使用电阻来替代某些平面间通孔的方法来增加阻尼。这些电阻的阻值通常大约都在2~10Ω之间。在0V/电源“平面对”的情况下,还可以采用为有些去耦电容配置串联电阻的办法。据知,有些元件制造厂商已经生产有特别用来阻尼0V/电源平面对谐振的,包括一个串联电阻在内的电容器产品。

通常仅需要几个分布在整个PCB上的阻尼电阻就能提供足够的阻尼。为了产生最好的阻尼效果,它们应该被设置在产生谐振的“热点”上。在这些热点上,平面间的RF电压差有着最大值。对于那些形状简单的平面,虽然由于元器件的存在可以改变“热点”的实际位置,但我们仍有可能预测在哪些位置上可能产生最低谐振频率的“热点”。但对大多数的PCB来说,可能要求使用计算机模拟(仿真)或实验来找出阻尼电阻的最佳设置位置。

将铁氧体吸波材料制成颗粒掺入PCB的介质中也可以帮助衰减谐振的峰值。这样做还可能会以其他方式来降低发射。但目前这还不是一个普及的技术。因为铁氧体颗粒的存在会增加为PCB冲孔或钻孔工具的磨损程度。也许等到激光打孔HDI的PCB技术普及化后,掺有铁氧体的基板将会变得更有吸引力。

另一个用来降低空腔谐振的方法是仔细考虑设计平面的形状。虽然这样做不会对最低谐振频率产生任何影响(因为它主要是取决于平面的最长尺度)。但是对某些较高频率的谐振会有一些有益的影响。

在一个矩形平面的长度(L)是它的宽度(W)的整数或简单倍数情况下,比如L∶W=1、1.5、2,那么在某些频率上,它的长度和宽度方向的谐振频率将会是一致的。从而会引起具有比通常较高Q值的峰值(更为强烈的谐振)。墨菲法则告诉我们:若就在为了获得产品的最佳性能而更换并采用最新型号的微处理器以前改变时钟频率往往会造成比通常要高的谐振。这很可能是因为它的谐振频率正好与一个无法滤去的重要时钟谐波相一致所引起的。它不仅将会带来很高的花费以及非常耗时的设计修改,甚至会造成在不允许任何延迟的情况下,却引起无法通过EMC符合性测试。

因此,最好的办法就是避免使用正方形平面和简单的L/W比。由于存在有无数个无理数,我们推荐使用“黄金分割”:1.618…等(有时用它的近似值1.62)。原因之一是因为它会给出一个令人心悦的外表(正如文艺复兴时代的艺术家和古希腊建筑师们所知道的)。细长条状的平面应尽量避免(即L∶W比永远都不应该大于3或小于0.33)。这样做还会对形成非平行边缘平面提供一些帮助。并避免形成如矩形或圆形这类简单的普通形状。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。