PCB平面上任何缝隙和孔洞的存在对EMC来说都是有害的。这是因为它们的存在必然会增加阻抗和阻止RF返回电流的自由流通。在平面上的缝隙和孔洞(或边缘)离开线条足够远的场合(请参阅上节),从EMC角度出发,对所有PCB布局设计的总的指导思想是,PCB上不允许有任何最大尺度大于所关心的最高频率的波长(λ)的十分之一(λ/10)的缝隙或孔洞存在(即,最高频率因为EMC而受到了限制)。

我们知道,在空气或真空中,λ=300/f(这里,在λ的单位是米(m)时,频率f的单位为MHz)。但假如缝隙或孔洞中充满的不是空气或不是处于真空状态,那么充填材料的介电常数k(=相对介电常数)将会使充填材料中传播信号的波长变短:

例如,平面缝隙或孔洞的充填材料为PCB基板材料(除特别指出,总是指FR4材料),它在频率为1MHz以上时的k=4.0。这意味着,它的波长正好是在空气或真空中的一半:λ=150/f(λ的单位为m,f的单位为MHz)。

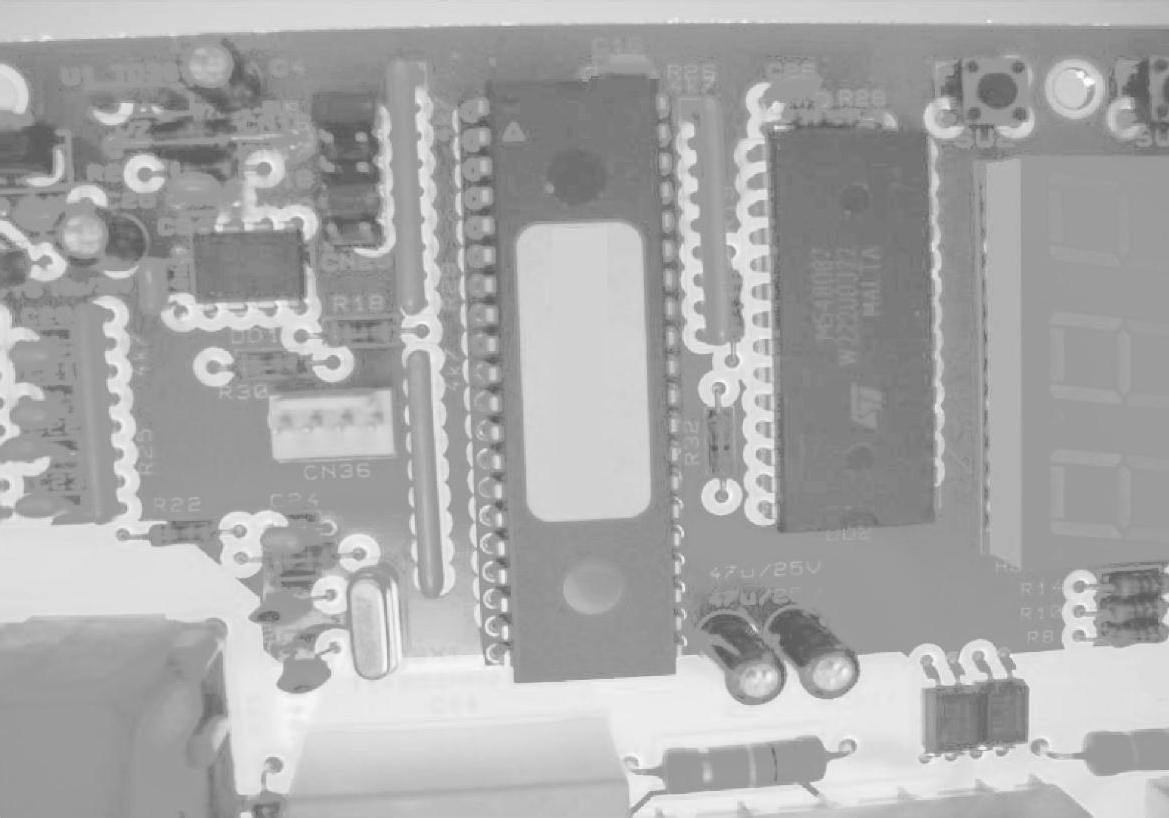

由于在每个通孔周围要求有净空孔(阻焊盘)的存在,现代PCB的高密度贯穿孔镀敷制造技术(THP),在所有平面上都会形成大量的贯穿孔。这样高密度的平面钻孔的存在会大大增加平面阻抗,从而大大降低了使用平面所获得的效能。

在改善EMC性能,而又不会严重影响产品产量的前提下,阻焊盘应该设计得尽可能地小。然而,有些制造厂商使用成本低廉的PCB供应商的产品,它们的精度与当今使用的典型PCB的质量要低得多,特别是多层板的层间对位更是很大的问题。为此,这些PCB会采用很大的阻焊盘才能保持成本不致过高。在这类情况下,使用高质量PCB供应商的产品,不仅在整体上会大大提高性价比,同时PCB上的阻焊盘的直径可以小到1mm的水平上。

在实际应用中,有一些专业PCB制造厂商可以供应阻焊盘直径小于1mm的PCB。但是使用高密度互连接技术(HDI)生产的PCB可以大大消除平面的阻焊盘钻孔,并使平面给出它的最佳EMC性能。

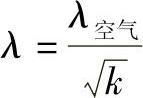

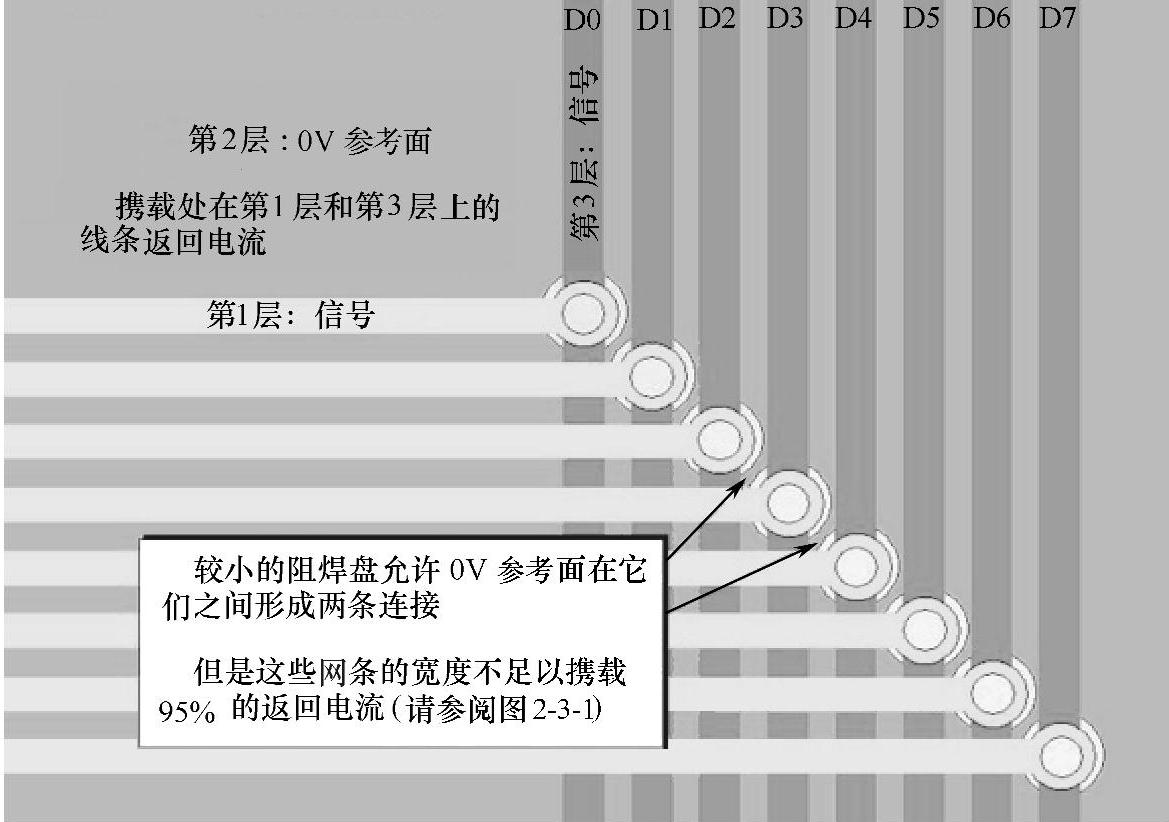

有关密集THP PCB布局的另一个重要问题是阻焊盘不应相互合并在一起,在平面上形成更大的缝隙和槽。这种情况在通孔被安置在过于靠近时经常会发生。并且当使用计算机辅助设计(CAD)系统来绘制平面时,将输入的最小半径定义的太大时也常会出现这种情况。甚至在PCB制造厂商对一个平面层原始布局过度曝光时也会出现这种情况。图2-3-2显示了出现阻焊盘合并错误的几个例子。

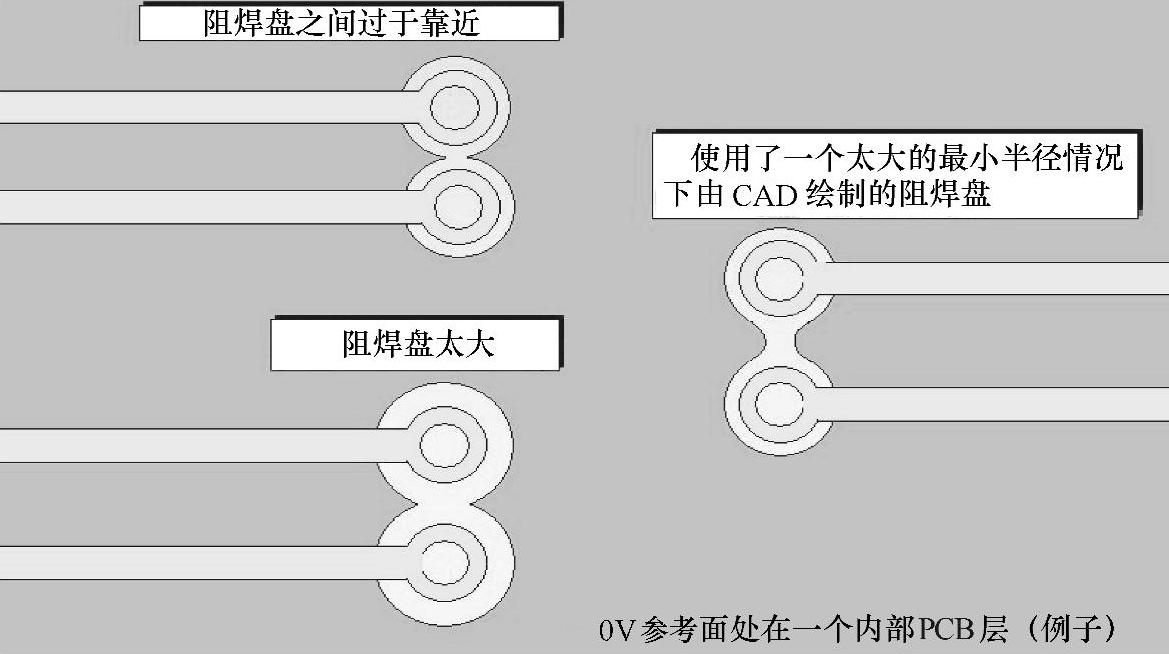

图2-3-3显示了如何不在一个PCB上形成多个平面的例子。假如使用的微处理器(CPU)是在上世纪80年代初购置(生产)的话,则PCB可能仍然会给出可以接受的EMC性能。但是在这个新世纪中购置(生产)的则绝对不行(即便它们具有相同的类型和型号)。

通过审查布局草图就可以很容易地发现通孔之间是否设置得过于靠近,并应立即予以修改。使用CAD绘制平面的规则往往是先把它们设置为一个较大的最小半径以缩短计算机的处理时间,并帮助提高设计效率。这样的做法是完全可以接受的,其前提是只要在最后检查布局方案时不要忘记改用一个较小的半径值,以防止阻焊盘出现归并现象。

为了避免还要对那些过度曝光的平面层光模进行重合对位处理,不应该再选用由这些制造厂商供应的PCB。因为他们的公司信誉程度明显是有缺陷的。经常还会发现这样的情况:一个PCB设计的早期发送的产品所使用的阻焊盘直径正如设计所要求的一样,但是当产品按部就班进行投产期间,有些供应商为了提高他们自身产品的产量会增大产品阻焊盘。因此,有必要对PCB裸板在进仓时进行检查。其中要包括对阻焊盘直径的检查。

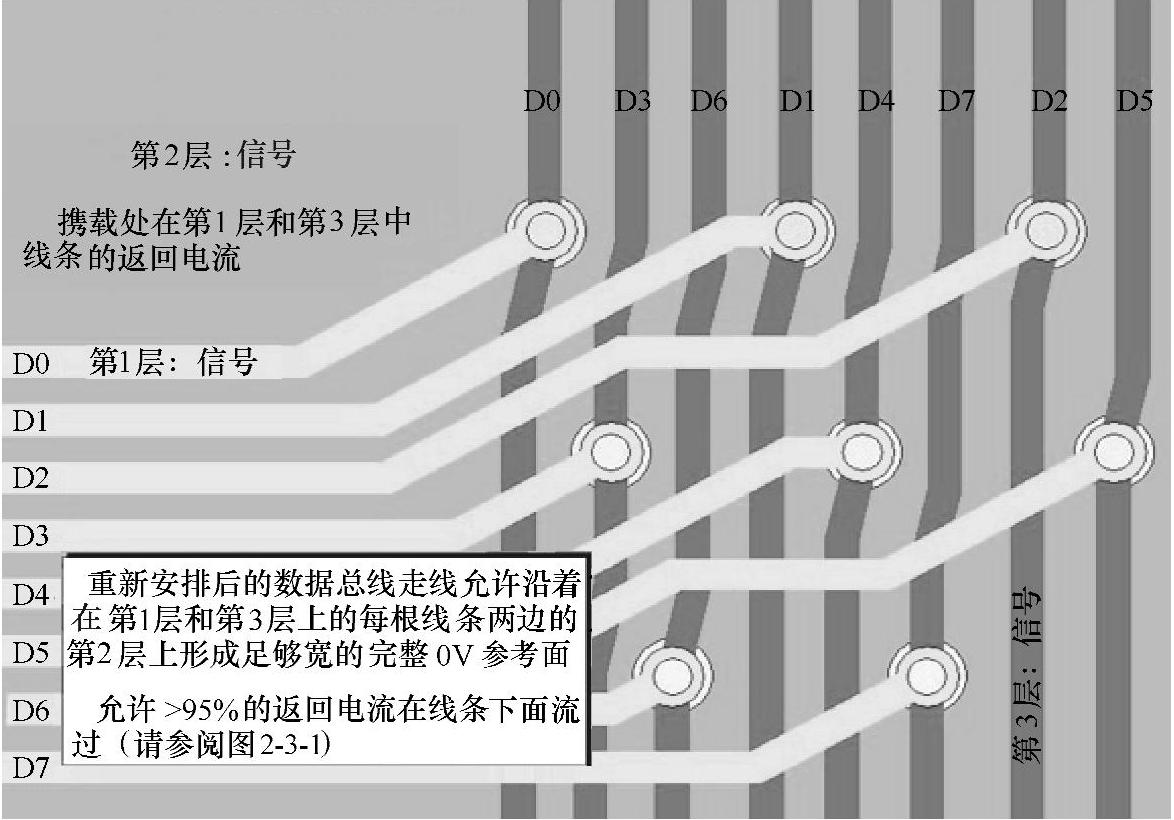

当一个PCB具有大量的贯穿孔和通孔时,特别要小心防止它们的阻焊盘出现合并或侵占线条的电流返回通路情况的出现(请参阅图2-3-2)。图2-3-4、图2-3-5、图2-3-6分别显示了如何通过对布局的仔细设计来克服这些问题。

大多数PCB设计工程师都应该有能力进一步改善图2-3-6的布局设计,但该图至少图示了改善性能的正确出发点。

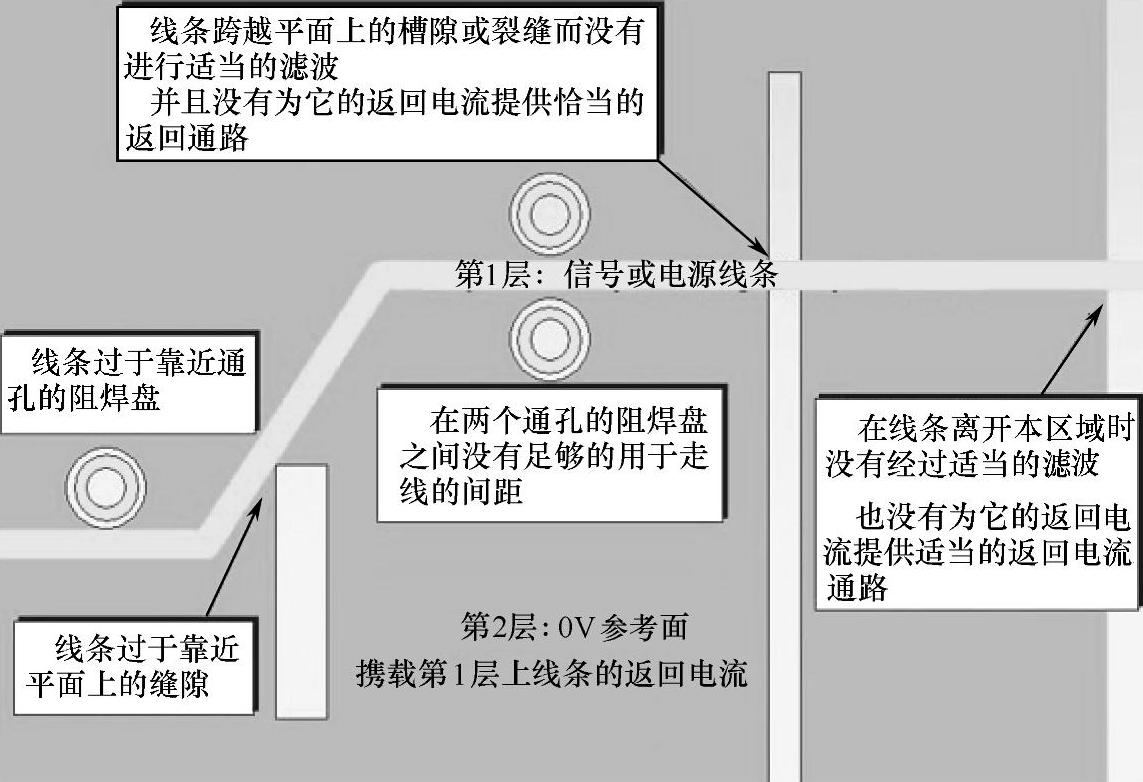

图2-3-7显示了当线条的布线过于靠近阻焊盘、平面裂缝或边沿时的一些常见错误。所以增加了与这些线条有关的返回电流阻抗,从而也使得EMC性能受到影响。请注意,从信号完整性的角度出发,在一个返回电流通路中阻抗的增加与在发送通路中增加阻抗一样,同样会造成信号波形的恶化(比如在信号通路中)。(https://www.xing528.com)

图2-3-2 阻焊盘错误归并的例子

图2-3-3 如何不在PCB上形成平面的例子

图2-3-4 一个设计很差的0V参考面的例子

图2-3-5 一个改进了的0V参考面设计的例子

平面层使用的是与信号线条相同的薄铜箔。因此,当应用在重载DC或低频电流的场合,它们的电阻有时会引起一些问题。PCB制造厂商能够将标准厚度的1/2oz[1]①或1oz的箔片镀敷至8oz的厚度,以降低平面电阻。有些PCB制造厂商还能够以叠压的方式把金属薄层压入到一个PCB中来作为散热器使用(有时称之为热包层PCB)。在它们的技术工艺允许镀敷的贯穿孔和通孔与金属箔片之间形成可靠电气连接的情况下,平面电阻会有明显的下降。把PCB的0V参考面搭接到它的底板上也有助于平面电阻的降低。这种技术的使用,请有兴趣的读者参阅相关文献。

图2-3-6 一个相当不错的0V参考面设计的例子

图2-3-7 常见线条布线错误的几个例子

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。