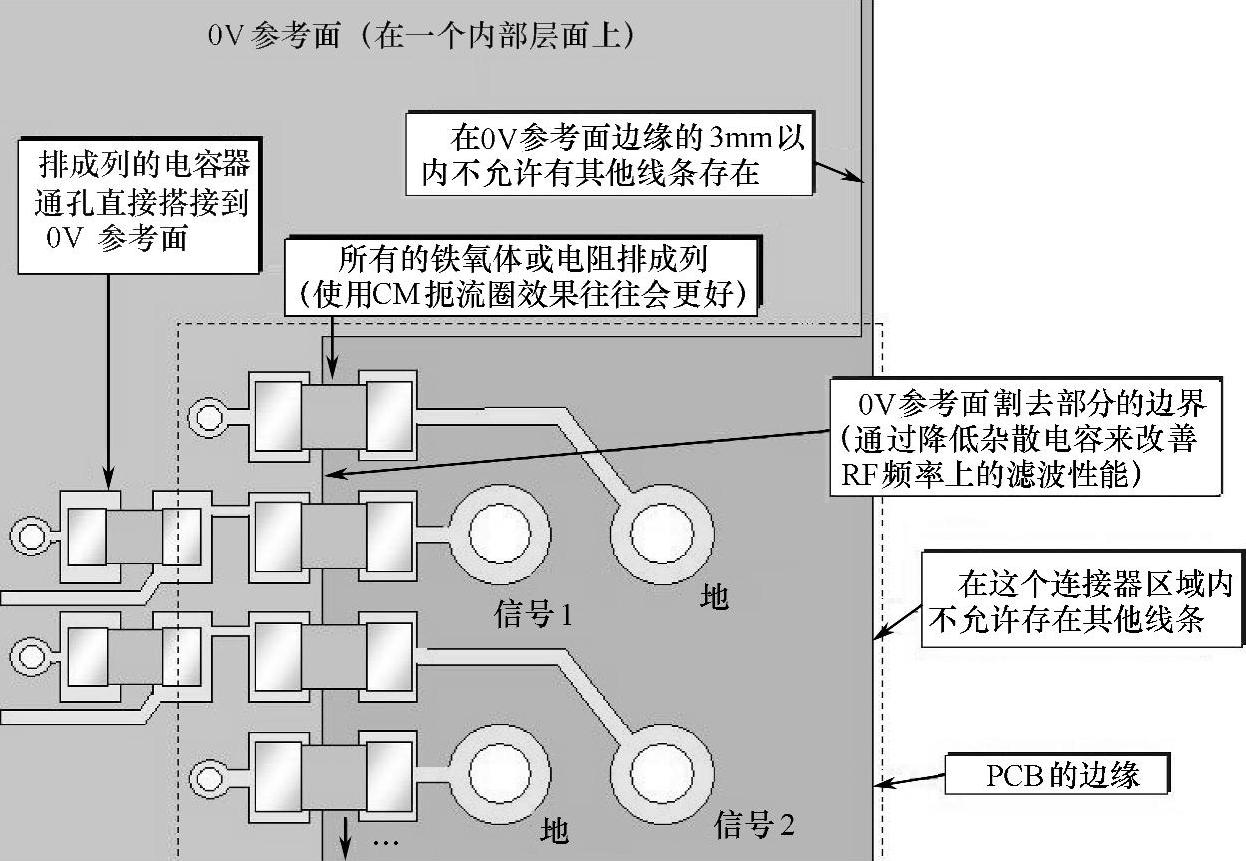

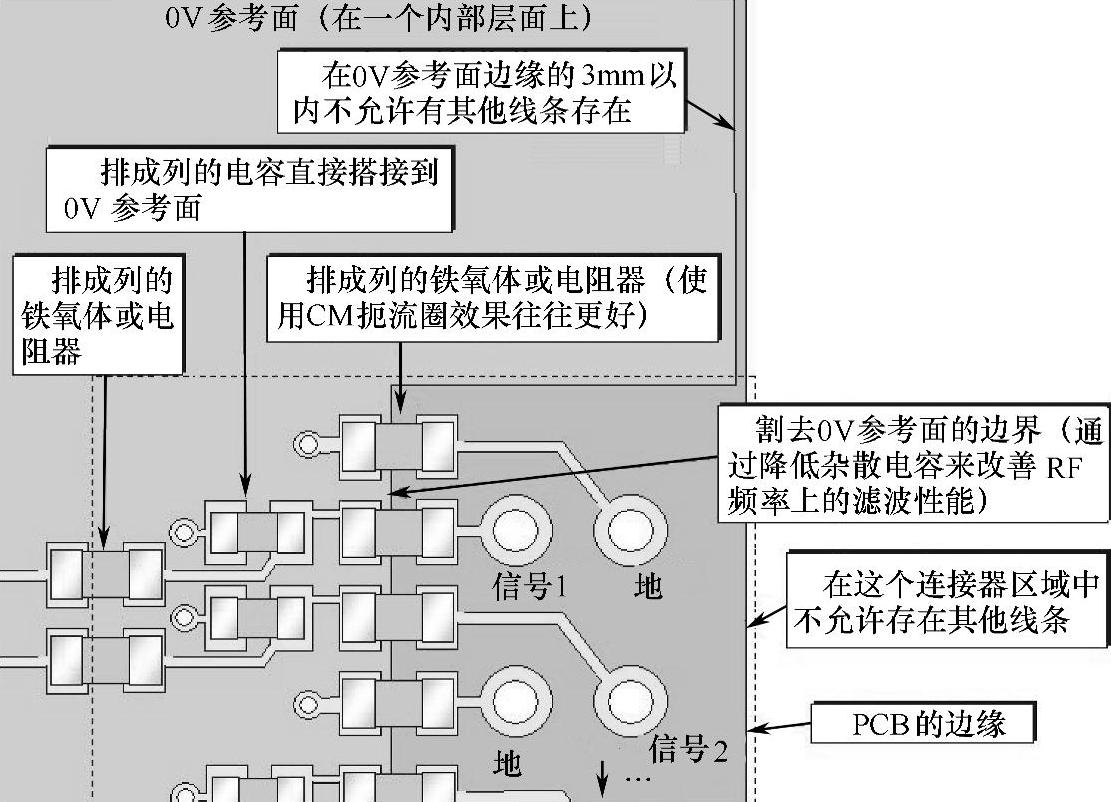

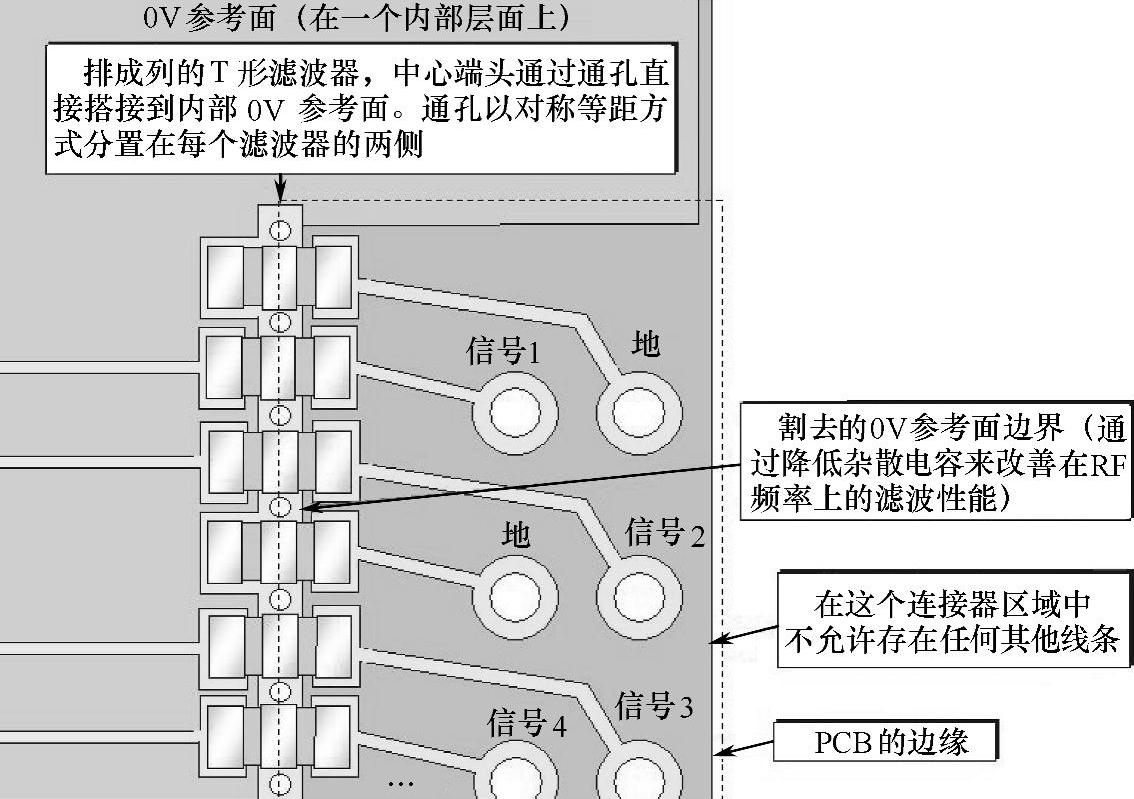

一般地说,在相互连接设备的所有组成部件中,没有采用搭接良好的金属平板(正如在典型的舰艇和潜水器使用的)作为参考的场合,对一个非屏蔽离板连接器/电缆进行滤波的最佳类型是使用一个串联电阻或软铁氧体抑制器来作为它离板前的最后元器件。作为一个例子,图2-1-16中所示的就是在一个PCB布局中,所使用的价格低廉的两端电容型RC或LC完成滤波的一个非屏蔽离板连接器。可以使用CM扼流圈来代替电阻和铁氧体的多级衰减布局没有在图中显示出来。

图2-1-16 一个使用RC或LC滤波的未屏蔽离板连接器布局的例子

为了简明起见,将单级低功率和信号PCB滤波器布局的设计要点罗列如下:

(1)把衰减器元件排列成行

图2-1-16显示了如何将连接到离板连接器/电缆的铁氧体排列成整齐的一排。在频率超过100MHz以上时,这种仔细的布局方式对最佳化这些器件的衰减性能是至关重要的。由于一些现代新式连接器连接密度甚高,为了节省空间,人们常常想把电阻或铁氧体按交错排列的方式布置。但请千万不要这样做!铁氧体的交错排列布局会引起在它们的已滤波和未滤波端头之间杂散耦合电容的增加。虽然看起来附加的电容出现的不会很大,但它们已足以可能使铁氧体完全丧失滤波作用。

假如无法获得完全整齐排列的电阻或铁氧体布局(比如没有足够的空间等),则要么想办法选用体积较小的铁氧体元件(尺寸较小的0402铁氧体元件已逐渐普及化),或者使用集总铁氧体阵列。另外可供选用的方案是将铁氧体元件同时安排在PCB的两个表面层上(顶层和底层)。这类布局必须做到的是,顶层铁氧体的排列必须与底部的排列在几何上完全对准对齐。

在需要使用一个CM扼流圈的场合,把串联电阻和铁氧体正确排列成行,在帮助正确设置这样一个CM扼流圈方面也是必要的。重要的是,一定要保持一个扼流圈的输入端和输出端连接分离得越远越好。RC或LC滤波器中的电容也要以整齐排列的方式布置在电阻或铁氧体排行的后面(请参阅图2-1-16)。而且这些电容器的0V端头必须使用尽可能短而粗的线条通过通孔连接到完整实心的内部0V参考面层(这样做的目的是使它们的串联电感最小化和改善电容器的高频性能)。在滤波器电容的端头推荐使用“焊盘中通孔”技术。这一点在使用微化孔PCB技术(将在本篇第6章“包括微化孔在内的布线和层叠技术”中加以讨论)或波峰焊PCB技术时很容易做到。通常来说,焊盘中通孔技术不能用于回流焊技术。但有些PCB制造厂商似乎能够做到这一点。而且在不仅不会增加成本,效果也相当不错。

(2)对离板“地导体”(GND)进行滤波

在连接器/电缆中的“地”(GND)连接中也设置有用于安装铁氧体的焊盘。这是因为在一个离板0V连接也设有一个与信号通路中安装相同的铁氧体同样会有助于改善滤波性能。因此这些焊盘的设置,可以在需要时帮助铁氧体的安装。假如要求使用CM扼流圈的话,则必须要使所有的路由离板导体同时穿越它(至少在具有若干个CM扼流圈的情况下,每个信号加上它的指定返回导体应是如此)。因此,在适当的位置上提供一些用于GND信号的焊盘将会有所帮助。

(3)减小0V参考面

图2-1-16显示出在部分滤波器区域割去了0V参考面的情况。事实上,割去的部分最远也仅达到电阻、铁氧体或CM扼流圈端子的“电路边”的交界处。这样做是因为0V参考面接近于这些元件处于连接器区域的连接器/电缆端子会增加它们的寄生电容以及在高频条件下,会降低它们的滤波性能的缘故。割去如图2-1-16所示部分的0V参考面还会帮助防止外部导体中的噪声与PCB的0V参考面之间出现不希望的耦合。但在有些情况下,则要求不要割去该部分的0V参考面,即便是这样做(保留这部分的0V参考面)会在某种程度上牺牲串联电阻、铁氧体或CM扼流圈的滤波性能。关于这一点将在本章的第7节“离板互连接的设置”中加以讨论。

在这一节中,所有的例子都包括有串联电阻,铁氧体或CM扼流圈,并将它们设置在连接器/电缆前面来作为最后的滤波器元件。直接将连接器/电缆通过一个电容连接到0V参考面的其他类型的滤波器(比如,π形滤波器),则不应使用具有割去部分0V参考面的连接器/电缆区域。代替的是,0V参考面应一直延伸到PCB的边缘,并沿着连接器/电缆的连接形成网状。这个问题还会在本篇第3章“0V参考面和电源参考面”中作进一步讨论。

(4)连接器区域中不应有其他线条或元件

在图2-1-16所示的PCB上的虚线区域称之为“连接器区域”。这个指定区域的唯一用途就是用来对离板(外部)连接器进行滤波。如果布局设计不当,这个区域中的滤波器元件和线条之间的寄生电容和互感能够使为离板连接器/电缆提供的滤波作用全部抵消。因此,在多层PCB任何层次上的这个区域中都不允许有任何其他线条、元件或电源参考面存在。即便是在上面曾提及的0V参考面在该区域中没有被割去的情况下,也必须如此。

(5)连接器区域的屏蔽

假如发现屏蔽是必须的话,“连接器区域”应该由一个屏蔽罩壳所覆盖。这个屏蔽罩壳将需要根据前面“PCB屏蔽罩壳”一节所讨论的方法进行设计。由于该屏蔽罩壳是用于对一个离板连接器/电缆滤波器区域进行隔离的,所以它不可避免的将会有一个用于安装进出的连接器或电缆的非完整屏蔽面。

在使用由一个金属材料(或金属镀敷塑料)制成的连接器面板的场合,连接器区域的屏蔽罩壳切开的一面(安装连接器面板的一面)必须完成与连接器面板内部表面的多点电气搭接。通常最好是采用适当类型的导电“EMC密封衬垫”(这样做的好处是,成本一般都会较低)来完成这些搭接。即便仅希望给PCB罩上一个普通的,非屏蔽用途的塑料盒的情况。在EMC设计考虑时,仍应考虑采用镀有金属表面或金属表面喷涂的塑料来作为罩壳材料,或者可以考虑在盒的内表面敷上一层金属箔,然后像本篇第2章“PCB与底板的搭接”中所介绍的方法与PCB的完整内部0V参考面完成电气搭接。

(6)使用屏蔽来改善滤波器性能

假如一个PCB屏蔽罩壳的隔离壁是与0V参考面的几何截止边缘对齐的话,在图2-1-16中所示的串联电阻、铁氧体或CM扼流圈的滤波性能将会得以改善。这样做的另外一个附加好处是,串联电阻和铁氧体可以通过为它们开设的“鼠洞”伸出。这类屏蔽罩壳的设计原则应根据本篇的第1.2和第1.3小节中的讨论进行。

在一个屏蔽罩壳已经覆盖整个连接器区域的场合,该屏蔽罩壳还应该包括有一个内部的隔离壁将它的内部分隔成两个部分。这个隔离壁在几何位置上应该与0V参考面的几何截止边缘对齐,并且在它的上面应该开有为电阻和铁氧体伸出用的“鼠洞”。

在屏蔽罩壳没有完全覆盖整个连接器区域的场合,那么用来改善串联电阻或铁氧体滤波性能所使用的屏蔽壁应该是包括滤波器电路在内“PCB一边”的屏蔽罩壳的一部分(也可能覆盖其他的电路区域),或者是正如上述的搭接到连接器面板的一个连接器面板/电缆屏蔽罩壳的一部分。

(https://www.xing528.com)

(https://www.xing528.com)

图2-1-17 使用T形滤波器的一个未屏蔽离板连接器布局的例子

(7)T形滤波器

图2-1-17所示为,如何将上面图2-1-16所图示的细节,即“设计规则”应用到一个T形滤波器。采用这种滤波器类型的连接器区域至少要延伸到将滤波器电路一侧上的串联电阻和铁氧体几何尺寸的一半加以覆盖。用于改善滤波器性能,开有“鼠洞”的屏蔽罩壳的隔离壁既可以沿着串联电阻,铁氧体或CM扼流圈排列的中心线安装;也可以沿着电容器排列的中部安装(请参阅图2-1-17)。倘若能将屏蔽罩壳的隔离壁沿着T形滤波器的任何两个,或者甚至全部三个滤波元器件排列都进行安装,滤波器的性能将会更好。假如仅使用一个这样的“鼠洞”的情况下,该“鼠洞”的开设位置最好是沿着电容器的排列位置。

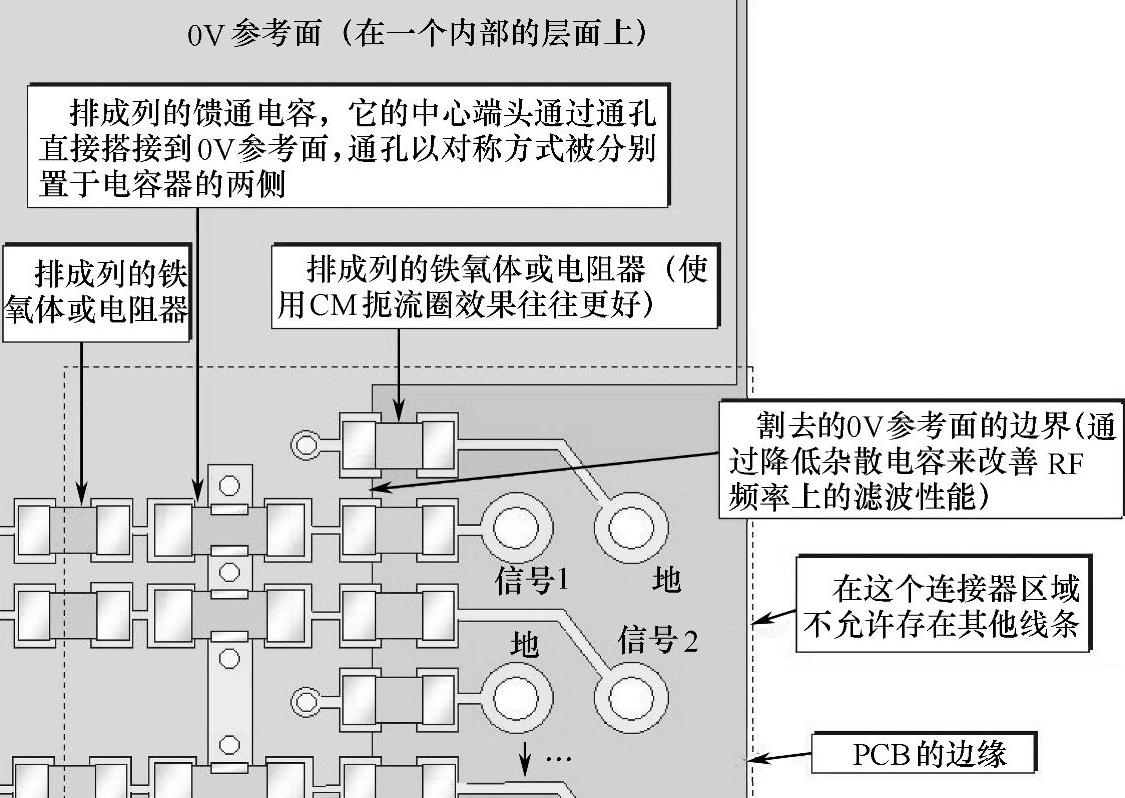

图2-1-18所示是图2-1-17中T形滤波器的一种变化形式。此图中所使用的是在频率为300MHz以上时可以改善滤波性能的三端电容。在任何使用三端滤波器的场合,都要求一个0V隔离线条存在,以将滤波器的中心端子与它焊接在一起。同时,还总要求有两个以相等间隔分布在每个滤波元件两侧的0V通孔以改善它们的隔离性能。用于改善滤波器性能的开有“鼠洞”的屏蔽罩壳的设置要按照图2-1-17的设计准则进行。但一个与电容器对齐的隔离壁应该沿着它们的0V隔离线条以及根据上面的第1.2和第1.3节介绍的方式完成与0V隔离线条的电气搭接。

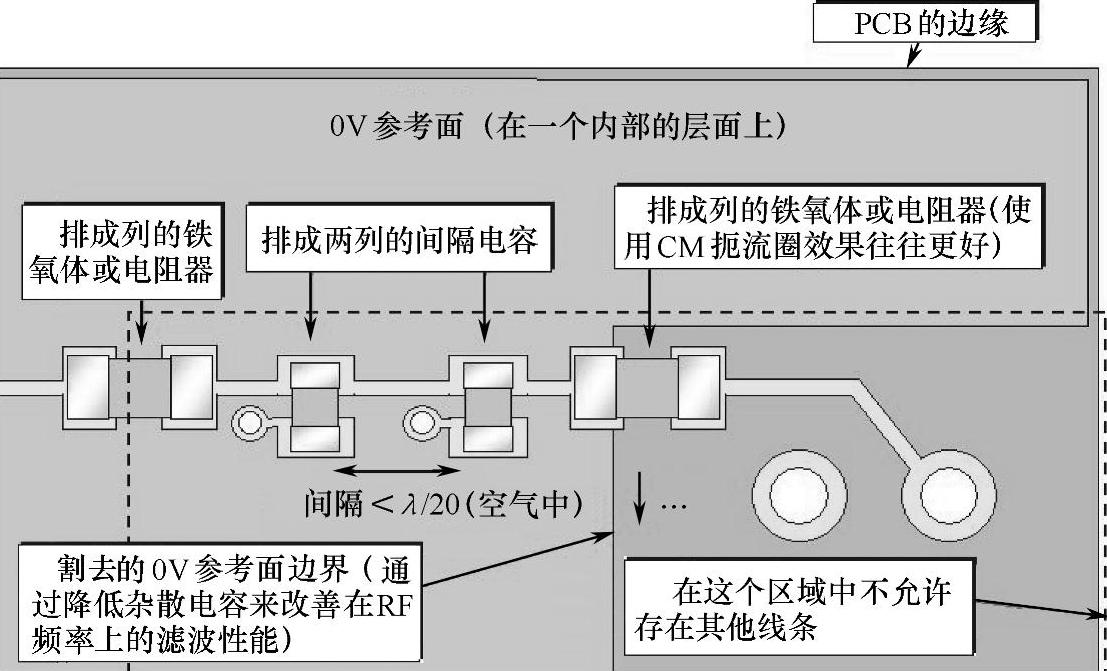

图2-1-19所示为一种可供选用的性能比图2-1-17所示的更好的电路设计和PCB布局。它的性能有时甚至比图2-1-18所示的更有所改善(这取决于不同的应用)。但该图中与一个T形滤波器的输入端和输出端分别有关联的两个电流环路分享相同的电容。因此,在两个电流环路之间不可避免地存在有磁通(磁力线)耦合。这种耦合必然会降低滤波性能。即便在电容器中,它的线条中或通孔中不存在(事实上,总会存在)电感部分(分量),上述情况也依然存在。图2-1-19中通过使用两个间隔很远的半值电容来降低这种耦合。因此,与滤波器的输入电路有关联的电流环路与它的输出环路的磁通耦合就会低得多。

图2-1-18 使用带有“馈通电容”的T形滤波器的未屏蔽离板连接器布局的例子

(比如,Murata NFM18)

图2-1-19使用具有间隔并联电容T形滤波器的未屏蔽离板连接器布局的例子

当频率处在要完成滤波的最高频率情况下,图2-1-19中的两个半值电容之间的最大间隔距离为λ/20(此式使用的是在空气中的传播时的λ值,若是在FR4中,上式则应为λ/10)。否则的话,两个半值电容间的电流环路会产生谐振而降低它们的效果。

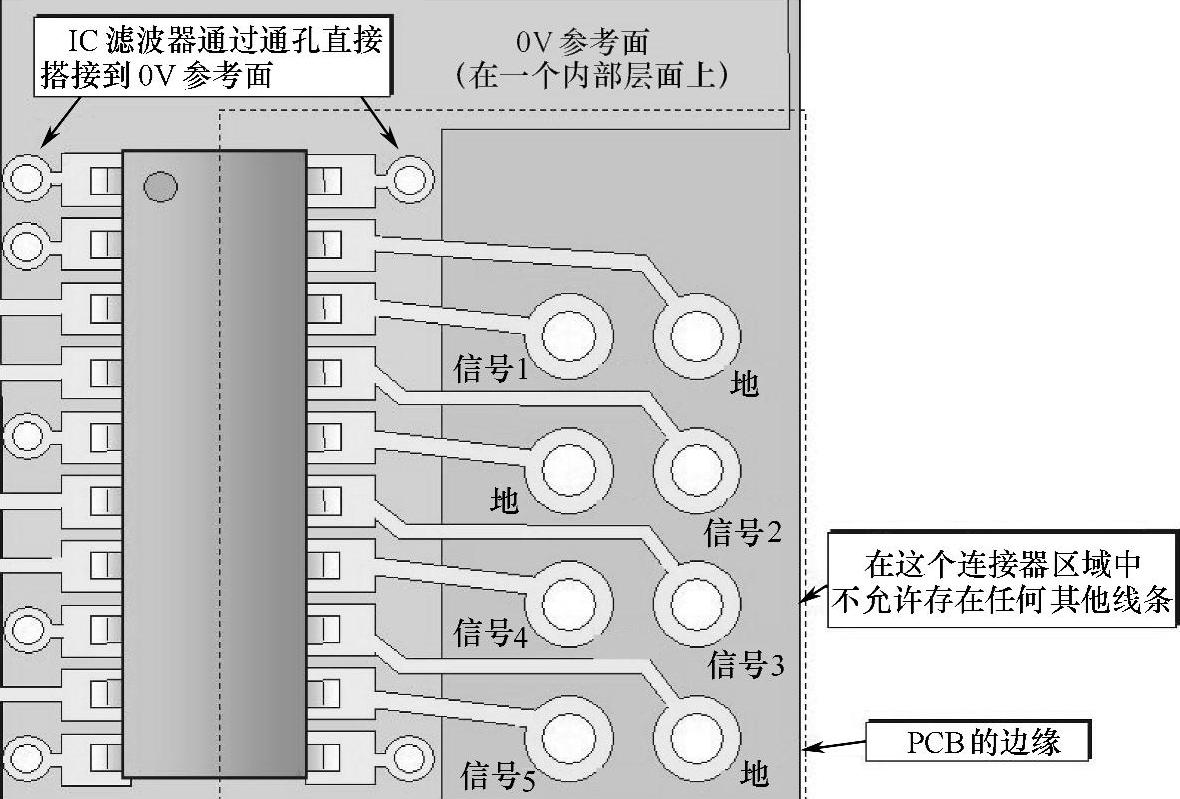

图2-1-20显示的是一个集总T形滤波器的正确使用方法。Murata NFE31滤波器系列就是这类滤波器中的一种。集总T形滤波器是一类三端器件,它们的中心端子必须直接焊接到一个0V隔离线条上。实际上,这种焊接方式已在图2-1-2,图2-1-11以及图2-1-18中分别有所显示。请不要忘记:在隔离线条上还存在有两个0V通孔等距的被设置在每个滤波器件的两边。

在希望采用开有“鼠洞”的屏蔽罩壳的隔离壁来改善图2-1-20所示滤波性能的场合,隔离壁应该沿着0V隔离线条设置。并根据前面所讨论的结果,将电容搭接到0V隔离线条上。

图2-1-20 使用集总T形滤波器未屏蔽离板连接器的例子

(比如,Murata NFE31)

图2-1-21所示为使用一个IC封装型的集总滤波器。IC式滤波器可以是铁氧体、RC、LC,T和π形滤波器阵列。它们的主要优点是节省了大量的PCB面积。市场上已出现并可购置到使用硅IC工艺生产的电阻T以及π形滤波器(比如,由California Micro元器件公司生产的这类产品)。制造厂商并声称由于与这些产品的内部电容相关联的电感有所下降,它们在频率为300MHz以上时的滤波性能要优于传统的分立式的同类型产品。目前还不太清楚的是,在IC式滤波器的什么位置上设置开有“鼠洞”的屏蔽罩壳壁最为合适。因此,在缺乏其他有关信息和数据资料的情况下,建议仍将隔离壁设置在这类器件的中心部位上。

图2-1-21 使用一个IC滤波器的未屏蔽离板连接器布局的例子

(比如,www.calmicro.com)

如图2-1-20和图2-1-21中所显示使用的那些集总滤波器所能提供可供选择类型的滤波器要少于那些在图2-1-16、图2-1-17、图2-1-18和图2-1-19中所使用的由分立元器件构成的滤波器。但集总滤波器所要求的PCB空间远小于分立式的,所以根据应用的不同和所受到的限制,采取某种折中方案往往是可取的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。