在屏蔽罩壳上的孔洞包括有折叠金属结构中的缝隙、用于对屏蔽罩壳内的元器件进行调节所留有的小孔、帮助防止在自动焊接过程中由于热胀冷缩出现“爆裂”的预留孔(如前所述,这类爆裂会使焊接质量变差),以及在屏蔽罩壳主体与在它的第六面上的PCB参考面层之间电气搭接间的间隔。在前面的讨论中已提及过这类由环绕电镀通孔周围的净空间孔所引起的问题。

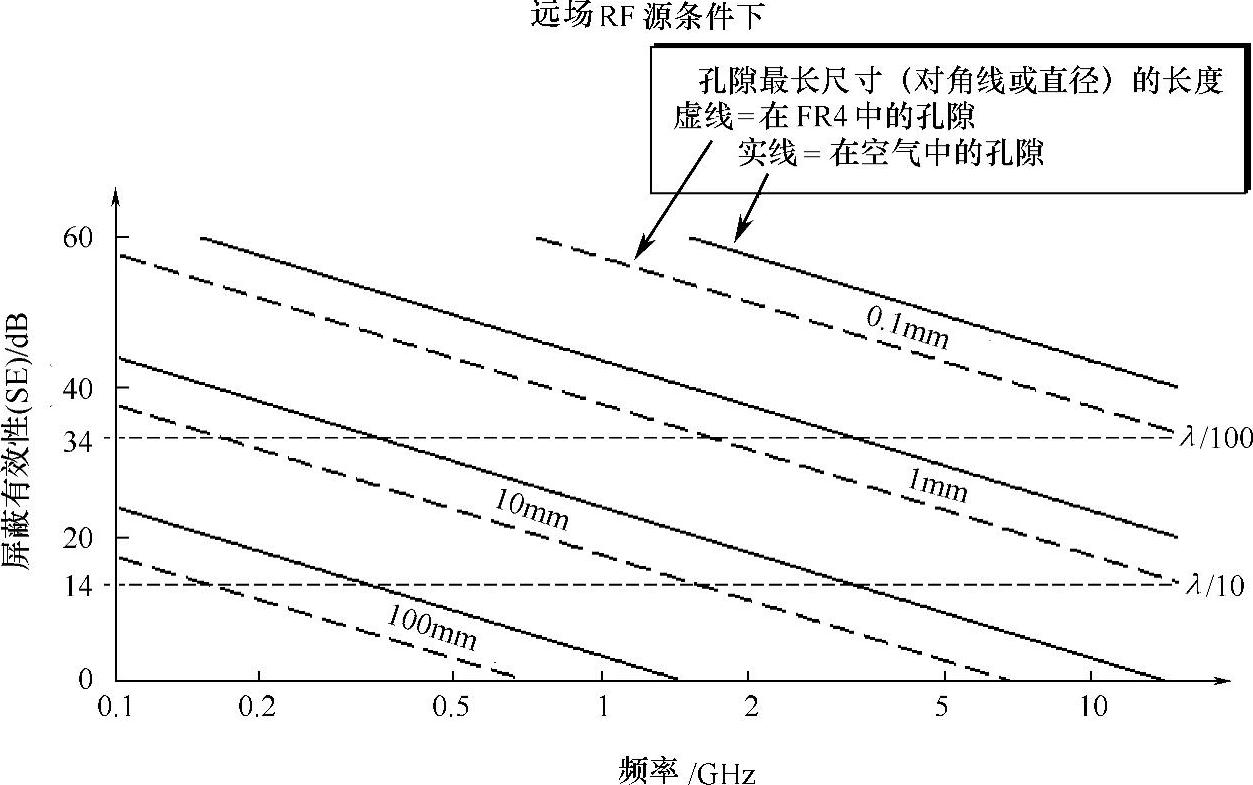

屏蔽上孔隙的尺度必须远小于对要求形成屏蔽的最高频率的波长。具有单个孔隙的一个屏蔽,若该孔隙的最大对角线尺寸为一个波长的百分之一(1/100)的话,那么在该相应频率上,我们所能期望的屏蔽罩壳的SE不会大于34dB。这个值可以很容易的在图2-1-6中找到。

图2-1-6 单一孔隙SE的估算

我们知道,一个频率为f的信号,在空气中传播时的波长(λ)为300/f(mm)(这里频率的单位为GHz)。而同一频率的信号在PCB中的波长大约仅为上述波长的一半。这是因为PCB基板(比如FR4)材料的介电常数将使得在PCB中的电磁传播速度降低仅为在自由空间中一半的缘故。

每当在屏蔽罩壳一个面上的孔隙数目加倍时,在垂直于该表面方向上的SE将会降低多达6dB。因此,假如在一个屏蔽罩壳的一个面上若有8个相同尺寸的孔隙的话,而每一个孔隙的最大尺寸都是所关心最高频率的λ/100,那么在该频率上,垂直于该表面上的SE不可能期望会超过16dB。(https://www.xing528.com)

由屏蔽罩壳与PCB内层面的电气搭接所形成的孔隙,通常会部分暴露于PCB表面上部的空气中,部分处于PCB内。在给定波长的情况下,如前所述,后者中的波长,仅为前者中的一半。所以,要决定这些搭接所形成的间隔距离,最好是保守地假定每个这样的孔隙都全部处在PCB材料中。换句话说,要选用搭接的间隔距离应仅为假定暴露在空气中间距的一半。

例如,围绕一个每边边长为50mm正方形的屏蔽罩壳的任何方向上,为了满足在频率为3GHz上获得20dB的SE要求,我们首先会注意到,在这个频率上,它在空气中的波长为100mm,而在PCB材料中的波长仅为50mm。所以,在空气中一个单个的直径1mm的圆形孔隙或者说在PCB中直径为0.5mm的圆形孔,将会使该屏蔽罩壳在该面上可获得的最大SE限制在不会超过34dB的水平上。若具有7个这样的孔隙时的SE将不会超过20dB。

因为该屏蔽罩壳的每边边长为50mm,若采用0.5mm作为它与PCB内部参考面层电气搭接间距的话,将会导致沿着该边形成100个间隔孔隙。这个数目大大地超过了为获得我们所规定的20dB指标的最多为7个孔隙的要求。在这个案例中的关键是涉及一个参考面层(或宽“隔离线条”)的使用。而这个结果正是由于通过使用一个与屏蔽罩壳的安装处在相同PCB表面上的一个参考面层(或一个宽隔离线条),而两者之间的搭接又是采用的将屏蔽罩壳的隔离壁在电气上沿着它的整个长度以多点搭接方式搭接到该层面(或宽线条)上的方式所获得的。解决上述问题的关键就变成如何消除这类多点搭接所形成的孔隙。为此,使用金属屏蔽罩壳“缝隙焊接”的传统做法或使用导电密封衬垫和导电胶都可以达到同样解决问题的效果。

这样做的好处是与PCB内部参考面层的电气搭接将不再在PCB的表面上部的空气中形成孔隙。但我们仍然还有在隔离线条和PCB内部参考面层之间的通孔空间所形成的孔隙问题。使用一般THP PCB技术来将这个孔隙直径缩小到1mm以下是有困难的。但是截止频率以下波导技术(请参阅以下的介绍)可以在相当程度上解决这个问题,从而改善屏蔽的SE。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。