在频率为30MHz以上时,采用普通结构的金属构件就可以很容易的获得100dB或更高的SE值。但前提是它必须具有一个完整屏蔽的封闭容积。除非你已经准备围绕整个屏蔽进行接缝焊接,并且不允许有接缝或缝隙的存在。并且还不准许有外部电缆、天线或传感器存在(这些要求将使得产品变得非常奇特)。所有上述这一切要求使得产品的装配变得相当困难。

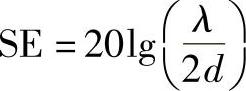

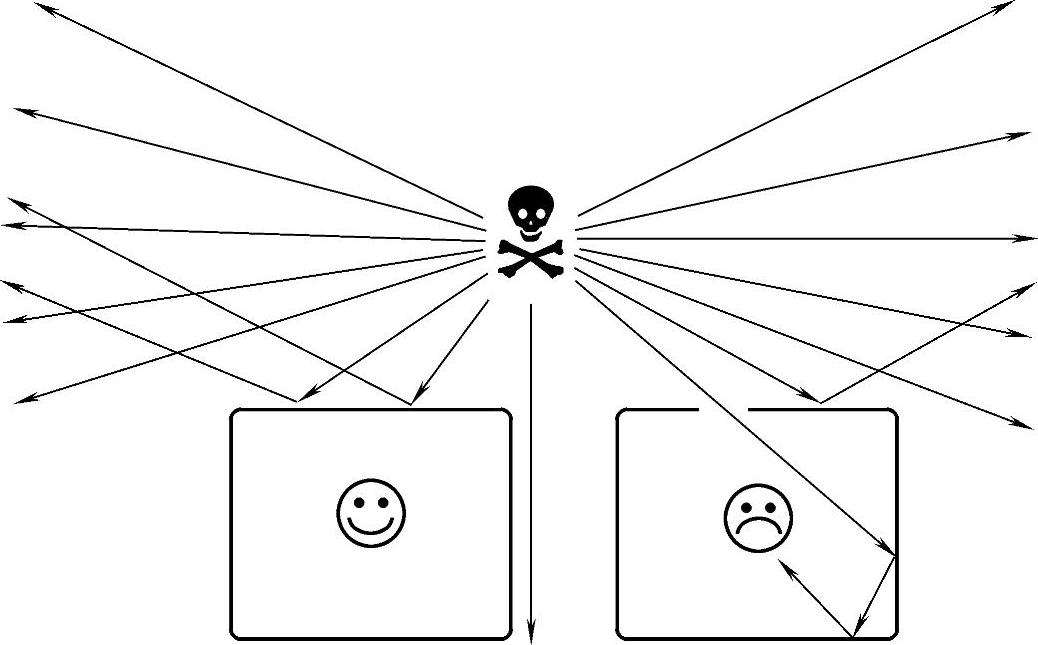

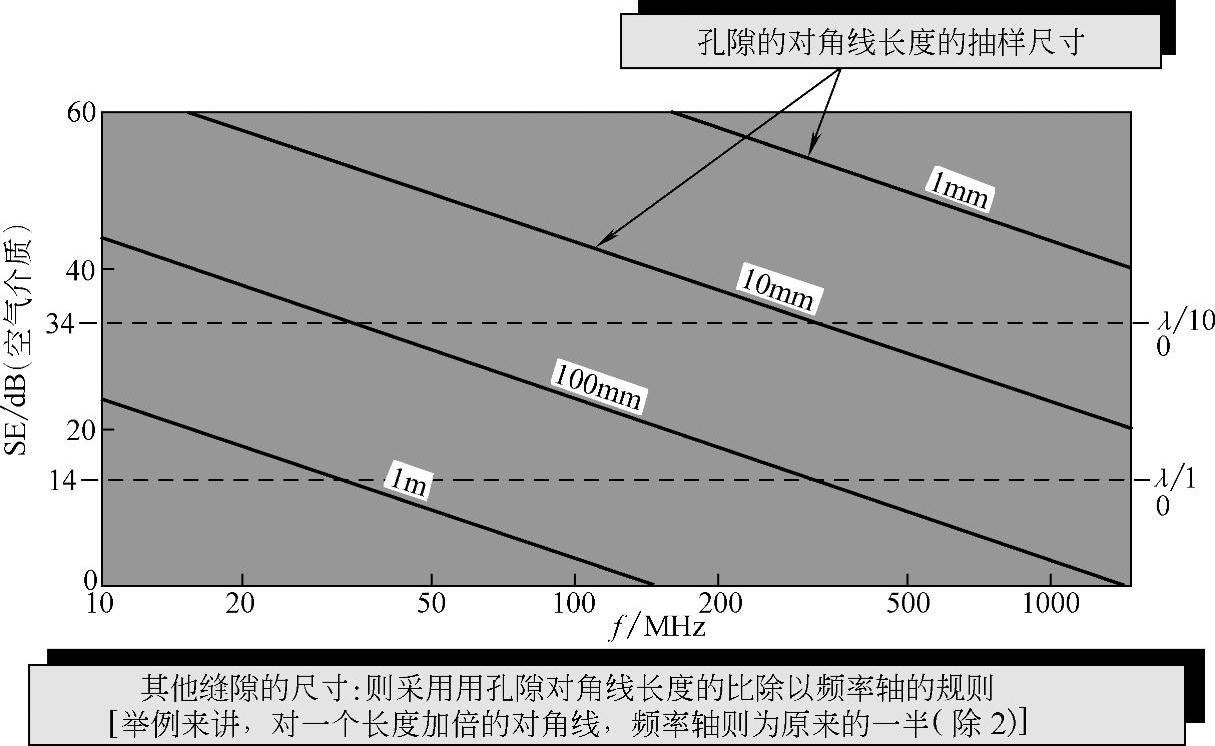

在实际应用中,不论是使用屏蔽来降低发射,还是使用屏蔽来改善抗扰性能,屏蔽性能大都会受到屏蔽罩壳上缝隙的限制。图1-4-2和图1-4-3试用图示的方法来表达上述的情况。

把屏蔽上的一个缝隙考虑作为一个完整屏蔽上的一个孔洞,隐含有它们将起到一个半波谐振“缝隙天线”作用的意思。这就允许我们对一个给定的SE来预测允许的最大缝隙的尺寸:对一个单一缝隙:

式中λ——所研究频率的波长;

d——缝隙的最长尺寸。

图1-4-2 抗扰屏蔽

(屏蔽的有效性大都受到孔隙的制约)

图1-4-3 辐射屏蔽

(屏蔽的有效性大都受到孔隙的制约)

在实际应用中,虽然这个计算并不总是那么准确,但作为一个估算工具,它具有使用方便的优点。这总要比什么都没有来得好。若在发现由此得出的预测不那么准确的情况下,我们仍可以根据实践经验和针对特定产品上所使用的技术和构成方式进行修正。

缝隙天线的谐振频率是由它的最大尺度所决定的。这个最大尺度也就是它的对角线。至于缝隙的宽窄,以及甚至视线是否可以穿过缝隙,对它的谐振频率几乎没有什么影响。

即便由金属薄板的重叠所形成的缝隙,并有一定厚度的漆膜或氧化膜所覆盖着,它仍然会像一个宽到可以让一个手指都伸进去的缝隙一样,在它的谐振频率产生辐射(泄漏)。

在现代电子产品内部所使用的频率与我们的通讯和广播所赖于的频率范围没有什么不同。如图1-2-1和图1-2-2。

最重要的EMC问题之一是要保持产品的内部频率在其内部。以防止由于它们的泄漏而污染外部的无线电频谱。

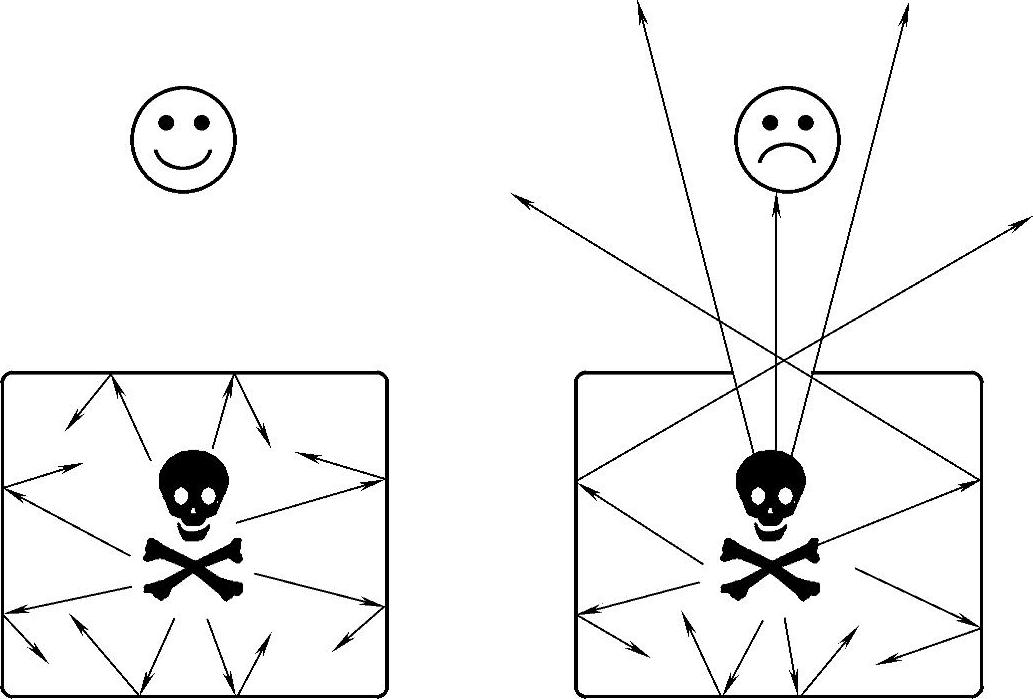

图1-4-4显示了,在屏蔽上的缝隙如何有效地起着类似天线的作用。造成内部频率发射到外部,并干扰无线电频谱。

图1-4-4 一个屏蔽(罩壳)上的空隙是一个有效天线

缝隙天线的半波谐振(前面已列出计算它的经验公式):

SE=20lg(λ/2d)(https://www.xing528.com)

是图1-4-4(以及图1-4-5中的经验公式)中粗实线使用的基础。

v=fλ

这里v——光速,3×108m/s;

f——频率(Hz);

λ——波长(m)。

我们发现,位于一个19in机架前面板边缘的一个430mm长的窄缝,在频率大约为350MHz上将形成它的半波谐振。因此,该19in的前面板在这个频率上已不再能提供什么有用的屏蔽。即便是将它拿掉,屏蔽性能也不见得会有什么太大的差异。

对一个给定的SE,要对一个缝隙的最大尺度所能产生的影响进行预测,图1-4-5是非常实用的。如需要还可以很容易地改变它的比例尺寸来满足不同尺度要求。

在频率为1GHz(它代表了大多数标准中的测试上限)上,如果要求的SE为20dB的话,图1-4-5指出,一个缝隙的长度不应大于16mm。若要求的SE增加到40dB的话,缝隙长度则不能长于1.6mm。这将要求我们使用下面讨论的密封衬垫来密封缝隙或使用截止频率以下的波导技术。

在实际应用中,SE的实际值将取决于罩壳本身的隔离壁之间的内部谐振、元器件以及导体与缝隙之间的接近程度(请记住:要将诸如携载数字信号总线,带状电缆这类噪扰电缆远离屏蔽上的缝隙和接缝),以及用于装配罩壳各个部件所使用的紧固件阻抗等。

只要有可能,就应将所有必需的或不可避免的缝隙分割成若干个较小的缝隙。特别是不可避免的长缝隙(盖子,门等),则需要使用导电密封衬垫或指簧(或其他保持屏蔽连续性的方法)加以密封。下述经验公式告诉我们:若干个小的相互邻近的相同缝隙的SE正比于(粗略的)它们的数目。

ΔSE=20lgn

图1-4-5 用于单个缝隙屏蔽有效性(SE)判断的一般准则

这里的n是指小缝隙的数目。所以,两个尺寸相同的缝隙的SE值要比单一相同尺寸的缝隙的SE值下降大约6dB。4个则下降12dB,8个则下降18dB,等等。当所关心频率的波长变得可以与小缝隙阵的整体尺寸相比拟时,或这些小缝隙并不处于相邻近的位置上(与波长相比,它们之间的距离)时,上述粗略的“数目每增加一倍,SE下降6dB”的估算方法将解析成相位抵消效应。但好在这个简单估算方法的误差是出现在更为保守的一侧。

当所安置缝隙间的距离大于半波长时,它们总的SE值通常不会比单个缝隙所获得的更差。但对几何尺寸相对较小的产品来说,情况会有所不同。举例来说,在100MHz这样的低频率时,我们知道其半波长为1.5m。若在一个小于这个尺度的典型产品上增加缝隙的数目,将会形成使罩壳的SE变差的倾向。

存在于屏蔽上的缝隙不仅仅会呈现为一根缝隙天线。而且会由于它的存在,使得屏蔽中的流通电流会被迫沿着缝隙的周边改变它们的通路,从而引起磁场发射。与此同时,在缝隙两边形成的电压差也将会引起缝隙发射电场。作者就曾看到过这样的一个微控制器,在它的PCB上安装有一个带有一个直径不大于4mm小孔(设计用于安装一个柱形的固定夹)的小型屏蔽罩。就是这个小孔,在130MHz频率上形成了电平高得惊人的发射。虽然图1-4-7显示,在该频率上,来自那个4mm小孔的SE值相当不错。但由于来自这样一个特别噪扰的微控制器的发射会在屏蔽罩中引起相当大的电流流通。显然,就是这个原因造成了发射。而不是小孔的天线效应。在涉及长窄形缝隙的地方,有时可以通过想办法改变缝隙的长边与内部电路之间的相对位置,从而改变它们之间的相对方向来降低这类发射。

但要注意的是,上述这些讨论所形成的建议都是非常粗略的。经常会由于电缆之间过于靠近,罩壳内重载电流的流动等因素的影响,而无法达到预期的效果。

为了找出任何一个带有缝隙的复杂罩壳的SE值,唯一真正精确的做法就是将其结构,并包括所有PCB和导体(特别是那些接近缝隙的)模型化。然后,使用三维场求解器求解SE值。现在的这类软件包都有许多用户容易掌握使用的接口,并可以在普通台式PC上运行。另一个途径就是通过某个大学或咨询机构,并利用它们的设备、软件系统和技术来完成你所需要的建模。

假如,你不想采用或没有条件使用场求解方法的话,剩下的最好办法就是制作一个与实物尽可能相近似的大模型。它应该包括所有内部电路和其他元器件。然后,将它置于一个EMC实验室中进行实地测试。前面已特别指出过,这类测试要在尽可能早的项目开发阶段上进行,以免以后出现不愉快的惊奇。最后还需要强调的是,虽然可用的SE测试方法很多,但几乎没有哪一个或几个已被标准化。

因为SE值会随着装配方法和质量、材料以及内部PCB和电缆的差异变化很大。在设计过程中,为SE留有20dB的“保险系数[31]①”是非常必要的。一旦在项目后期的校验/质量测试中出现问题时,还有改进的余地。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。