单稳态电路(简称单稳,又称单稳态触发器)具有如下特点。

① 具有一个稳态和一个暂稳态,无操作时,电路维持稳定状态。

② 外来触发可以将触发器由稳态翻转到暂稳态。

③ 暂稳态经过一段时间,自动翻转回稳态。

单稳电路被广泛应用于定时、延时、整形、波形变换等场合,是一种重要电路。

1.用555定时器构成的单稳态电路

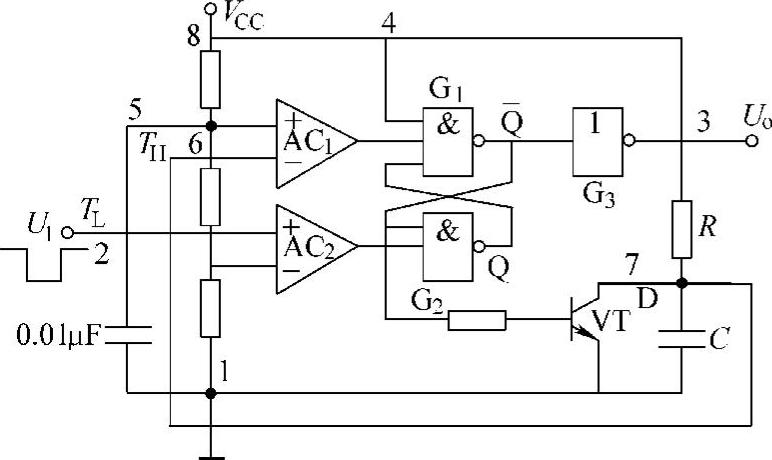

用555定时器构成的单稳态电路如图5-16所示。

定时电阻R接在放电端(⑦脚)和电源VCC(⑧脚)之间,定时电容C接在⑦脚和地(①脚)之间,⑥脚(高触发端TH)与⑦脚连接,这样就构成一个下降沿触发的单稳态触发器,低触发端TL(②脚)为触发输入。

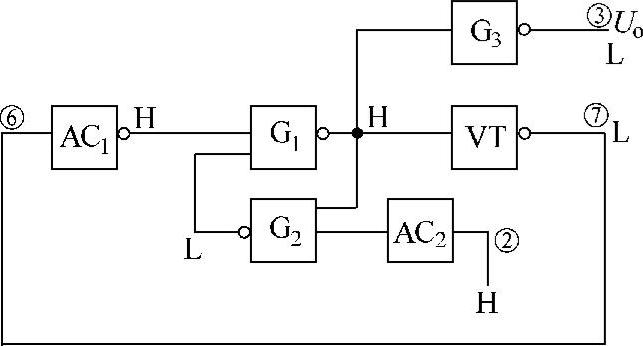

(1)稳定态。②脚(TL)为高电平时,电路处于稳定态,③脚输出低电平。图5-17所示为用555定时器构成的单稳态电路稳态等效结构及各点状态。

图5-16 用555定时器构成的单稳态电路

图5-17 用555定时器构成的单稳态电路的稳态等效结构及各点状态

显然,电路各点之间呈互锁关系。即电路接通电源的瞬间,R-S触发器输出为高电平, 使晶体管VT截止,电容C则被VCC经R充电。当UC=2VCC/3时,比较器AC1输出跳为低电平,使R-S触发器置0,③脚输出跳为低电平,同时因

使晶体管VT截止,电容C则被VCC经R充电。当UC=2VCC/3时,比较器AC1输出跳为低电平,使R-S触发器置0,③脚输出跳为低电平,同时因 使晶体管VT饱和导通,电容C被放电,⑥、⑦脚变为低电平,电路进入锁定的稳态。

使晶体管VT饱和导通,电容C被放电,⑥、⑦脚变为低电平,电路进入锁定的稳态。

(2)暂稳态。处于稳定态的电路,若②脚出现触发脉冲下降沿(Ui<VCC/3)时,比较器AC2输出低电平,R-S触发器置1,③脚输出高电平。同时,因 晶体管VT截止,电容C充电。当UC=2VCC/3时,比较器AC1跳为低电平,R-S触发器置0,使电路输出跳回低电平。同时,因

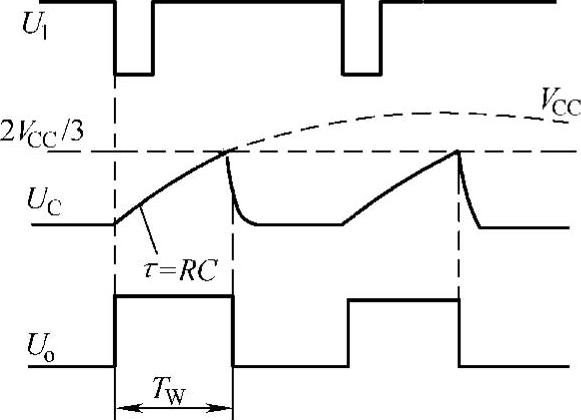

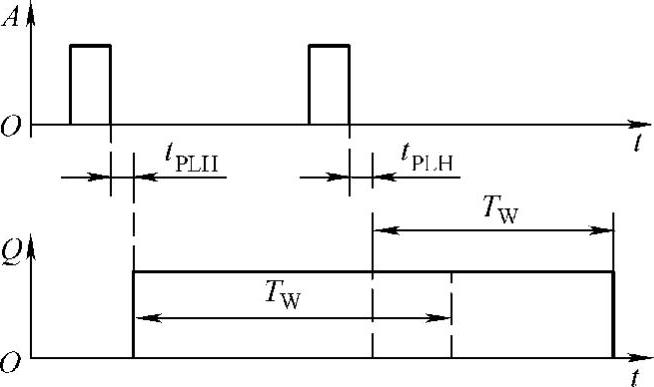

晶体管VT截止,电容C充电。当UC=2VCC/3时,比较器AC1跳为低电平,R-S触发器置0,使电路输出跳回低电平。同时,因 ,晶体管饱和导通,电容C放电。此时,如果触发输入已为高电平,电路则锁定于稳定态;若触发输入仍维持低电平,电路就会重复以上的暂稳态过程。因此,电路的触发脉冲只能是宽度很窄的负尖峰。电路的工作波形如图5-18所示。

,晶体管饱和导通,电容C放电。此时,如果触发输入已为高电平,电路则锁定于稳定态;若触发输入仍维持低电平,电路就会重复以上的暂稳态过程。因此,电路的触发脉冲只能是宽度很窄的负尖峰。电路的工作波形如图5-18所示。

如果忽略晶体管VT的饱和压降,电路暂稳态时输出的脉冲宽度为

TW=RCln3≈1.1RC(https://www.xing528.com)

变化范围可从几微秒到数分钟,准确度可达0.1%。

给上述单稳态电路的触发端接一个检测逻辑电路用的逻辑开关(作为触发信号输入装置),用万用表监测单稳态电路的输出电压变化,再用计时秒表记录电路保持暂稳态的时间,就可以测试单稳态电路的参数。

图5-18 用555定时器构成的单稳态电路工作波形

2.集成单稳态电路

在TTL和CMOS集成电路系列产品中,有多种单稳态电路的成品。单稳态集成电路温度漂移小,性能稳定可靠,而且暂稳态可调范围大,抗干扰能力强。

单稳态电路有可重触发和非重触发之分,触发方式有下降沿触发和上升沿触发两种。所谓非重触发,是指电路在暂稳态期间不接受再触发,暂稳时间固定的工作类型。可重触发是指电路在暂稳态期间接受再触发,使暂稳时间延长的工作类型。

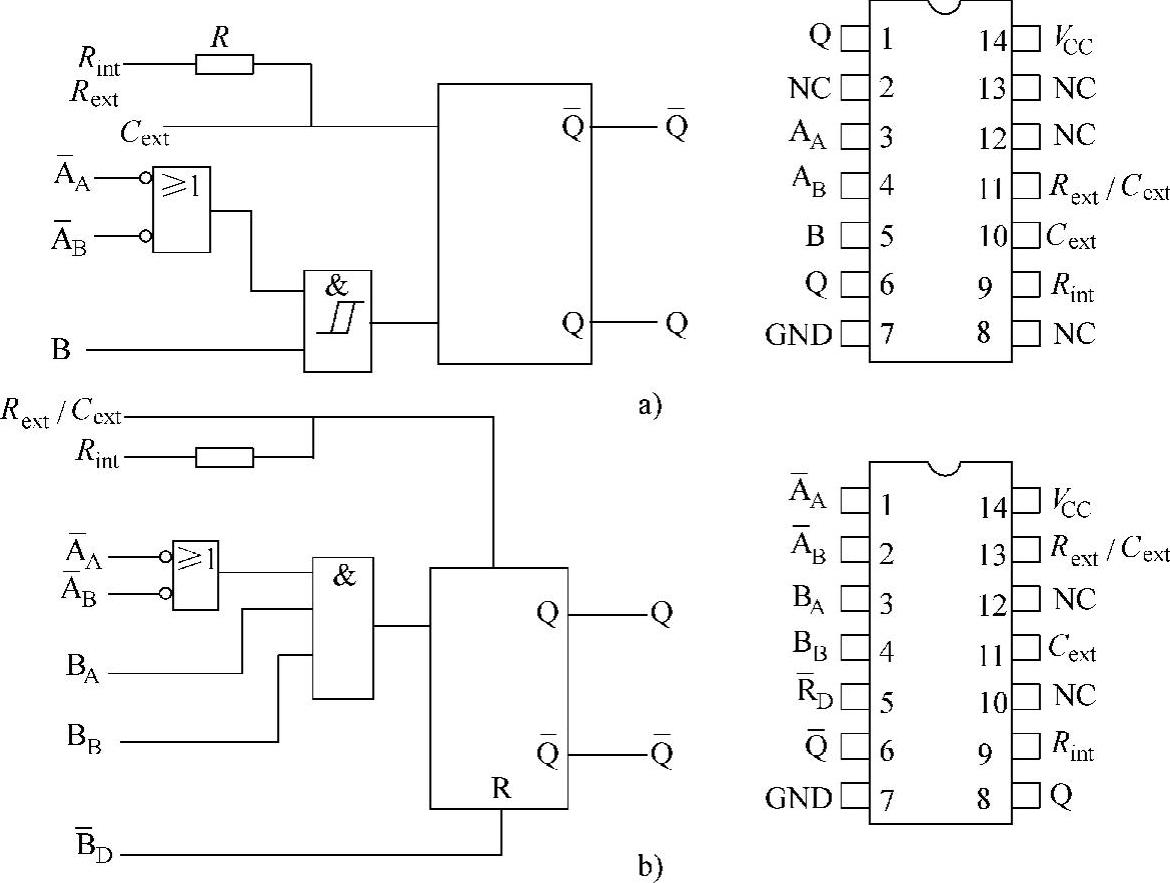

图5-19为TTL系列集成电路74121(含施密特门电路的单稳触发器)、74122(可重触发的单稳触发器)的内部结构和引脚排列方式。

电路有两个负跳变触发输入端( 、

、 ),两个互补输出(Q、

),两个互补输出(Q、 ),Rint(内定电阻)引出端,Rext/Cext(外接电阻、外接电容)引入端。使用时,外接电容接在Cext和Rext/Cext两个引脚上。74121有一个可用于禁止负跳变输入的正跳变触发端B,74122设有两个正跳变触发输入端BA和BB。使用内定电阻,将Rint端接VCC;使用外接电阻,将Rint开路,外接电阻接在VCC和Rext/Cext两引脚之间。图5-20为电路的工作波形。

),Rint(内定电阻)引出端,Rext/Cext(外接电阻、外接电容)引入端。使用时,外接电容接在Cext和Rext/Cext两个引脚上。74121有一个可用于禁止负跳变输入的正跳变触发端B,74122设有两个正跳变触发输入端BA和BB。使用内定电阻,将Rint端接VCC;使用外接电阻,将Rint开路,外接电阻接在VCC和Rext/Cext两引脚之间。图5-20为电路的工作波形。

图5-19 集成电路74121和74122的内部结构和引脚排列方式

a)74121 b)74122

图5-20 74122工作波形

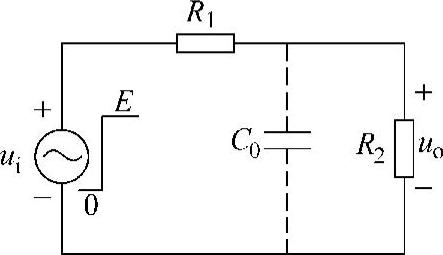

图5-21 电阻分压电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。