实际的时序逻辑电路有两类。一类是系列产品中的成品集成电路,如各种寄存器、计数器、环形计数器等。对于这类时序逻辑集成电路的识别,可按照芯片型号去查相应手册,了解它的功能和各引脚信号的作用。另一类是用触发器及逻辑门电路按所需功能连接而成的(这类电路的结构通常是比较简单的),识别分析这类电路是本部分所要介绍的内容。

1.识别时序逻辑电路的步骤

(1)确认电路类型。如果没有触发器,也没有信号反馈电路结构则不是时序电路。

(2)确认电路中的触发器的原类型,观察有无功能转换电路。初步判断时序电路的功能。表4-22列出了各种触发器在电路中的通常应用方式。

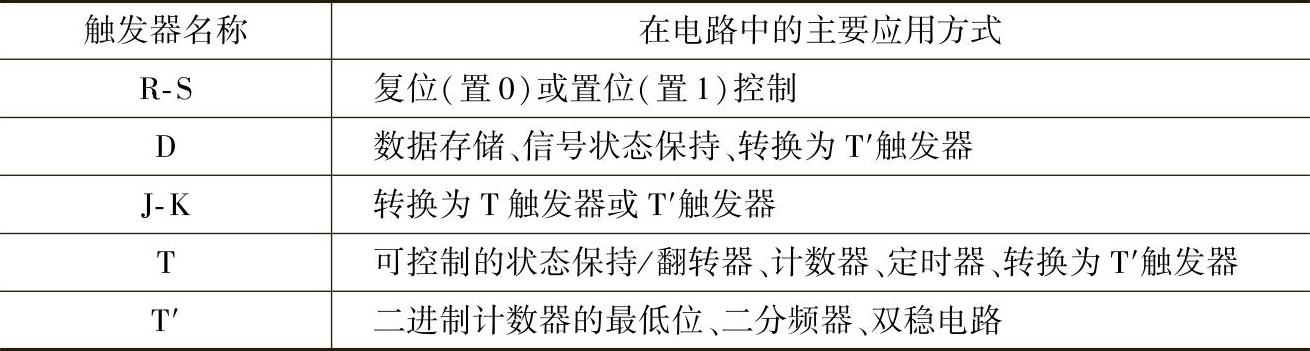

表4-22 各种触发器在电路中的通常应用方式

(3)分析触发器的各种输入信号的来源及有效电平。有时需要把被分析的部分从电路中摘出来,剔除无关信号,画出更直观的输入、输出关系电路图。

(4)分析电路的动作原理和规律。

2.实例分析——D触发器应用实例

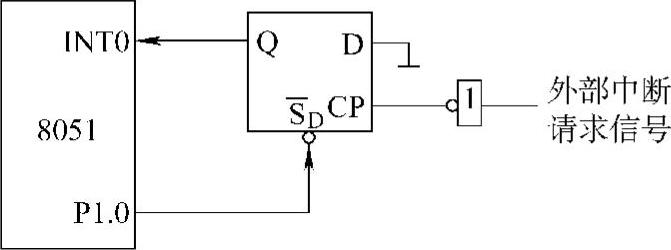

1)图4-59为使用D触发器构成的时序电路。D触发器的作用是为单片机8051形成片外中断请求信号 ,并将信号的有效状态保持到8051的中断响应完成、由P1.0口输出低电平为止。

,并将信号的有效状态保持到8051的中断响应完成、由P1.0口输出低电平为止。

电路动作原理:把D触发器的同步输入端D固定接地、构成低电平输入,触发器的输出端Q信号送入8051的 信号输入端,平时P1.0口输出高电平,对触发器不起作用。当外部设备需要8051的中断服务时,就发过一个低电平脉冲,经非门倒相变为高电平送入触发器的时钟信号CP端(前沿触发)。信号脉冲的前沿触发触发器,D端的低电平进入触发器,Q端输出低电平,发出中断请求信号。8051响应中断请求、并执行相应的中断服务程序。完成中断服务后,由P1.0口发出一个低电平信号给D触发器的

信号输入端,平时P1.0口输出高电平,对触发器不起作用。当外部设备需要8051的中断服务时,就发过一个低电平脉冲,经非门倒相变为高电平送入触发器的时钟信号CP端(前沿触发)。信号脉冲的前沿触发触发器,D端的低电平进入触发器,Q端输出低电平,发出中断请求信号。8051响应中断请求、并执行相应的中断服务程序。完成中断服务后,由P1.0口发出一个低电平信号给D触发器的 端,使触发器直接置1,触发器Q端输出高电平,撤消中断请求。

端,使触发器直接置1,触发器Q端输出高电平,撤消中断请求。

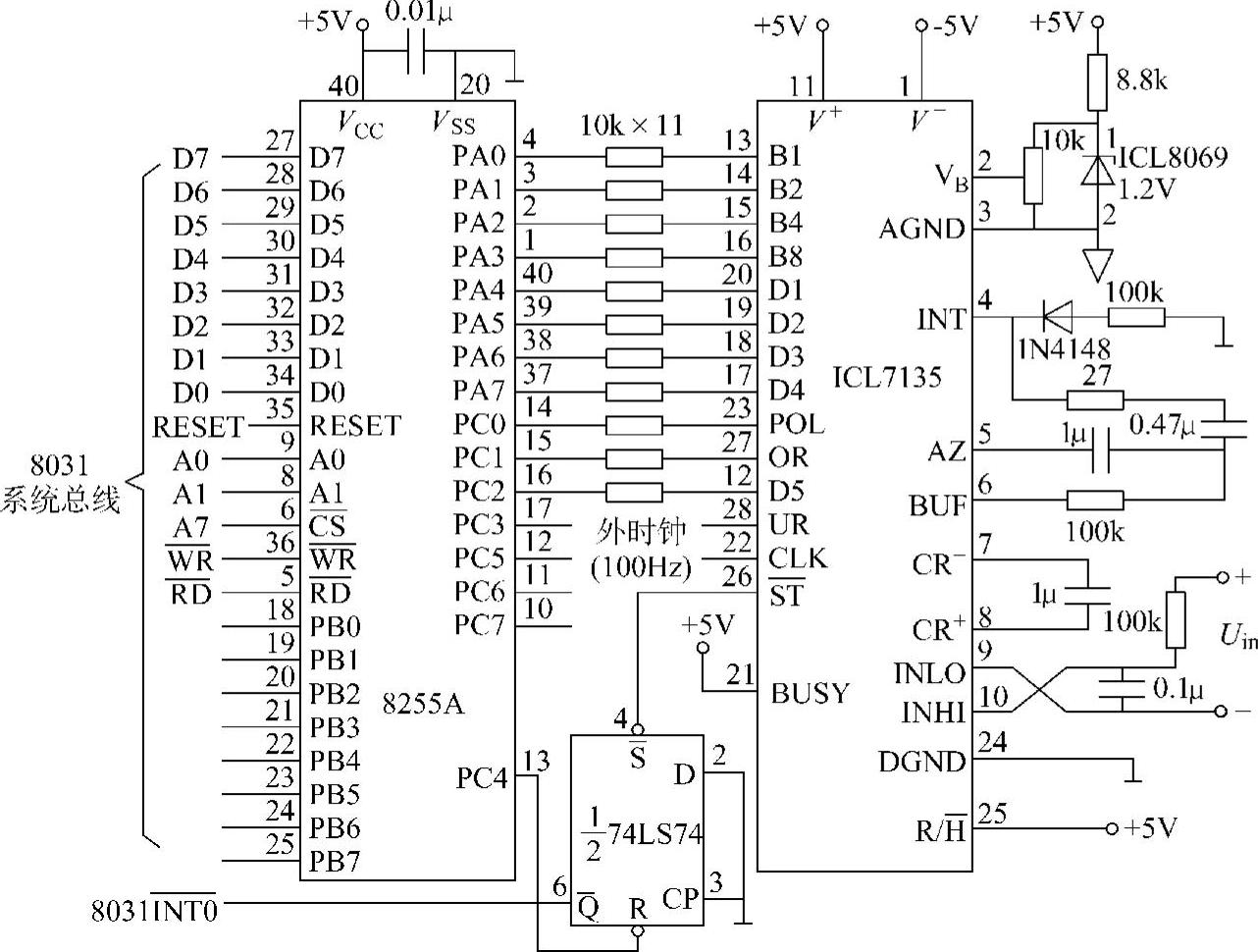

2)图4-60为ICL7135与8255A接口电路,这里只分析由D触发器构成的时序电路。

图4-59 用D触发器构成的时序电路

图4-60 ICL7135与8255A接口电路

D触发器的CP信号和同步输入端D都接地,CP信号固定为无效状态。电路只使用置位端S和复位端R,两信号都是低电平有效,但不能同时有效。触发器的 输出作为8031的INT0信号(低电平有效)。所以,当ICL7135的ST信号为低电平时,触发器被置位,Q=0,

输出作为8031的INT0信号(低电平有效)。所以,当ICL7135的ST信号为低电平时,触发器被置位,Q=0, 信号有效;当8255A的PC4口输出低电平时触发器复位,

信号有效;当8255A的PC4口输出低电平时触发器复位, ,

, 信号无效,中断请求撤消。

信号无效,中断请求撤消。

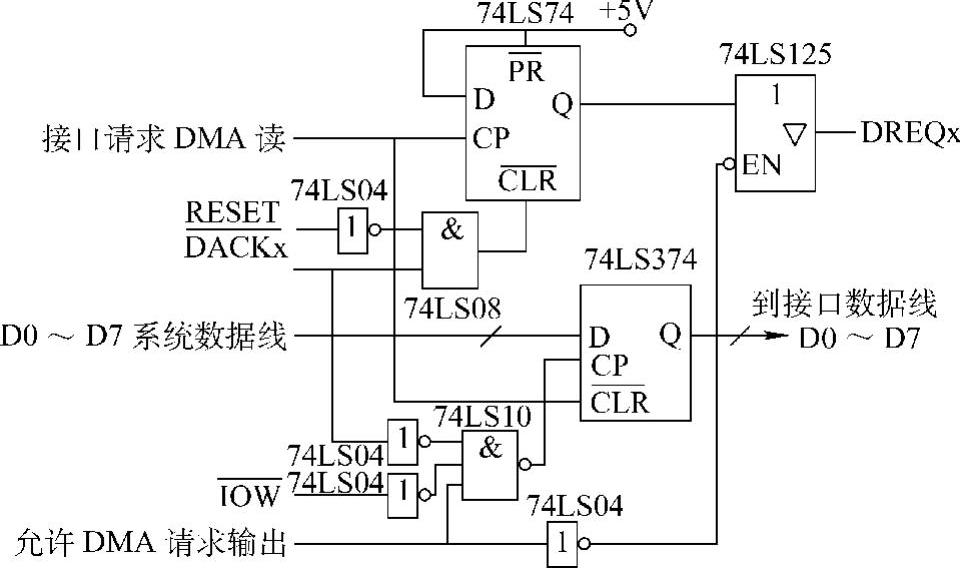

3)图4-61为PC输出至I/O装置的DMA电路,即PC的DMA方式输出电路。图中使用了两种D触发器产品,74LS374是三态同相的8D触发器,用于8位数据的暂存(以协调数据传输动作)和系统数据线的使用权切换;74LS74双D触发器(电路中只使用1个)用于形成DMA操作的请求信号DREQ(高电平有效)。

图4-61 PC输出至I/O装置的DMA电路

DREQ有效电平形成并保持的必要条件是:

① PR(预置)端为高电平,图中将该端口接电源。

② D(同步输入)端为高电平,图中将该端口接电源。

③ LR(清零)端为高电平,根据电路的逻辑关系,需要电路的 端为低电平(无效状态)和DMA操作的响应DACK为高电平(有效状态)同时具备。

端为低电平(无效状态)和DMA操作的响应DACK为高电平(有效状态)同时具备。

④ 三态传输门74LS125打开(控制端信号为低电平有效),即经非门74LS04变反的“允许DMA请求输出”信号为高电平。

⑤ “接口请求DMA读”信号(就是高电平有效的触发器CP信号)为高电平。

其中,前两个信号是固定不变的,只要后4个信号有1个不符合要求,都会使DMA操作停止。(https://www.xing528.com)

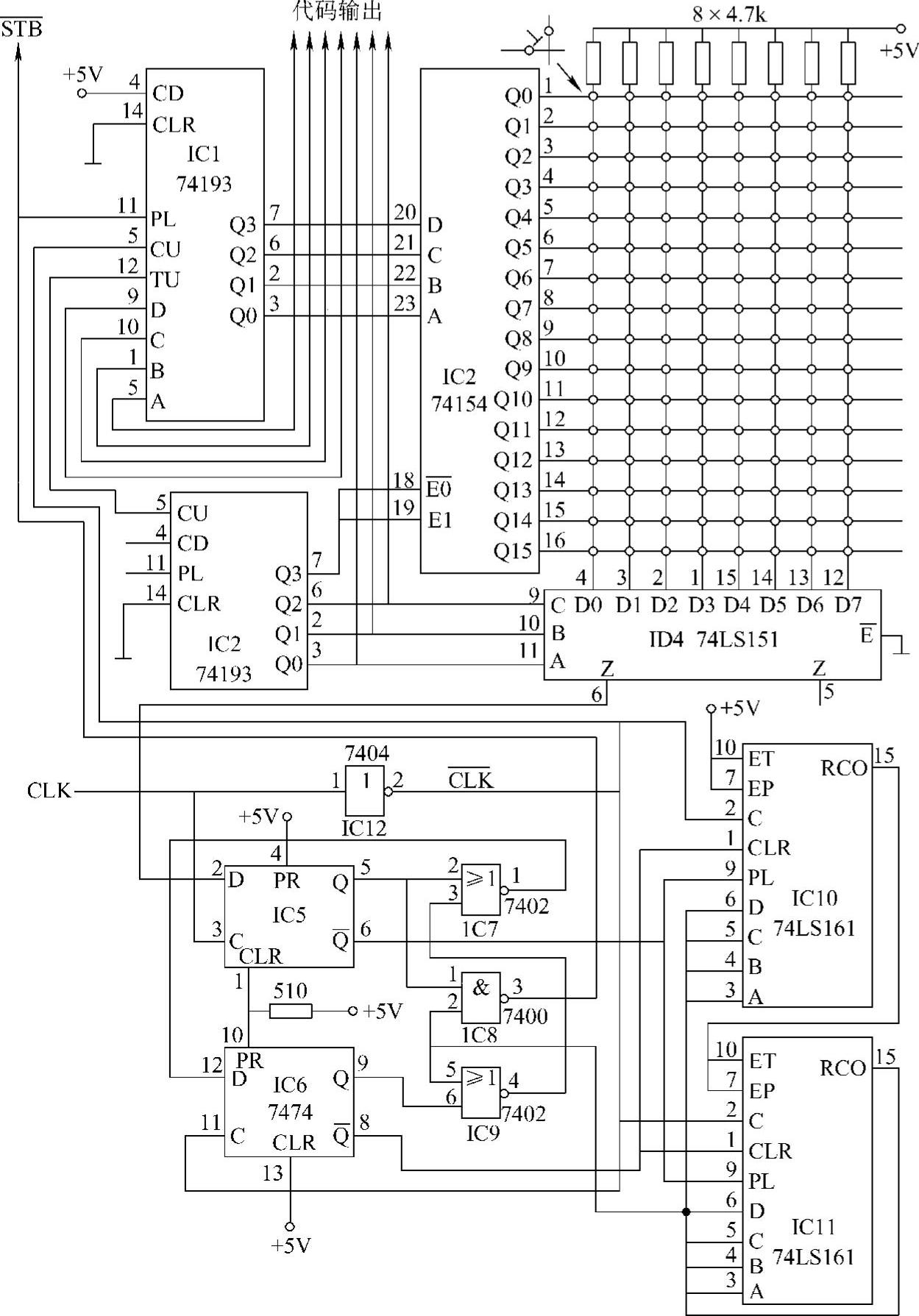

4)图4-62为硬编码方式128键键盘的控制电路。

图4-62 硬编码方式128键键盘的控制电路

键盘电路由74LS154对键盘开关阵列进行16位扫描,由74LS151读取键盘阵列状态的8位信息,并将信息转换为3位二进制编码作为输出代码的低3位,输出代码的高4位由IC1(74193)输出。

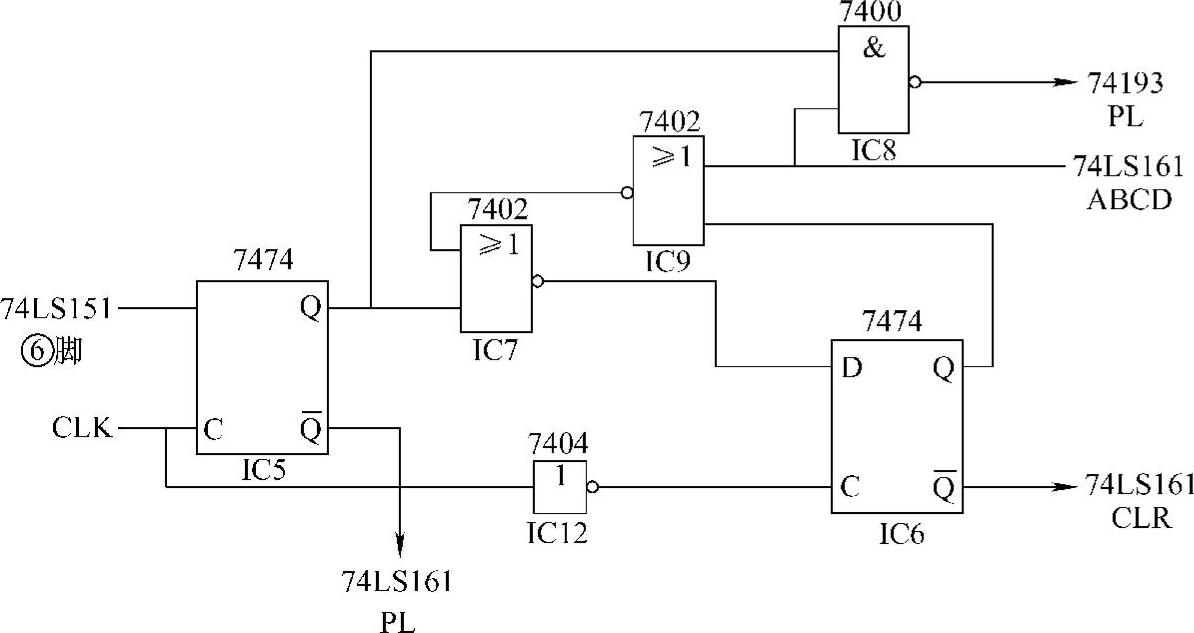

以7474双D触发器为主体构成电路的时序电路如图4-63所示。

图4-63 由7474构成的时序电路

电路的作用是为两只级联的74LS161(可预置的4位二进制计数器)形成PL(置1)、CLR(清零)信号和74193(IC1)的PL(置1)信号。

两个D触发器的预置(PR)和清零(CLR)端都固定接为高电平无效状态。两个D触发器的时钟信号C都取自系统时钟CLK,经IC12(7404非门)倒相,形成交替触发方式。74LS161的PL信号取自IC5的Q输出端、CLR信号取自IC6的 输出端。IC1(74193)的PL信号由两只74LS161的A、B、C、D八个输出端并联信号和IC5的Q端信号经IC8(7400)与非逻辑组合形成。

输出端。IC1(74193)的PL信号由两只74LS161的A、B、C、D八个输出端并联信号和IC5的Q端信号经IC8(7400)与非逻辑组合形成。

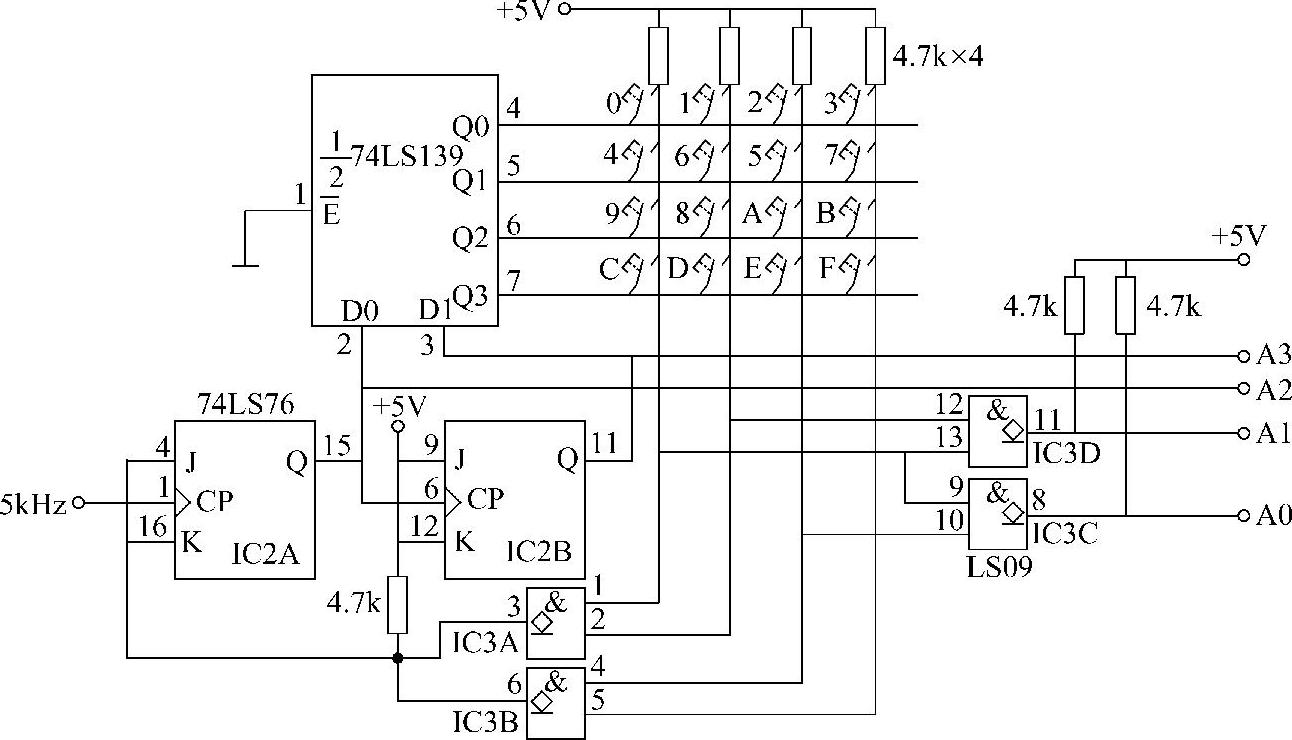

5)J-K触发器应用实例。图4-64为十六进制键盘编码器电路。

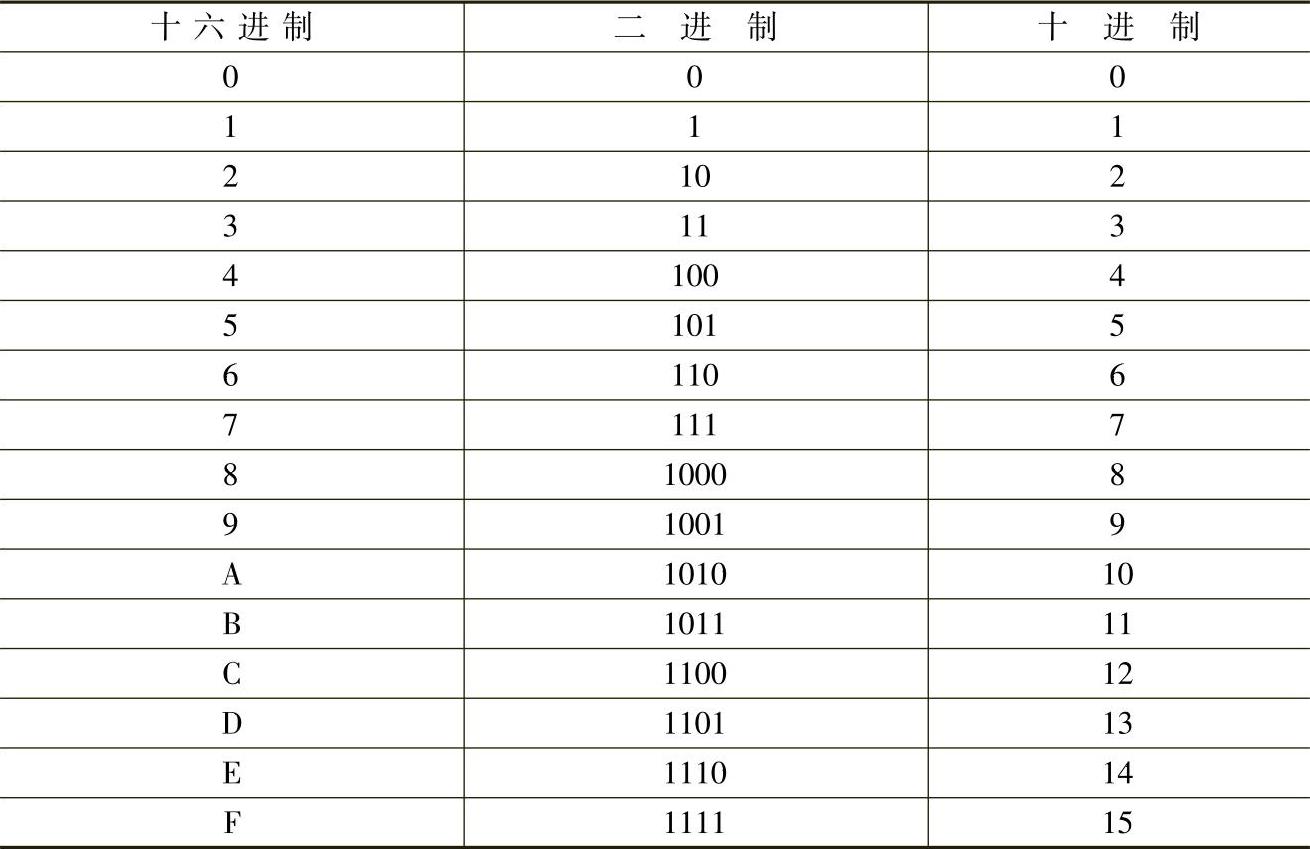

十六进制是用0~9和A、B、C、D、E、F六个字母计数的方法,逢十六进一。在计算机软件系统中,主要用作二进制码的缩写,十六进制、二进制及十进制的对应关系见表4-23。

图4-64 十六进制键盘编码器电路

表4-23 十六进制、二进制及十进制对照表

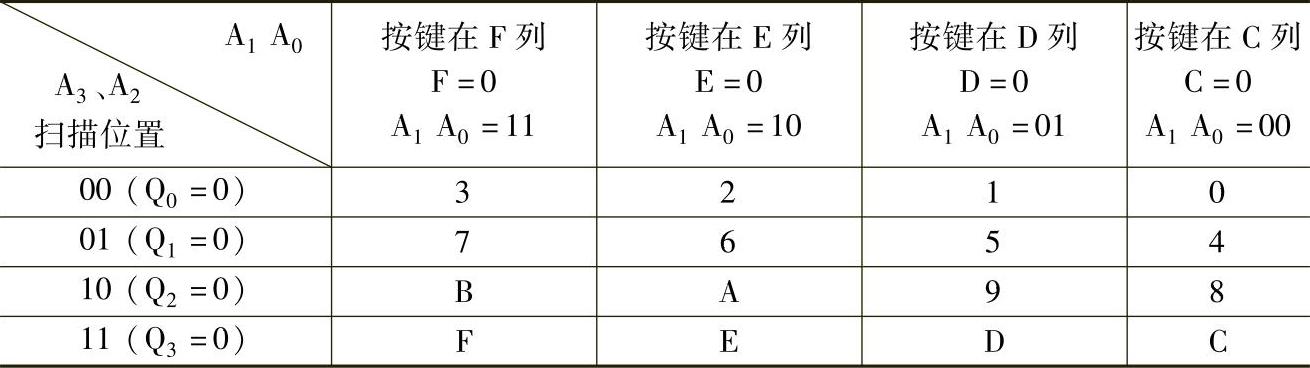

电路的功能是将0~F共16个按键的动作转换为A3、A2、A1、A0四位不同的输出码,按键与输出码的对应关系见表4-24。

表4-24 按键与输出码的对应表

电路中的时序电路由74LS76(双J-K触发器)构成,IC2A转换为T触发器,IC2B转换为T′触发器,两者共同组成一个2位二进制减法异步计数器。计数器输出作为电路输出编码中的A3、A2两位,同时又是74LS139译码输入信号D1、D0。74LS139(双2-4译码器)的使能信号( )端接地,总处于工作状态,负责为16个开关键阵列输出扫描信号。用OC与门(74LS09,输出端接有4.7kΩ上拉电阻)负责读键盘,查找被按动的键。其中,两个(IC3A、IC3B)合并为一个4输入端的与逻辑门,用于控制计数器,当有键被按住时就输出0,计数器停止动作,保持输出数据不变,形成电路输出码的高两位A3、A2,确定按键所在的行位。另外两个(IC3D、IC3C)用于形成电路输出码的低两位A1、A0,确定按键所在的列位。

)端接地,总处于工作状态,负责为16个开关键阵列输出扫描信号。用OC与门(74LS09,输出端接有4.7kΩ上拉电阻)负责读键盘,查找被按动的键。其中,两个(IC3A、IC3B)合并为一个4输入端的与逻辑门,用于控制计数器,当有键被按住时就输出0,计数器停止动作,保持输出数据不变,形成电路输出码的高两位A3、A2,确定按键所在的行位。另外两个(IC3D、IC3C)用于形成电路输出码的低两位A1、A0,确定按键所在的列位。

用C、D、E、F分别代表4列(纵线)键信号,A1、A0两位数值由C、D、E、F键信号决定。它们之间的逻辑关系是:

A1=C·D

A0=C·E

C、D、E、F键信号在无按键时都为高电平;有按键时键开关把行、列线接通,键所在的列线被74LS139输出的扫描信号拉为低电平。键盘编码A3 A2 A1 A0的形成见表4-25。

表4-25 键盘编码A3A2A1A0形成表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。