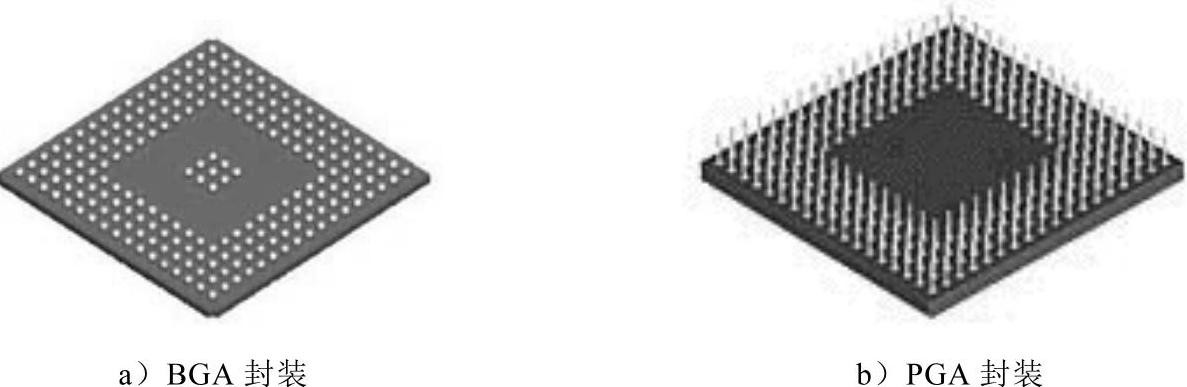

首先来认识BGA/PGA封装技术。20世纪90年代,随着集成技术的进步,设备的改进和深亚微米技术的使用,芯片集成度不断提高,对集成电路封装要求更加严格,I/O引脚数急剧增加,功耗也随之增大。当IC的频率超过100MHz时,传统封装方式可能会产生所谓的串扰(Cross Talk)现象,而且当IC的引脚数大于208时,传统的封装方式难以满足要求。因此,除使用QFP封装方式外,现今大多数的高脚数芯片,如CPU、南北桥等VLSI芯片的高密度、高性能、多功能及高I/O引脚封装的皆使用BGA(Ball Grid Array Package)封装技术,如图9-12a所示。BGA封装的特点如下:

1)BGA的I/O引脚数虽然增多,但引脚间距远大于QFP,从而提高了组装成品率。

2)虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,简称C4焊接,从而可以改善它的电热性能。

3)厚度比QFP减少1/2以上,重量减轻3/4以上。

4)寄生参数减小,信号传输延迟小,使用频率大大提高。

5)组装可用共面焊接,可靠性高。

6)信号传输延迟小,适应频率大大提高。

PGA(Pin Grid Array Package)封装也叫插针网格阵列封装技术,目前CPU的封装方式基本上均采用PGA封装,在芯片下方围着多层方阵形的插针,每个方阵形插针是沿芯片的四周,间隔一定距离进行排列的,根据引脚数目的多少,可以围成2~5圈,如图9-12b所示。它的引脚看上去呈针状,是用插件的方式和电路板相结合。安装时,将芯片插入专门的PGA插座即可。

图9-12 BGA封装和PGA封装

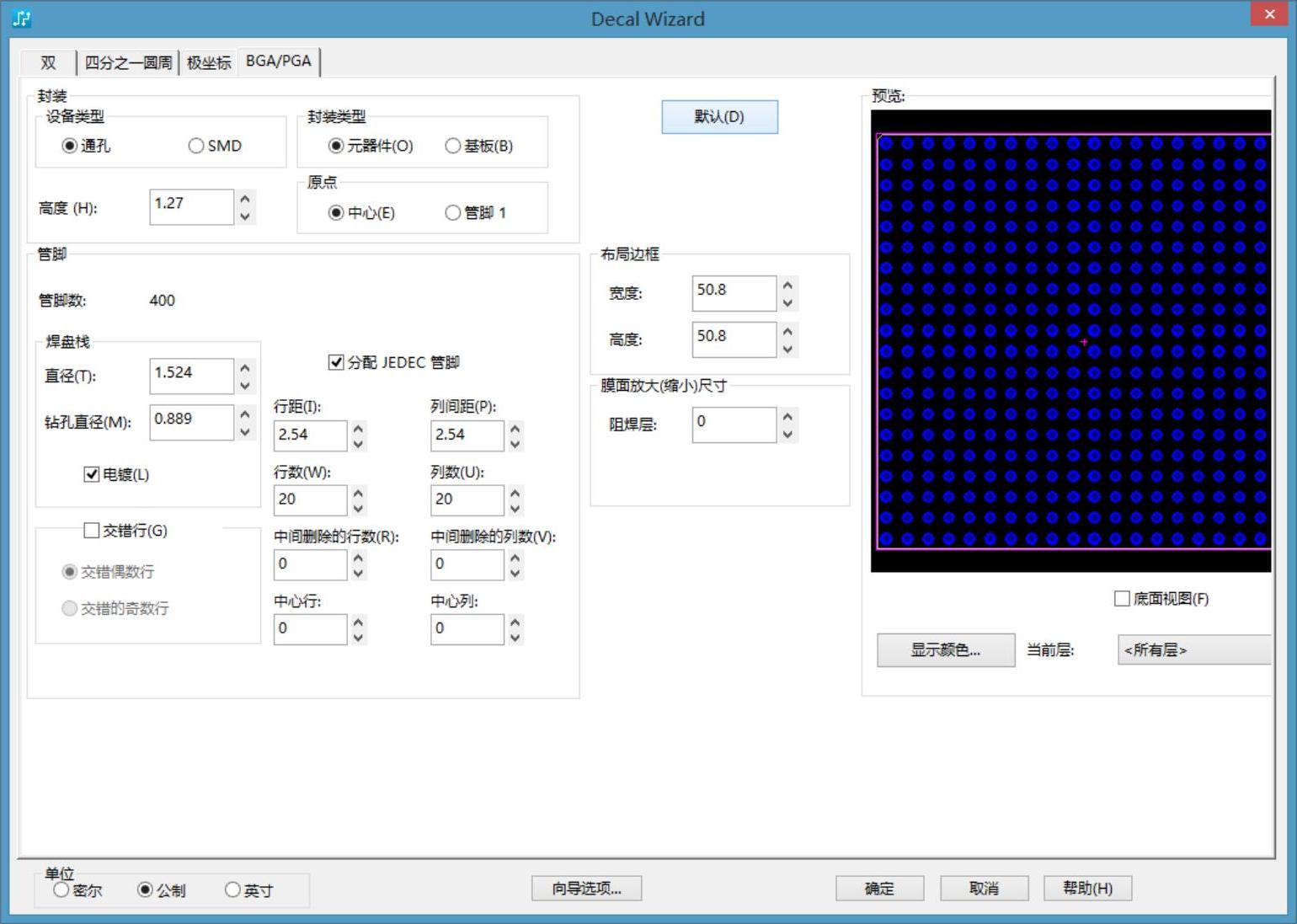

BGA/PGA封装向导如图9-13所示。

图9-13 BGA/PGA封装向导

1.“封装”选项组

(1)设备类型可选择“通孔”或“SMD”。

(2)封装类型。

1)元器件:选中该单选按钮,则元器件封装的引脚焊盘从左向右排列。

2)基板:选中该单选按钮,则元器件封装的引脚焊盘排列与选中“元器件”单选按钮时的排列互为镜像。

(3)高度输入封装的高度值,将会在PCB设计中的高度限与3D显示时生效。(https://www.xing528.com)

(4)原点该选项用于设置原点的位置。

元器件封装的引脚焊盘排列方式与图9-14所示的图标相对应。例如,选中“元器件”单选按钮,则如图9-14a所示,若选中“基板”单选按钮,则如图9-14b所示。

图9-14 引脚排列图标

2.“管脚”选项组

(1)焊盘栈

1)直径;钻孔直径(定义已经在前面讲述)。

2)电镀:选择是否镀金。

(2)交错行交错偶行或交错奇行。

(3)行距该选项用于设置引脚阵列相邻行之间的距离。

(4)列间距该选项用于设置引脚阵列相邻列之间的距离。

(5)行数该选项用于设置引脚阵列的行数目。

(6)列数该选项用于设置引脚阵列的列数目。

(7)中间删除的行数该选项用于设置引脚阵列的空行数目。如果引脚阵列的行数是偶数,则空行的数目也必须是偶数;如果引脚阵列的行数是奇数,则空行的数目也必须是奇数。

(8)中间删除的列数该选项设置参见“中间删除的行数”选项设置。但是“中间删除的列数”和“中间删除的行数”选项必须同时设置才能生成预览,可以查看设置效果,否则设置不生效。

(9)中心行该选项用于设置空行中的行数。

(10)中心列该选项用于设置空列中的列数。

(11)分配JEDEC管脚选择该选项,则PADS会根据JEDEC标准命名方法为封装的每一个引脚分配一个由数字和字母组合而成的名称。行的命名方法是当行数小于20时,以A~Y的顺序从上到下命名,但其中I、Q、S、X、Z不被使用;当行数大于20时,以AA~AY顺序从上到下命名,但其中AI、AQ、AS、AX、AZ不被使用,以此类推,当行数大于40时将以B开始。引脚阵列的列命名方法是以1开始从左向右或从右向左命名。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。