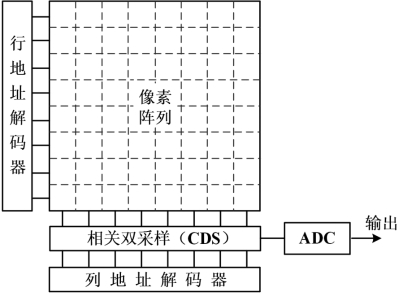

传统CMOS图像传感器的结构如图6.21所示,主要单元模块包括:像素阵列、纵向移位寄存器或行地址解码器、横向移位寄存器或列地址解码器、相关双采样电路和模拟-数字转化器(ADC)。前面几个小节对各种像素电路和相关双采样电路进行了详细讲解,下面将简单介绍寻址方案和模拟-数字转换方案。

CMOS图像传感器的每个像素是通过移位寄存器或者地址解码器进行定位的。移位寄存器可以在时钟信号的驱动下将脉冲信号依次移位,所以如果采用移位寄存器寻址,每个像素将按排列顺序依次被读取,类似一种扫描的效果。如果想要读取一个任意位置的像素,那么就必须采用地址解码器方案。地址解码器其实是一个N比特输入2N比特输出的转换器,每个像素都有唯一的一个二进制地址。通过对行地址解码器和列地址解码器输入某像素对应的二进制地址,就可以读取该像素的信号电荷。

图6.21 传统CMOS图像传感器的结构示意图

很多图像传感器具有可调分辨率的性能,它是通过改变寻址方案实现的。例如对于一个1280×960像素的图像传感器,可读取一半的像素(640×960),也可以读取1/4的像素(640×480)。在人工智能图像识别领域,为了快速识别目标,提取影像的边缘信息是关键,因此降低读取像素的数量也就意味着减少数据处理量,可加快识别速度。一旦识别到目标后,可对局部提高分辨率以获取更清晰的目标图像数据。(https://www.xing528.com)

每个像素采集的信号均是模拟信号,需要通过模拟-数字转换器变成数字信号。从ADC的角度,模数转换方案可分为芯片级ADC、列级ADC和像素级ADC。芯片级ADC是指所有像素共用同一个ADC,如图6.21所示,它的好处是所有像素的模数转换一致性高。但是它的缺点也很明显:1)由于所有像素信号都要经过这个ADC处理,这要求ADC的速度必须非常快。如果像素阵列十分庞大,芯片级ADC则很难满足其要求。2)模拟信号从像素出来到芯片级ADC,经过的路径较长,使信号更容易受到各种噪声的影响。

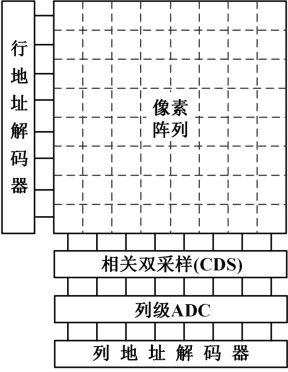

图6.22 列级ADC图像传感器的结构示意图

列级ADC是在每一列都有一个ADC,如图6.22所示,这种方案适用于高像素阵列的图像传感器。模拟信号从像素读取到纵向信号线,经过相关双采样处理后就被数字化,缩短了模拟信号行走的路径,噪声的影响被减小了。但是它也有缺点:1)由于每一列都有各自的ADC,模数转换的一致性差。2)列级ADC比芯片级ADC占用了更多的芯片面积。

像素级ADC是指在像素电路内实现模数转换,像素输出的是数字信号,如图6.23所示。这种方案模拟信号的行走路径是最短的,而且图像传感器的速度是最快的。但是因为每个像素都是自己完成模数转换的,所以其转换一致性在三种方案里是最差的。此外,像素里加入了模数转换的功能,会降低像素的填充系数。前面小节介绍的脉冲调制图像传感器就是像素级ADC的一种方案。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。