【摘要】:CMOS门电路由绝缘栅场效应管组成。因此,CMOS门电路应用广泛。CMOS非门电路如图10.2.18所示为CMOS非门电路。它是一种互补对称场效应管集成电路。其中,B1管称为驱动管,采用N沟道增强型,B2管称为负载管,采用P沟道增强型,它们制作在同一片硅片上。A端输入高电平时,B1管导通,B2管截止,Y端输出低电平。图10.2.20CMOS或非门电路及逻辑符号

CMOS门电路由绝缘栅场效应管组成。它具有静态功耗低、抗干扰能力强、扇出系数大等优点。因此,CMOS门电路应用广泛。下面介绍CMOS非门电路、与非门电路和或非门电路的工作原理。

(1)CMOS非门电路

如图10.2.18所示为CMOS非门电路。它是一种互补对称场效应管集成电路。其中,B1管称为驱动管,采用N沟道增强型(NMOS),B2管称为负载管,采用P沟道增强型(PMOS),它们制作在同一片硅片上。两管的栅极相连接并引出一端作为输入端A,两管的漏极也相连接,引出一端作为输出端Y。

A端输入高电平时,B1管导通,B2管截止,Y端输出低电平。A端输入低电平,则B1管截止,B2管导通,Y端便输出高电平。因此,如图10.2.18(a)所示电路具有非逻辑功能。其逻辑符号如图10.2.18(b)所示。

图10.2.18 CMOS非门电路及逻辑符号

(2)CMOS与非门电路(https://www.xing528.com)

如图10.2.19(a)所示为CMOS与非门电路。其中,B4与B3并联,B1与B2串联。当AB都是高电平时,B1与B2同时导通,B4与B3同时截止,输出Y为低电平;当AB中有一个是低电平时,B1与B2中有一个截止,B4与B3中有一个导通,输出Y为高电平。

图10.2.19 CMOS与非门电路及其逻辑符号

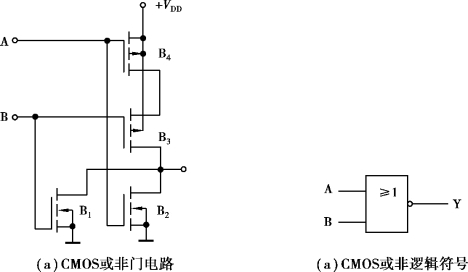

(3)CMOS或非门电路

如图10.2.20(a)所示为CMOS或非门电路。AB中有一个是高电平时,B1与B2中有一个导通,B4与B3中有一个截止,输出Y为低电平;当AB都是低电平时,B1与B2同时截止,B4与B3同时导通;输出Y为高电平。

图10.2.20 CMOS或非门电路及逻辑符号

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。