TTL集成逻辑门电路的含义是输入为三极管VT、输出为三极管VT的集成逻辑门电路,基本的TTL集成逻辑门电路是与非门,其他功能的门电路都是以与非门为基础构成。现以TTL与非门为例介绍TTL集成逻辑门电路的基本知识。

(1)TTL与非门

1)电路工作原理

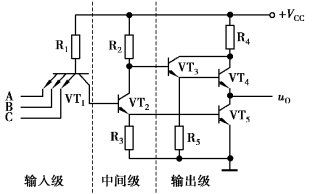

典型的TTL与非门电路如图10.2.8所示。电源电压为5 V。该电路可分为3部分:输入级、中间级和输出级。其中,VT1为多发射极晶体三极管,可对输入A、B、C实现与逻辑功能。

图10.2.8 TTL与非门电路

①输入端至少有一个为低电平

设uA为低电平(uA=0.3 V),uB、uC为高电平,那么VT1A的发射结由VCC和R1置于正偏,这时uB1=0.3 V+0.7 V=1 V,VT2、VT5截止,uB3≈5 V,足以使VT3、VT4导通,输出uO≈5 VuBE3-uBE4=3.6 V,为高电平,即实现有0出1的功能。

②输入端全为高电平(3.6 V)

设A、B、C端都为高电平(3.6 V),这时VT2、VT5饱和导通,VT1发射极反向偏置,集电结正向偏置,处于倒置状态。VT2的集电极电位uC2=uCES2+uBE5≈0.3 V+0.7 V=1 V,该电压值不可以使VT3、VT4导通。因此,输出uO为低电平,即实现全1出0的功能。

可知,如图10.2.8所示电路实现的是与非逻辑关系。

2)电压传输特性

TTL与非门电压传输特性是指在空载的条件下,输入电压uI与输出电压uO之间的关系曲线。如图10.2.9(a)、(b)所示为电压传输特性测试电路和特性曲线。

①截止区(AB段)

当0V<uI<0.6 V,VT2和VT5管均截止,VT3、VT4导通,uO为高电平3.6 V。

②线性区(BC段)

当0.6 V<uI<1.2 V,uO随着uI增大而线性地降低。

③转折区(CD段)

当1.2 V<uI<UTH,VT5管迅速饱和,uO急剧下降到低电平0.3 V。其中,UTH称为阈值电压,是指VT5管截止和导通分界线时对应的输入电压,即输出电压由高电平转变为低电平所对应的输入电压。TTL与非门的阈值电压约为1.4 V。

④饱和区(DE段)

当uI>UTH以后继续增加,VT5管的饱和深度加深,uO已基本不变。

图10.2.9 TTL与非门电压传输

3)TTL与非门的使用特性

①输出高电平电压UOH和输出低电平电压UOL

TTL与非门输出高电平典型值为3.6 V,大于等于2.4 V为合格;输出低电平典型值为0.3 V,小于等于0.4 V为合格。

②输入噪声容限

输入噪声容限是说明与非门抗干扰能力的参数。噪声容限电压值越大,与非门的抗干扰能力越强。

A.低电平噪声容限电压UNL

保证输出为高电平电压所允许叠加在输入低电平电压上的最大干扰电压。UNL越大,说明门电路输入低电平时抗正向干扰的能力越强,即

![]()

式中,UOFF称为关门电平,是输出电压为高电平下限值时所对应的输入电压。

B.高电平噪声容限电压UNH

保证输出为低电平电压所允许叠加在输入高电平电压上的最大干扰电压。UNH越大,说明门电路输入高电平时抗负向干扰的能力越强,即

![]()

式中,UON称为开门电平,是输出电压为低电平上限值时所对应的最小输入电压。

③输入高电平电流IIH和输入低电平电流IIL

当某一输入端接高电平,其余输入端接低电平时,流入该输入端的电流,称为高电平输入电流IIH(μA)。

当某一输入端接低电平,其余输入端接高电平时,流出该输入端的电流,称为低电平输入电流IIL(mA)。

④输入负载特性

在实际应用中,门电路的输入端常经过一个电阻接地,这个电阻称为输入电阻RI。保证输出为标准高电平USH时所对应的输入端外接电阻RI的最大值,称为关门电阻。一般选关门电阻RI≤0.9 kΩ;保证输出为标准低电平USL时所对应的输入端外接电阻的最小值,称为开门电阻,用RON表示。在实际应用中,一般选开门电阻RON≥2.5 kΩ。

⑤扇出系数NO

它是指一个与非门能带同类门的最大数目,是表示与非门带负载的能力参数。对TTL与非门,NO≥8。

⑥平均传输延迟时间tpd

规定从输入电压上升到高电平的50%开始到输出电压下降到高电平的50%的时间间隔,称为导通传输延时时间tPHL;从输入电压下降到高电平的50%开始到输出电压上升到高电平的50%的时间间隔,称为截止传输延时时间tPLH。平均传输延迟时间tpd为

![]()

如图10.2.10所示为TTL与非门延迟时间的输入输出电压波形。TTL与非门的tpd在10~40 ns,此值越小越好。

(https://www.xing528.com)

(https://www.xing528.com)

图10.2.10 TTL与非门输入输出电压波形

4)TTL与非门的应用举例

①控制脉冲信号传输

【例10.2.1】 已知与非门电路两个信号输入端A、B的波形如图10.2.11所示,试画出与非门输出![]() 的波形。

的波形。

解 画输出波形时,对应输入波形A、B的变化分段讨论,运用对应逻辑关系得出结果。

当B=0时,![]() ,即Y恒为1,A信号不能通过,与非门关闭;当B=1时,

,即Y恒为1,A信号不能通过,与非门关闭;当B=1时,![]() ,输出Y的波形与

,输出Y的波形与![]() 相同,即与非门开门,

相同,即与非门开门,![]() 信号能顺利通过与非门,从Y输出。因此,可得输出Y的波形如图10.2.11所示。

信号能顺利通过与非门,从Y输出。因此,可得输出Y的波形如图10.2.11所示。

图10.2.11中,A端为信号输入端,B端为控制端。由上述分析可知,与非门除能完成一定的逻辑功能外,还可作为控制元件,控制信号的通断。

图10.2.11 例10.2.1图

②组成其他功能的门电路

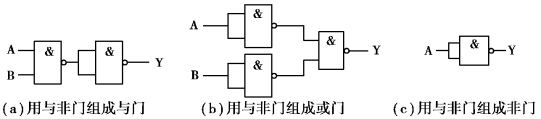

由与非门可组成其他功能的门电路,如图10.2.12所示。此外,还可用与非门组成异或门和同或门。

图10.2.12 用与非门组成其他功能的门电路

(2)其他类型的TTL与非门

1)集电极开路的与非门(OC门)

两个或多个普通与非门的输出端直接相连,相当于将这些输出信号相与,称为线与。线与连接时,TTL与非门电路将可能出现输出级电流过大的危险。因此,不允许TTL与非门电路输出直接线与连接。为解决两个或多个门电路输出端线与的问题,可将输出级改为集电极开路的三极管结构,做成集电极开路门电路,简称OC门。

①OC门的电路结构

图10.2.13 集电极开路的与非门

如图10.2.13(a)所示为一个典型的集电极开路与非门电路。它与普通的TTL与非门的主要区别在于用外接电阻R4代替由VT3、VT4组成的复合管。如图10.2.13(b)所示为OC门的逻辑符号。

②OC门的应用

A.实现线与

用若干个集电极开路与非门接成线与的逻辑电路如图10.2.14所示。RC为外接共用电阻。当其中一个OC门,如OC1门的输入端A1和B1都为1,而OC2、OC3都有输入端为0时,则OC1的输出管VT5导通,OC2、OC3的输出管都截止,负载电流将全部流入OC1的VT5,但只要RC足够大,OC1的VT5就可以饱和,Y1即为低电平,Y也为低电平。

若如图10.2.14所示电路中的每个OC门的输入都有低电平时,它们的输出管均截止,Y为高电平。综上所述,可得Y=Y1·Y2·Y3,即实现了线与。

B.控制执行机构

利用OC门可控制一些较大电流的执行机构,用OC门和三极管VT控制电动机的电路,如图10.2.15所示。当OC门输入为1时,其输出为0,这时VT处于饱和导通状态,继电器线圈得电,触点闭合,电动机处于运转状态;当OC门输入为时0,其输出为1,VT截止,继电器线圈失电,触点断开,电动机处于停止状态。线圈两端并联的二极管起保护作用。

图10.2.14 OC门实现线与

图10.2.15 OC门驱动控制机构

2)三态输出与非门

三态门的输出除了有一般门电路的两种状态(即高电平和低电平状态)外,还具有高阻态。

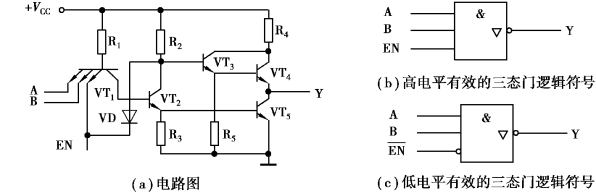

①三态门的工作原理

如图10.2.16(a)所示的电路是三态与非门。它的逻辑符号如图10.2.16(b)所示,EN为控制端,又称使能端,A、B为输入端,L为输出端。

当EN=0时,二极管VD处于导通状态,VT3的基极电位被二极管VD箝位在1 V左右,VT2、VT5、VT3、VT4均截止,这时输出端与门电路内部呈高阻状态或称悬空状态。EN=1时,二极管VD截止,三态门与普通TTL与非门的工作情况相同,输出和输入之间逻辑关系为

![]()

图10.2.16 三态输出与非门

另一种三态门在控制端EN为高电平时禁止,为低电平时正常工作。逻辑符号如图10.2.16(c)所示。其中,EN端的小圆圈表示使能端低电平有效。

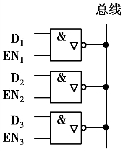

②三态门的应用

图10.2.17 三态门应用于总线

三态门主要用于总线传输。例如,有3路数据D1、D2、D3经三态门与总线连接,如图10.2.17所示。当某一路数据(D1)需要传输到总线上时,对应的三态门的使能端EN1加有效电平高电平,而其他三态门的EN端则加低电平,使它们的输出处于高阻状态,不与总线产生电信号联系,从而保证D1在总线上传输。

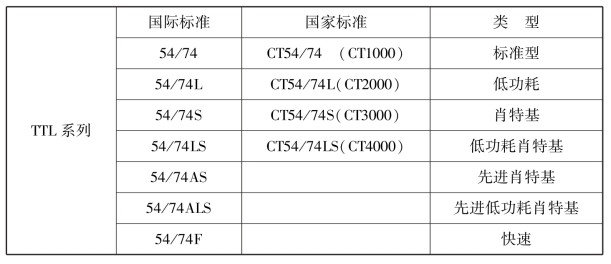

(3)TTL集成电路分类

TTL集成逻辑门使用时,应注意电源电压及电源干扰的消除。电源电压的变化对54系列应满足5 V±10%、对74系列应满足5 V±5%的要求。

有多余或暂时不用的输入端时,可将不用的输入端并联起来。这种处理方法不会影响电路的逻辑功能,可提高电路工作的可靠性,但会增加前级门的负载。此外,与门和与非门多余的输入端可以悬空(但这样容易使输入端受干扰信号的影响),也可将通过1 kΩ的限流电阻接至电源VCC上。或门和或非门的多余输入端可以接地。

表10.2.4 TTL门电路系列产品

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。