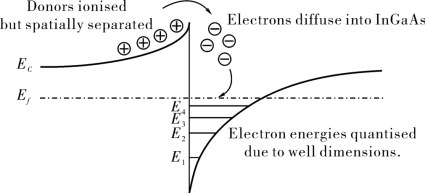

调制掺杂是指宽禁带半导体一边掺杂、而窄禁带半导体一边不掺杂。由于量子效应,在垂直异质结界面方向上能量量子化,形成不连续的量子化能级。宽带一侧电子转移到量子阱中,按照最低能级向上填充使得电子连续不断填充未被占据的最小的能级。由于势阱的尺寸不均匀,导致导带平缓弯曲,随着势阱的尺寸变宽分离能级靠的越近,如图2.3所示。然而,在平行异质结界面的平面内,能量是连续的。

图2.3 异质结界面量子阱中2DEG 图

从量子论知道,垂直于界面方向的电子被限制,而在二维平面方向的电子可以自由运动。这些在二维平面方向自由运动的电子称为二维电子气(2DEG)。宽禁带的AlSb势垒层重掺杂,而InAs势阱中没有掺杂,形成调制掺杂结构,被Dingle等人第一次提出来,AlSb势垒层中电子转移到没有掺杂的InAs势阱中,在InAs层中形成2DEG,这样二维电子气和电离施主杂质在空间上是分开的,减少了电离杂质散射对载流子运动的影响,最终使得势阱中电子的迁移率有很大提高。调制掺杂最大的贡献在于能同时得到高浓度和高迁移率的载流子,这是普通掺杂无法实现的。调制掺杂的HEMT 器件都有未掺杂的空间势垒层(Space layer),如图2.3所示,空间势垒层的作用就是把沟道电子和电离施主杂质分开,这样减少电离施主杂质对沟道电子的散射影响,从而提高HEMT 器件沟道中二维电子迁移率,提高HEMT 器件频率特性。尽管空间势垒层能把电离施主杂质和二维电子气在空间上分开,提高电子迁移率,但是空间势垒层的厚度也直接影响2DEG 面电子的浓度和迁移率。(https://www.xing528.com)

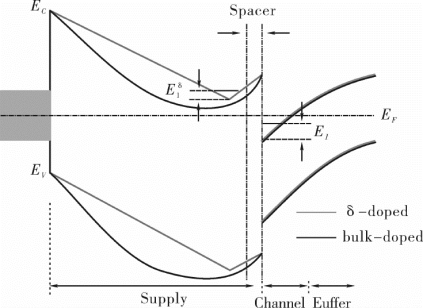

一般讲的掺杂是体掺杂,整个材料中都有掺入的杂质。随着提高掺杂性能的需求面掺杂技术应用而生。面掺杂是δ掺杂,指平面的原子层掺杂。在一个单原子层内高掺杂(ND>5×1012cm-2)的半导体构成面掺杂的半导体。图2.4描述了体掺杂和δ面掺杂的能带图和量子阱。δ面掺杂和体掺杂的能带图中,Eδ1 是指δ面掺杂区域的量子化能级,E1指量子阱中的量子化能级。当Eδ1 低于费米能级EF 时,在调制掺杂区形成一个平行的导电沟道。如果通过内建电场或外部电场还没有完全耗尽,那这个平行的导电沟道对2DEG 来讲是不希望出现的部分。同样,在体掺杂结构中,如果导带的最低能量低于费米能级EF ,则平行的导电沟道也会出现,同样是在HEMT器件中不希望发生的现象。

图2.4 体掺杂和δ面掺杂异质结形成2DEG 能带图

图2.4显示了体掺杂和面掺杂能带的弯曲趋势相同,使得沟道中有相似的载流子浓度。与体掺杂相比,同样杂质浓度,面掺杂能得到更高的载流子浓度。也就是说,与体掺杂相比,得到相似二维电子气浓度的面掺杂只需要较少的施主杂质。δ面掺杂的优点是面掺杂可以使导带底部最小能量提高,最终避免不希望出现的平行导电沟道产生。从图2.4可看到,面掺杂外延中产生的较高的载流子浓度更容易越过薄的空间势垒区的斜坡,而体掺杂耗尽区中电势下降,导致体掺杂中电子相比越过薄空间势垒区难度变大。由于空间势垒层很薄,也认为δ面掺杂的电子可以隧穿到势阱沟道里面,增加了量子阱中载流子浓度。所以,在HEMT 器件设计中面掺杂是一步关键设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。