半导体异质结是不同半导体材料形成的交界面,是形成许多器件的基本要素,包括半导体激光器、发光二极管(LED)、异质结双极晶体管(HBTs)、高电子迁移率晶体管(HEMTs)和共振遂穿二极管(RTDs)等。随着外延生长技术的逐渐成熟,半导体异质结器件的发展也非常迅速。

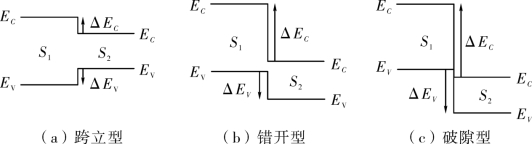

当两种不同禁带宽度的半导体材料形成异质结,在交界面处两种材料之间的导带和价带就会不连续。导带和价带不连续处的能量差称为导带带阶和价带带阶,分别记为ΔEc和ΔEv。在没有外加偏压时,由于异质结两边半导体具有统一的费米能级,电子将从宽带隙的半导体转移到窄带隙的半导体。电子的转移使得窄带隙半导体的导带能带发生弯曲,导带底的不连续和弯曲就形成了量子阱。根据两种半导体材料S1和S2的不同性质,不同的禁带宽度和电子亲和势,形成三种类型的异质结:type-Ⅰ跨立型,type-Ⅱ错开型,type-Ⅲ破隙型,能带结构如图2.1所示。

图2.1 三种类型异质结的能带图

Ⅲ族元素(In,Al,Ga)和V 族元素(Sb,As等)形成锑基化合物半导体(ABCS)。这些材料的晶格常数在6.1Å 附近,通常锑基化合物半导体材料也称为“6.1Å 族”。InAs/AlSb异质结是由大禁带宽度1.60eV 的AlSb势垒层和小禁带宽度0.36eV 的InAs沟道材料组成。InAs/AlSb形成type-Ⅱ错开型异质结,并且在Ⅲ-Ⅴ族异质结中有最大的导带带隙ΔEc(~1.35eV),这样深的势阱对电子有很好的限制作用。1990年,美国加利福尼亚大学Herbert Kroemer教授第一次宣布高电子迁移率InAs/AlSb异质结形成。Dandrea等人报道,InAs和AlSb之间1.6%的晶格失配产生应力使得两种材料价带之间有大约0.04~0.10eV 之间的价带带阶。(https://www.xing528.com)

图2.2 type-Ⅱ错开型InAs/AlSb量子阱

AlSb/InAs/AlSb量子阱很大的ΔEc有利于限制电子在沟道中运动,即使在非有意掺杂的势阱中,由于很高的ΔEc,势阱中面载流子浓度大于3×1011cm-2。为得到高的2DEG 面电子密度采用调制掺杂结构,这样把电子和施主电离杂质在空间上分开,减小了施主杂质的散射影响,使得势阱中电子迁移率提高很多。InAs沟道材料是窄禁带宽度的材料,很容易产生大量的空穴。从图2.2可知,InAs沟道材料的价带比AlSb材料低,那么这些空穴容易越过势垒流走,这就引起InAs/AlSb HEMT 器件产生大的栅漏电流,这也引起关注在制造InAs/AlSbHEMT 器件中要重点考虑如何通过改变结构来减小栅极漏电流的问题。

AlSb/InAs/AlSb量子阱中电子迁移率不仅与电子面密度有关而且与量子阱的宽度也有很大关系。据报道,材料的面密度和势阱宽度的最佳值分别是1.5×1012cm-2和15nm。太窄的势阱会使得电子迁移率减小,因为增大了界面粗糙度散射,然而势阱的宽度大于15nm 时,电子迁移率也会减小,由于子带间散射的影响。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。