【摘要】:但由同一电源供电的低压系统,不宜同时采用上述两种系统。

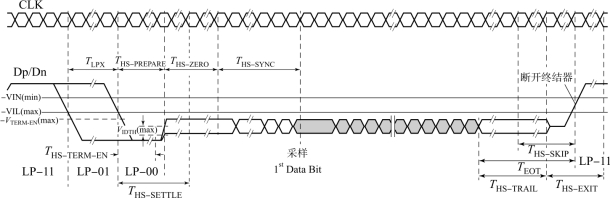

发送DSC传输请求后,数据通道将离开停止状态并通过开始传输(SoT)过程来准备高速模式。在数据突发结束时,数据通道保持高速传输模式并通过传输结束(EoT)过程进入停止状态。所以在实际的高速数据传输过程中,通道信号的判断电平是随着指令和数据的切换而在不断改变。图5.25和图5.26显示包括SoT和EoT的高速数据传输的顺序。

图5.25 突发高速数据传输原理示意图

(https://www.xing528.com)

(https://www.xing528.com)

图5.26 突发高速数据传输实测波形图

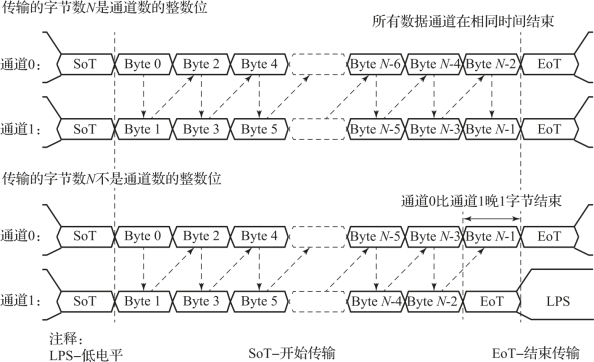

实际传输过程中,经常使用多个物理通道,一般情况下串行数据会先缓存至主处理器发送DSI接口,然后在通道控制器的作用下,按照通道分布顺序拆分,并行发送至各个通道;MIPI从设备从MIPI通道并行接收数据,并按照通道顺序将数据合并组合传送至DSI接口,供下一级电路处理,MIPI接口2通道数据传输原理示意图如图5.27所示。所以通道数越多,数据传送越快,例如某个MIPI设备单个通道数据传输速度为1 Gb/s,拥有4个通道,那么该设备的传输速率达4×1 Gb/s=4 Gb/s。本次驱动器的MIPI接口电路设计时,为了系统稳定性和结构去复杂性,就选用了一款数据传输速度为4×1 Gb/s的MIPI主桥芯片。目前,高通公司针对VR推出的新一代芯片的MIPI接口传输总速度可达60 Gb/s。

图5.27 MIPI接口2通道数据传输原理示意图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。