1.寄存器

寄存器是用来存放数据的一种时序逻辑电路,被广泛应用于各类数字系统和计算机中。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。

对寄存器中的触发器只要求它们具有置1、置0的功能即可,因而无论是用SR锁存器,还是用D触发器或者JK触发器,都可以组成寄存器。由于D触发器既简单又具备置1、置0功能,所以寄存器一般由D触发器组成。寄存器有公共输入/输出端、使能控制端和时钟信号输入端。一般把使能控制端作为寄存器电路的选择信号,把时钟信号作为数据输入控制信号。

2.基本寄存器

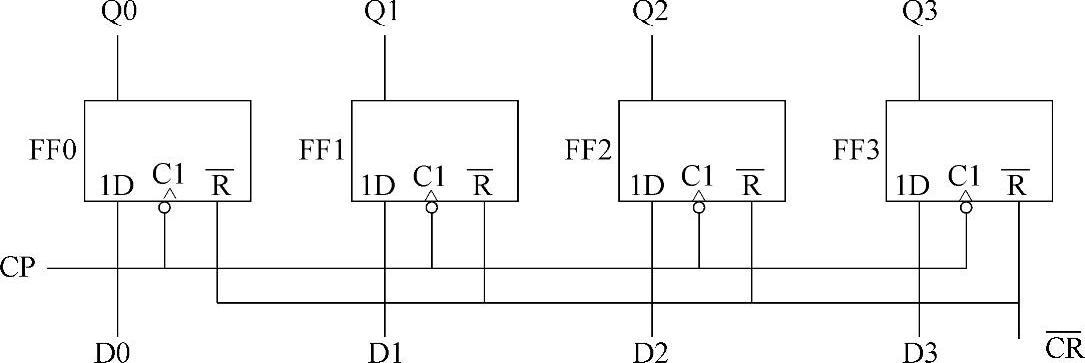

基本寄存器电路如图5-31所示。图中共有4个D触发器,所以能寄存4位二进制代码。图中CR为置0输入端,D3~D0为并行数码输入端,Q3~Q0为并行数码输出端。

图5-31 基本寄存器电路

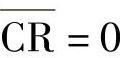

当时钟信号CP处于下降沿时,输出端Q3Q2Q1Q0=D3D2D1D0,属于数据更新功能;当 时,输出端Q3Q2Q1Q0=0000,属于清零功能;除这两种情况外,寄存器的输出Q3Q2Q1Q0保持不变时,属于存储功能。

时,输出端Q3Q2Q1Q0=0000,属于清零功能;除这两种情况外,寄存器的输出Q3Q2Q1Q0保持不变时,属于存储功能。

3.移位寄存器

移位寄存器是具有移位功能的寄存器。寄存器只有寄存数据或代码的功能,有时为了处理数据,需要将寄存器中的各位数据在移位控制信号作用下,依次向高位或向低位移动1位。移位寄存器按数码移动方向分类有左移、右移、可控制双向(可逆)移位寄存器;按数据输入端、输出方式分类有串行和并行之分。除了D边沿触发器构成移位寄存器外,还可以用JK触发器等构成移位寄存器。

所谓串行是指在一条信号线上依次传递数据的各个位,这种方法的优点是节省导线,适合远距离传输,一般电话线、网线都是采用串行传输的方式。而并行是指用多条信号线同时传递数据的各个位,这种方法需要多条导线,只适合短距离传输,计算机内部的数据总线、地址总线都是并行传输的方式。

数据寄存功能只是移位寄存器的基本功能,移位寄存器经常用于串行/并行转换工作,除此之外,由于二进制数据左移一位相当于乘以2,右移一位相当于除以2,所以,移位寄存器还经常用于数据的乘除法运算。(https://www.xing528.com)

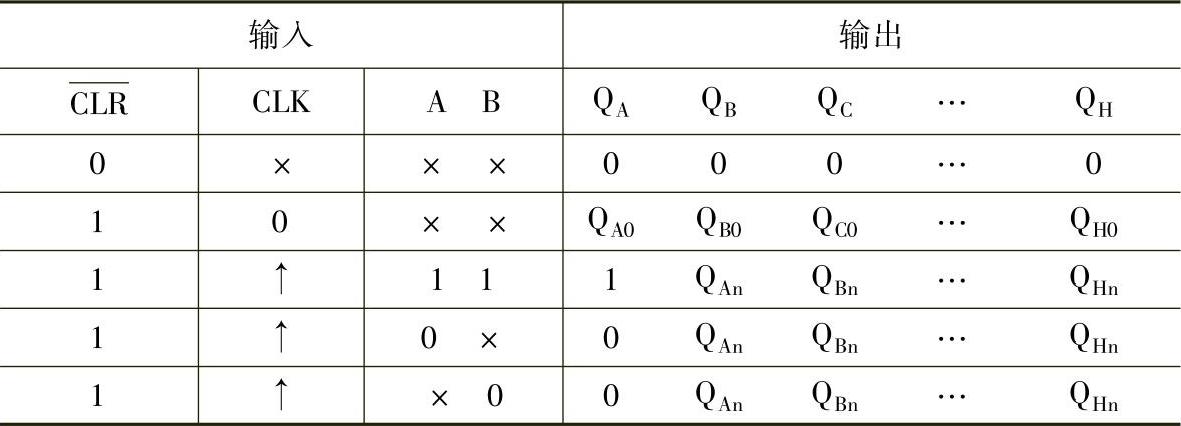

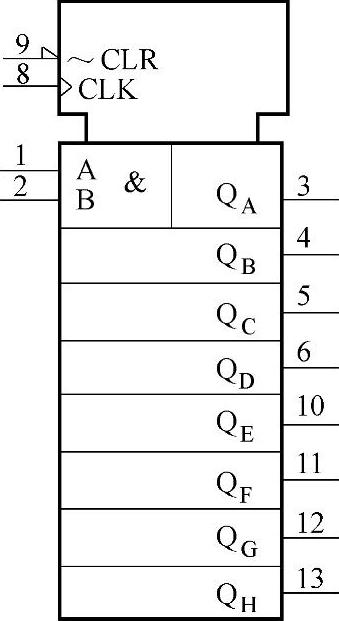

图5-32是8位移位寄存器74LS164的逻辑符号,表5-20是74LS164的功能表。74LS164能够从QA向QH方向移位,补充在QA的数据由A和B决定,A、B同时为1时,补充1,否则补充0。

表5-20 74LS164功能表

图5-32 74LS164的逻辑符号

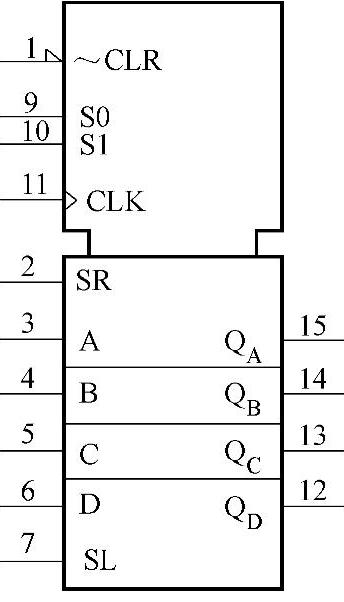

图5-33是四位双向移位寄存器74LS194的逻辑符号,表5-21是74LS194的功能表。74LS194能够实现数据的寄存和双向移位功能,S1S0=00时为保持功能,输出保持不变;S1S0=01时右移,从QA向QD方向移位,补充在QA的数据由SR决定;S1S0=10时左移,从QD向QA方向移位,补充在QD的数据由SL决定;S1S0=11时为并行输入功能,QDQCQBQA=DCBA。清零功能为异步低电平清零。

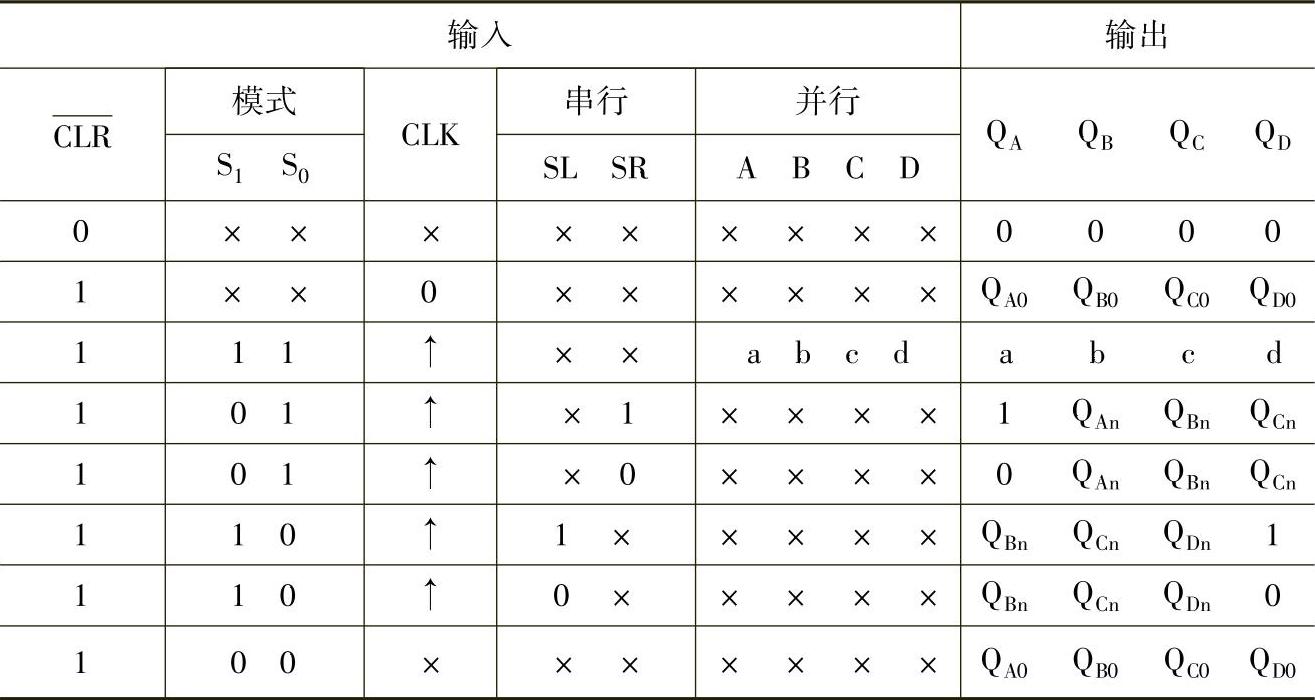

表5-21 74LS194功能表

图5-33 74LS194的逻辑符号

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。