SR锁存器有时也被称为RS触发器。SR锁存器分为基本SR锁存器和门控SR锁存器两类。其中,基本SR锁存器是各种锁存器和触发器的基本单元,也常用在按钮或开关的消抖电路中;门控SR锁存器单独应用较少,一般在作为集成触发器内部结构出现。

基本SR锁存器包括两种电路结构,即或非门SR锁存器和与非门SR锁存器。它们都有反馈,通过反馈的自我保持作用实现记忆功能。

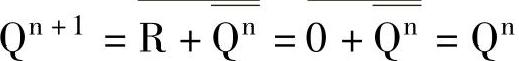

1.或非门SR锁存器

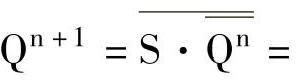

(1)电路分析 如图5-17所示,当S和R同时为1时, ,出现了原变量等于反变量的情况,违背了逻辑学的基本逻辑关系,所以,使用时要注意避免S和R同时为1的情况;当S=1且R=0时,可知Q=1且

,出现了原变量等于反变量的情况,违背了逻辑学的基本逻辑关系,所以,使用时要注意避免S和R同时为1的情况;当S=1且R=0时,可知Q=1且 ,称锁存器为1状态;当S=0且R=1时,Q=0且

,称锁存器为1状态;当S=0且R=1时,Q=0且 ,称锁存器为0状态;当S和R同时为0时,

,称锁存器为0状态;当S和R同时为0时, 且

且 ,锁存器为保持(记忆)功能。

,锁存器为保持(记忆)功能。

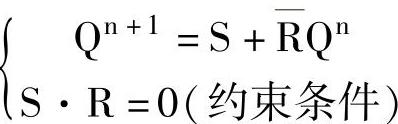

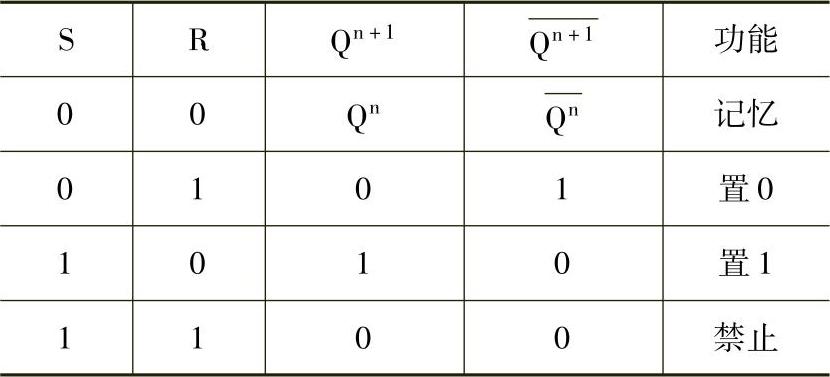

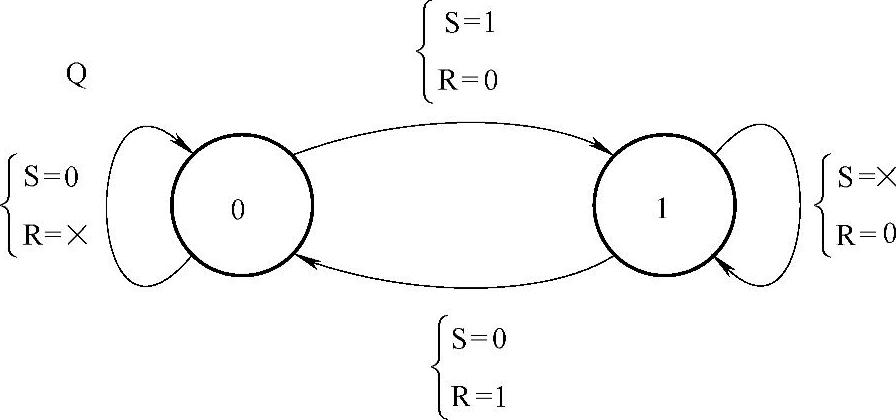

根据前述分析,可得或非门SR锁存器的功能表,见表5-14。

图5-17 或非门SR锁存器

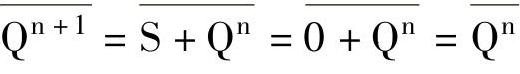

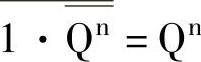

根据表5-14可得或非门SR锁存器逻辑表达式为

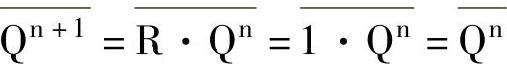

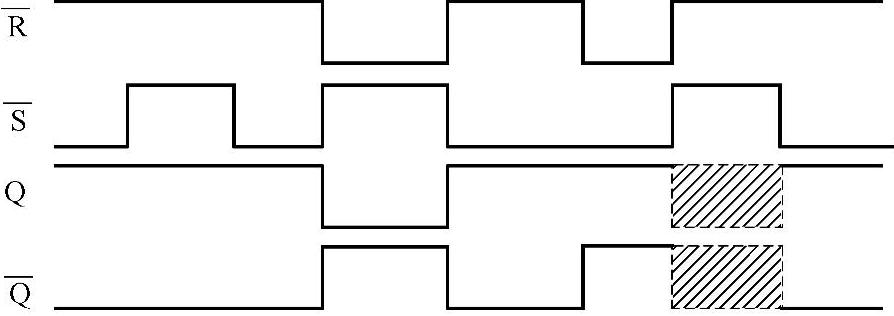

(2)时序图分析 如图5-18所示。从图中可以看出,当锁存器不是处于记忆功能时,输出状态随时受到输入的影响,因此,当输入受到干扰时,输出容易发生错误。

表5-14 或非门锁存器功能表

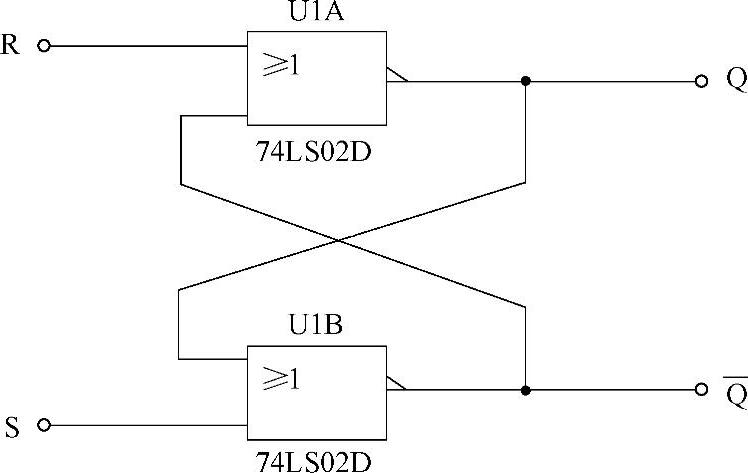

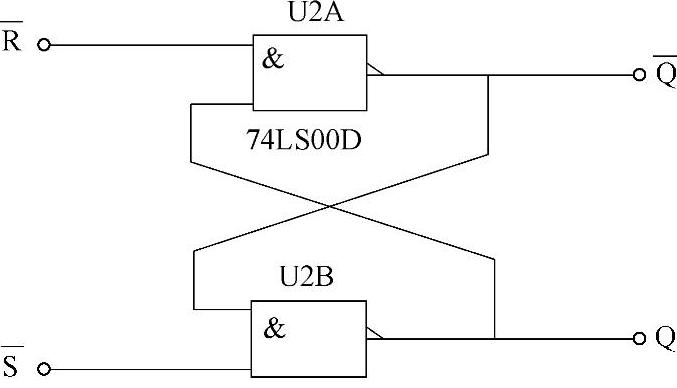

2.与非门SR锁存器

(1)电路分析 如图5-19所示,两个输入端分别为 和

和 ,对应的输出端分别为Q和

,对应的输出端分别为Q和 。当

。当 和

和 同时为0时,

同时为0时, ,也出现了原变量等于反变量的情况,违背了逻辑学的基本逻辑关系,所以,使用与非门SR锁存器时也要注意避免

,也出现了原变量等于反变量的情况,违背了逻辑学的基本逻辑关系,所以,使用与非门SR锁存器时也要注意避免 和

和 同时为0的情况;当

同时为0的情况;当 且

且 时,可知Q=1且

时,可知Q=1且 ,锁存器为1状态;当

,锁存器为1状态;当 且

且 时,Q=0且

时,Q=0且 ,锁存器为0状态;当

,锁存器为0状态;当 和

和 同时为1时,

同时为1时,

且

且 ,锁存器为保持(记忆)功能。

,锁存器为保持(记忆)功能。

图5-18 或非门锁存器时序图

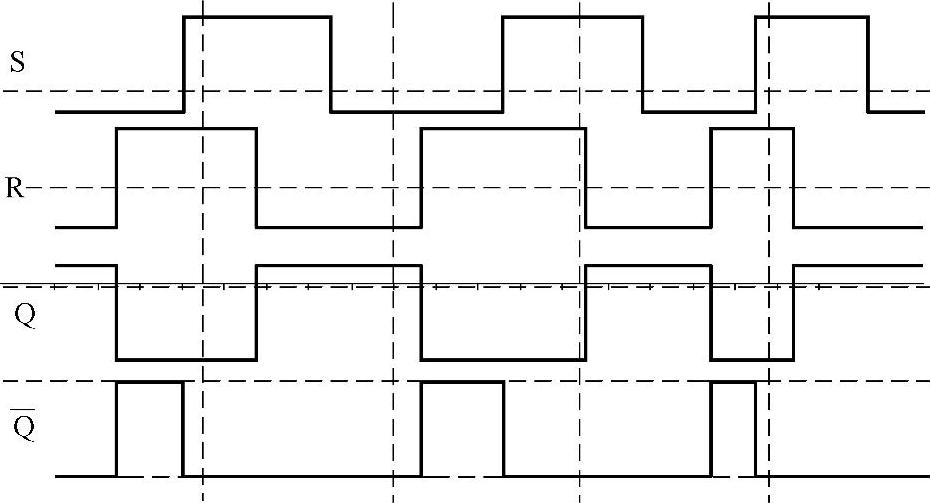

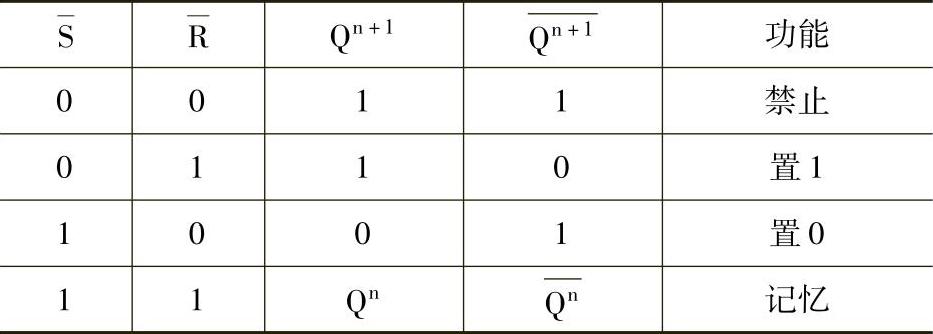

根据前述分析,可得与非门SR锁存器的功能表,见表5-15。如果将表5-15中的S和R的反变量写成原变量,对应的0和1取反,可以发现其与表5-14极为相似,区别仅仅是在违反约束条件时的Q的结果不同。

表5-15 与非门SR锁存器功能表(https://www.xing528.com)

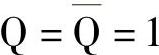

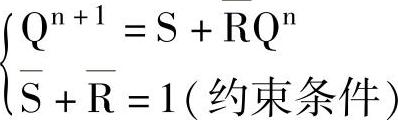

根据表5-15可得与非门SR锁存器逻辑表达式为

图5-19 与非门SR锁存器

注意:将与非门锁存器和或非门锁存器的逻辑表达式进行比较,可以发现两者是等价的,它们的约束条件可以通过摩根定理进行转换。类似的,一种逻辑功能的锁存器或者触发器可能有不同的多种电路结构或触发形式。

(2)时序图分析 与非门SR锁存器时序图如图5-20所示。

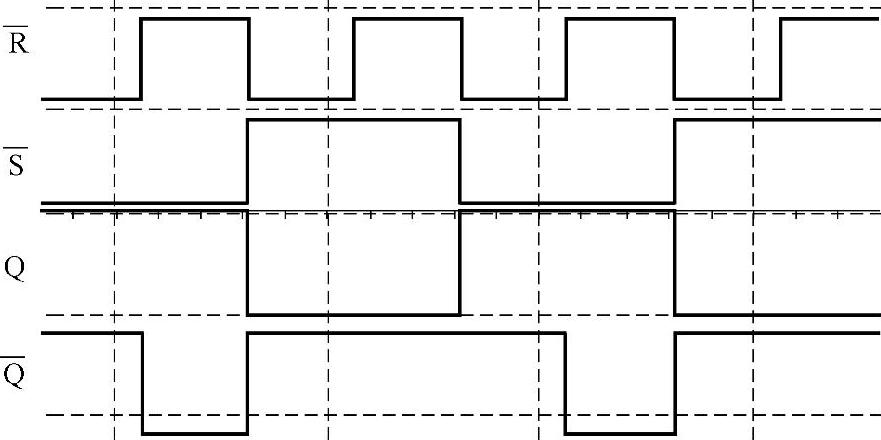

3.状态转换图和使用注意事项

(1)状态转换图 状态转换图是时序逻辑电路中常用的工具,在圆圈中写入状态,箭头表示状态转换的方向,转换条件写在箭头的旁边。SR锁存器的状态转换图如图5-21所示。

(2)注意事项 如果有某些特殊原因会导致SR锁存器两个输入端同时有效(违背约束条件)时,输出是确定的,而且有Q=Q;但是,在脱离同时有效时,如果两个输入端的输入信号同时跃变为无效,则由于门电路的延迟时间不同,输出有可能是1状态,也可能是0状态,如图5-22中阴影部分所示。对于某连接好的实际SR锁存器,由于两个集成电路的延时长短是确定的,所以输出是确定的0状态或者确定的1状态,也就是说,实际SR锁存器的输出是确定的,但需要实际测试。因此,更换集成电路或者生产多个产品时,无法保证其输出状态到底是什么,而实际生产产品时,必须保证所有产品的一致性,所以在用SR锁存器设计电路时,必须考虑到这个问题,如果不能容忍这种情况,就需要选择其他种类的锁存器或者触发器。当两个输入信号从同时有效到先后退出有效时,则没有这个问题,分别按照置0或置1功能执行。

图5-20 与非门SR锁存器时序图

图5-21 SR锁存器状态转换图

图5-22 SR锁存器的特殊问题

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。