TTL电路和CMOS电路的电气参数有所不同,需要分别叙述。

1.TTL电路

(1)特点

1)输入端一般有钳位二极管,减少了反射干扰的影响。

2)输出电阻低,增强了带容性负载的能力。

3)有较大的噪声容限。

4)采用+5V的电源供电。

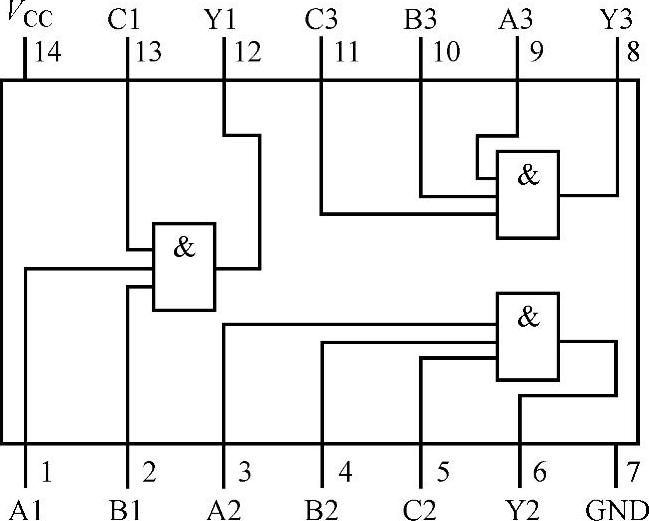

图5-7 74LS11各引脚逻辑功能分配

为了正常发挥器件的功能,应使器件在推荐的条件下工作。对于74LS系列电路,其工作条件是:

1)电源电压应在4.75~5.25V的范围内。

2)环境温度为0~70℃。

3)高电平输入电压VIH>2V,低电平输入电压VSL<0.8V。

4)输出高电平电流应小于400μA,输出低电平电流小于8mA。

5)工作频率不能高,典型低电平到高电平传输延迟时间为15ns,高电平到低电平传输延迟时间为12ns,最高工作频率约为33MHz。

(2)使用注意事项

1)电源电压应严格保持在5V±0.5V的范围内,过高易损坏器件,过低则不能正常工作。试验中,一般采用稳定性好、内阻小的直流稳压电源。使用时,应特别注意电源与地线不能错接,否则会因过大电流而造成器件损坏。

2)多余输入端最好不要悬空,虽然悬空相当于高电平,并不能影响与门(与非门)的逻辑功能,但悬空时易受干扰,为此,与门、与非门多余输入端可直接接到Vcc上,或通过一个公用电阻(几千欧姆)连到Vcc上。若前级驱动能力强,则可将多余输入端与使用的输入端相接;不用的或门、或非门输入端直接接地,与或非门不用的与门输入端至少有一个要直接接地,带有扩展端的门电路,其扩展端不允许直接接电源。若输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态,当R≤680Ω时,输入端相当于逻辑“0”;当R≥1.4kΩ时,输入端相当于逻辑“1”。

3)输出端不允许直接接电源或接地,不允许将输出不同信号的输出端直接连接使用(集电极开路门和三态门除外)。

4)应考虑电路的负载能力(即扇出系数),要留有余地,以免影响电路的正常工作。

5)在高频工作时,应通过缩短引线、屏蔽干扰源等措施来抑制电流的尖峰干扰。

6)当外加输入信号边沿变化很慢时(上升沿或下降沿小于50~100ns/V),必须加整形电路进行改善。

2.CMOS电路

(1)特点

1)静态功耗低。电源电压VDD=5V的中规模电路的静态功耗小于100μW,这样有利于提高集成度和封装密度,降低成本,减小电源功耗。

2)电源电压范围宽。电源电压可在3~18V范围内任取,从而使选择电源的余地很大,电源设计要求低。

3)输入阻抗高。正常工作的CMOS电路,其输入端保护二极管处于反偏状态,直流输入阻抗可大于100MΩ,在工作频率较高时,应考虑输入电容的影响。(https://www.xing528.com)

4)扇出能力强。在低频工作时,一个输出端可驱动50个以上的CMOS器件的输入端,这主要是因为CMOS器件的输入电阻高的缘故。

5)抗干扰能力强。CMOS电路的电压噪声容限可达电源电压的45%,而且高电平和低电平的噪声容限值基本相等。

6)逻辑摆幅大。空载时,输出高电平VOH>(VDD-0.05V),输出低电平VOL<(VSS+0.05V)。

CMOS电路还有较好的温度稳定性和较强的抗辐射能力。不足之处是,CMOS4000系列的工作速度比TTL集成电路低,电平变化传输延长时间至少要90ns,功耗随工作频率的升高而显著增大。

CMOS器件的输入端和VSS之间接有保护二极管,除了电平变换器等一些接口电路外,输入端和正电源VDD之间也接有保护二极管,因此,在正常运转和焊接CMOS器件时,一般不会因感应电荷而损坏器件。但是,在使用CMOS电路时,输入信号的低电平不能低于(VSS-0.5V),除某些接口电路外,输入信号的高电平不得高于(VDD+0.5V),否则可能引起保护二极管导通,甚至损坏进而可能使输入级损坏。

(2)使用注意事项

1)电源连接和选择。VDD端接电源正极,VSS端接电源负极(地)。绝对不许接错,否则器件因电流过大而损坏。CMOS器件在不同的电源电压下工作时,其输出阻抗、工作速度和功耗等参数都有所变化,设计中应加以考虑。

2)输入端处理。多余输入端不能悬空。应按逻辑要求接VDD或接VSS,以免受干扰造成逻辑混乱,甚至还会损坏器件。对于工作速度要求不高,而要求增加带负载能力时,可把输入端连接在一起使用。

对于安装在印制电路板上的CMOS器件,为了避免输入端悬空,在电路板的输入端应接入限流电阻和保护电阻,当VDD=+5V时,限流电阻取5.1kΩ,保护电阻一般取100kΩ~1MΩ。

3)输出端处理。输出端不允许直接接VDD或VSS,否则将导致器件损坏,除三态(TS)器件外,不允许两个不同芯片输出端并联使用,但有时为了增加驱动能力,同一芯片上的相同信号输出端可以并联。

4)对输入信号UI的要求。UI的高电平UIH<VDD,UI的低电平UIL小于电路系统允许的低电压,不能小于VSS。

5)接通电源要求。必须先接通电源,再加入信号。工作结束后,应先撤除信号,再关闭电源。不可在接通电源的情况下插入或拔出组件。

6)焊接和储存要求。电烙铁接地要可靠,或将电烙铁断电后,用余热快速焊接。储存时,一般用金属箔或导电泡棉将组件各引脚短路。

3.OC门与OD门

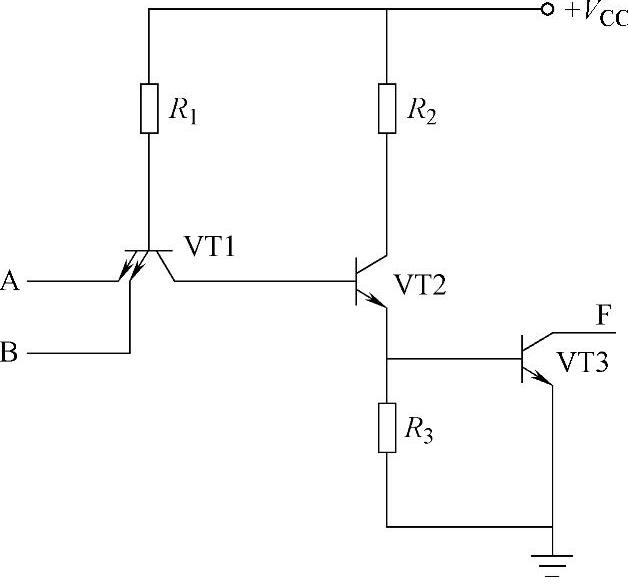

为了提高集成电路带负载能力、灵活匹配不同电源电压的负载,集成电路输出级取消推拉式结构,将上拉器件去掉,形成了OC(集电极开路)或OD(漏极开路)结构,采用OC结构的TTL门电路称为OC门,采用OD结构的CMOS门电路称为OD门。OC结构如图5-8中晶体管VT3所示。

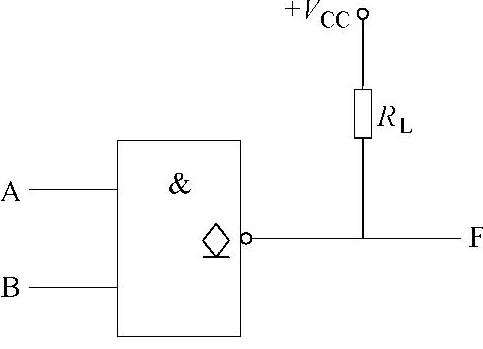

由于OC门和OD门没有内部上拉器件,所以不能输出高电平电流,要想在电路输出端得到正常的高电平,必须外接一个电阻RL与电源VCC相连,该电阻称为上拉电阻,如图5-9所示。

图5-8 OC与非门内部结构示意图

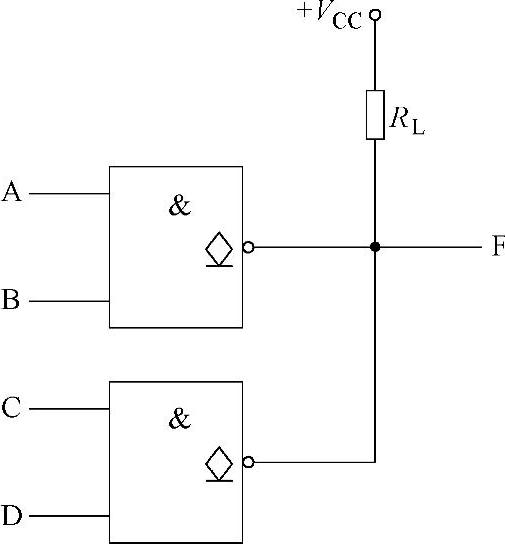

OC门和OD门可以实现与逻辑功能,即将几个OC门的输出端直接连在一起,通过一个上拉电阻接到电源VCC上,输出端即实现了与逻辑功能,如图5-10所示。

图5-9 OC门和OD门的使用

图5-10 与逻辑功能

在图5-10中,

此外,OC门和OD门还可以用来实现电平移位功能,只要改变上拉电阻所接电源的电压,就可以得到想要的高电平电压。使用OC门和OD门时,必须注意根据负载电流合理选择上拉电阻,才能实现正确的逻辑关系。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。