多通道缓冲串行口(McBSP)是一个高速、全双工、多通道缓冲串行接口,可直接与其他TMS320C54x、编码器以及系统中的其他串口器件通信。TMS320C54x的多通道缓冲串行口(McBSP)是在缓冲串行口的基础上发展起来的。在外部通道选择电路的控制下,采用分时方式实现多路缓冲串行通信,与以前的串行口相比,具有很大的灵活性。McBSP提供了全双工通信、连续数据流的双缓冲数据寄存器、接收和发送独立的帧和时钟信号,可以直接与T1/E1帧接口。

McBSP的主要特点:

1)串行口的接收、发送时钟既可由外部设备提供,又可由内部时钟提供。

2)帧同步信号和时钟信号的极性可编程。

3)信号的发送和接收既可单独运行,也可结合在一起配合工作。

4)McBSP的串行口可由CPU控制运行,也可以脱离CPU通过直接内存的读取操作来单独运行。

5)具有多通道通信能力,可达128个通道。

6)数据的宽度可在8、12、16、20、24和32位中选择,并可对数据进行A律和μ律压缩和扩展。

1.多通道缓冲串行口(McBSP)结构

McBSP的支持功能有全双工通信;双缓冲发送和三缓冲接收数据存储器;支持连续的数据流传送;能独立的接收、发送帧和时钟信号;可直接与工业标准的编码器、模拟界面芯片(AICs)、其他串行A/D或D/A器件连接并通信;具有外部变速时钟发生器及内部频率可编程时钟发生器;可以直接利用多种串行协议接口通信;多达128路发送和接收通道;数据的字长可选择,包括8、12、16、20、24和32位;可进行μ律或A律的压缩扩展通信;帧同步和时钟信号的极性可编程;可编程内部时钟和帧发生器。

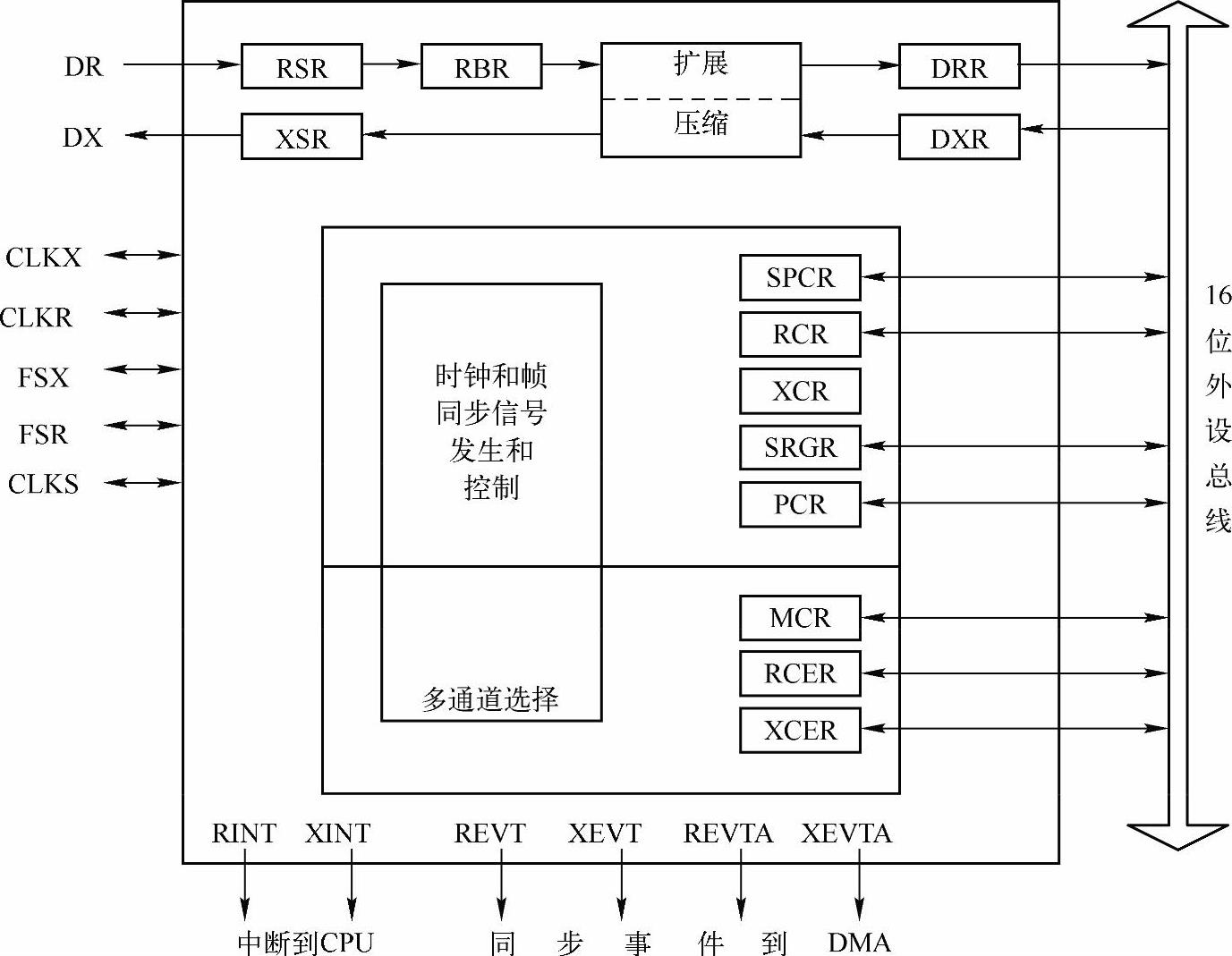

McBSP串行口是由外部通信引脚、接收发送通道、时钟及帧同步信号发生器、多通道选择以及CPU中断信号和DMA同步信号等组成,可分为数据通道和控制通道两部分。数据通道主要完成数据的接收和发送;控制通道可编程完成内部时钟和帧同步信号的产生与控制、多通道的选择、产生中断信号送往CPU和产生同步事件通知DMA控制器等。

McBSP的内部结构如图8-19所示。从图中可以看出,McBSP串口对外引出了硬件连线引脚,它们是串行数据发送引脚DX,串行数据接收引脚DR,发送时钟引脚CLKX,接收时钟引脚CLKR,发送帧同步引脚FSX,接收帧同步引脚FSR,外部提供的采样时钟引脚CLKS。

McBSP通过DX和DR引脚与外部设备进行数据通信,时钟和帧同步等控制信息的传输通过CLKX、CLKR、FSX和FSR引脚来实现。

在McBSP中可以内部连接TMS320C54x中断信号或DMA同步事件等信号。例如,RINT,可用于触发TMS320C54x的发送中断信号;XINT,可用于触发TMS320C54x的接收中断信号;REVT,可用于触发DMA接收同步事件信号;XEVT,可用于触发DMA发送同步事件信号;REVTA,可用于触发DMA接收同步事件信号;XEVTA,可用于触发DMA发送同步事件信号。

2.多通道缓冲串行口(McBSP)的控制寄存器

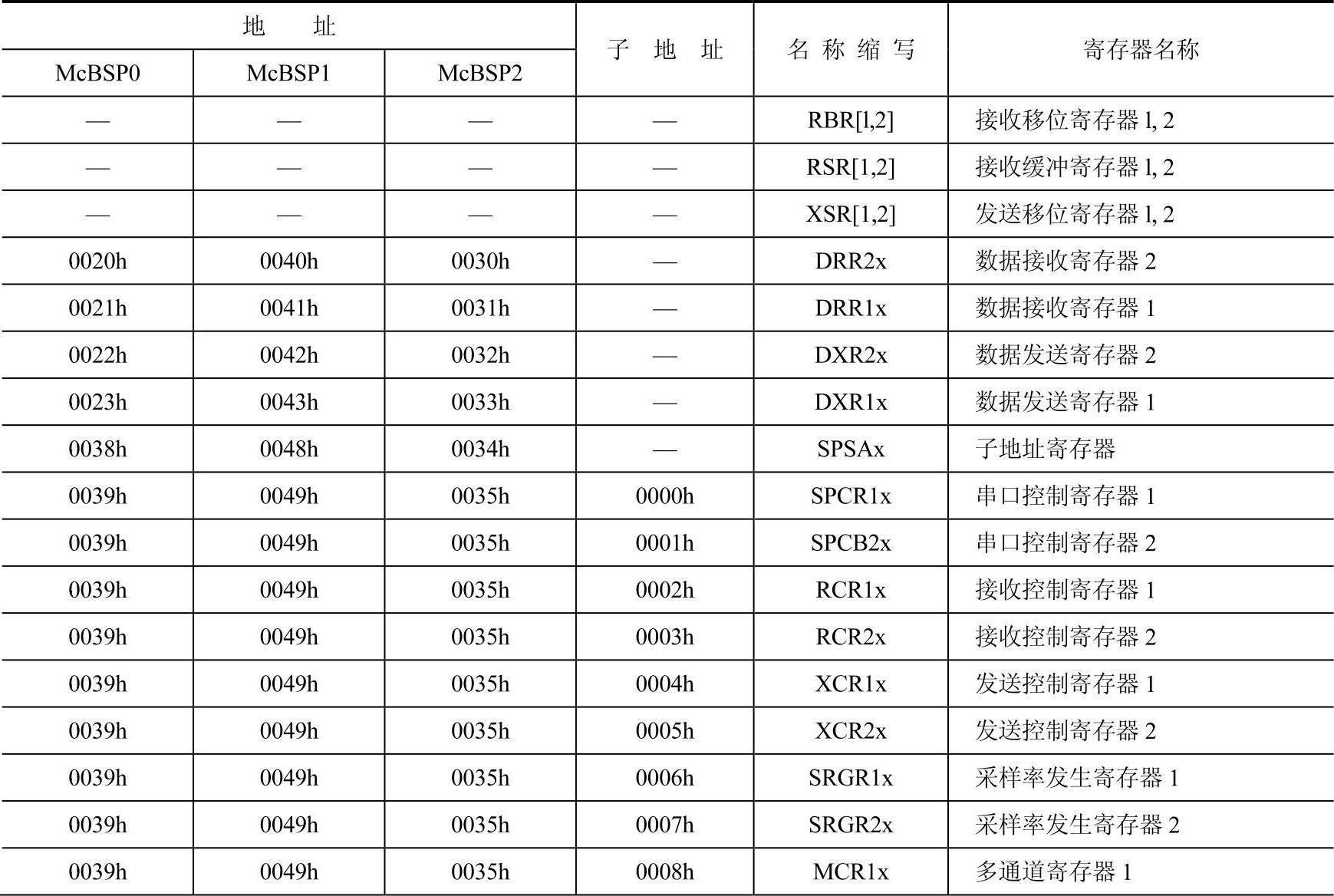

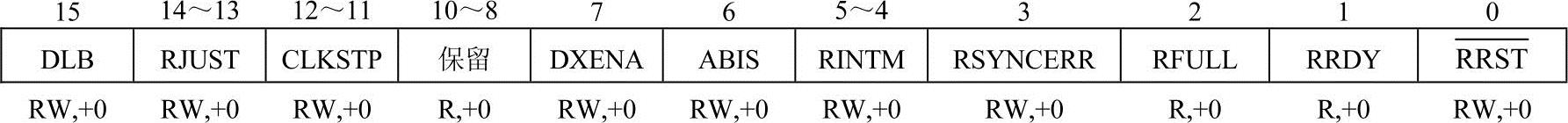

TMS320C54x可以通过内部总线访问McBSP的控制寄存器。McBSP寄存器列表见表8-8。

图8-19 多通道缓冲串行口(McBSP)的内部结构

表8-8 McBSP寄存器列表

(续)

用于McBSP串口配置的寄存器共有7个,分别为串口控制寄存器SPCR1和SPCR2、引脚控制寄存器PCR、接收控制寄存器RCR1和RCR2,以及发送控制寄存器XCR1和XCR2。3个16位寄存器SPCR1、SPCR2和PCR可进行串口配置。这3个寄存器包含了McBSP的状态信息和当前操作的配置。接收和发送寄存器RCR[1,2]和XCR[1,2]用于配置收发操作的不同参数。

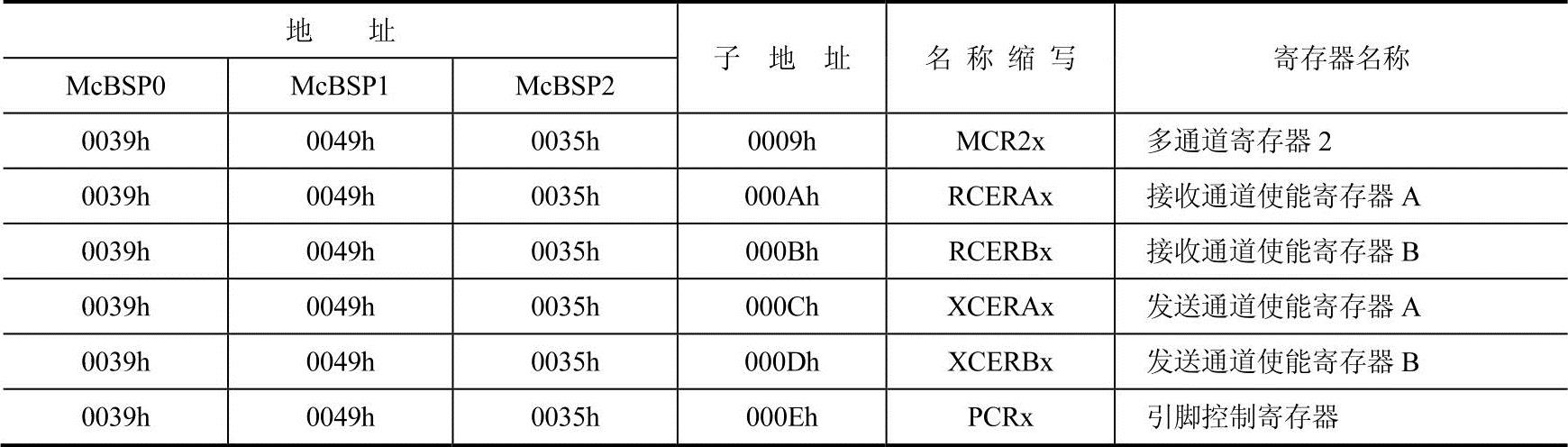

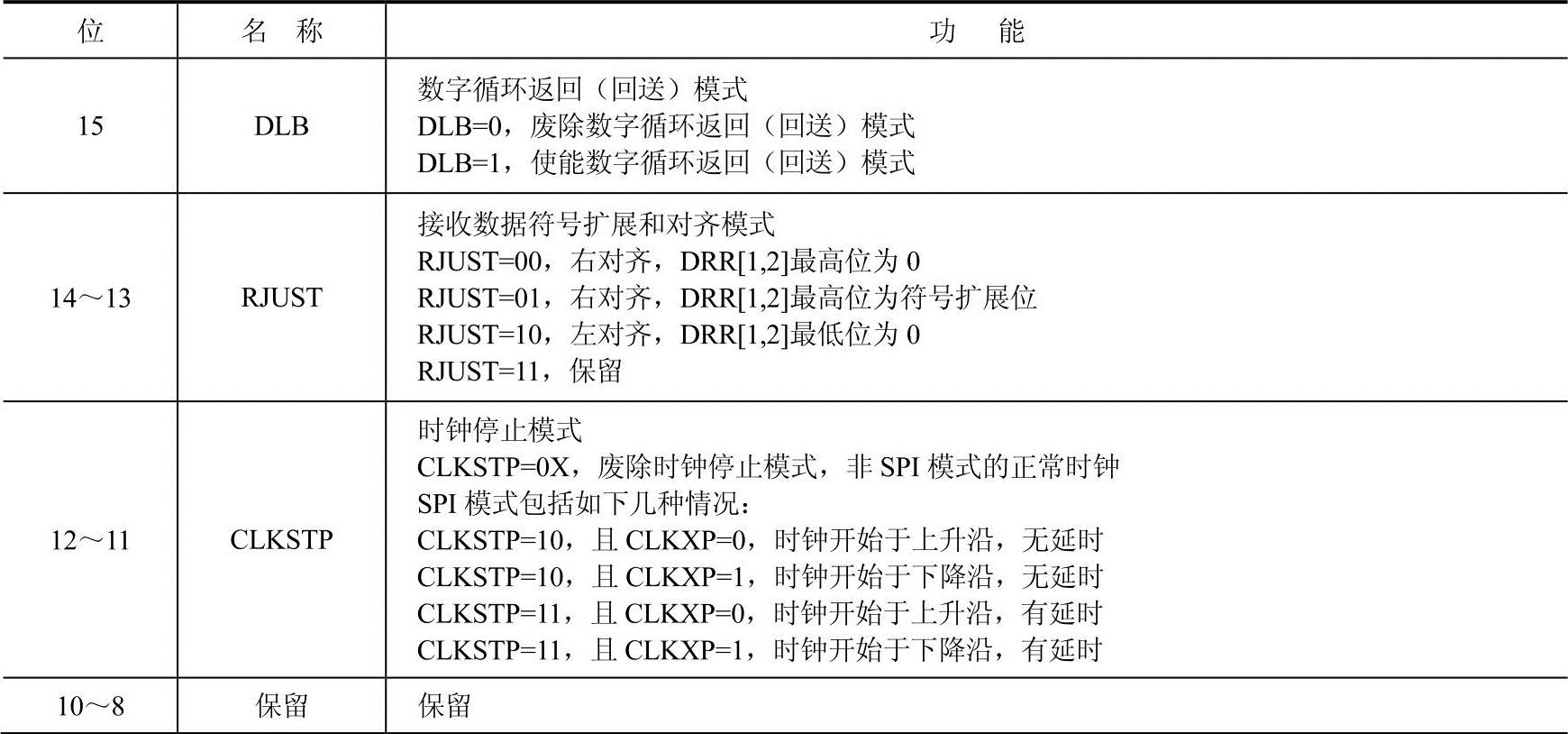

(1)McBSP的控制寄存器SPCR1

SPCR1设置McBSP串口的数字环回模式、接收符号扩展和校验模式、ClockStop模式、DX是否允许、A-bis模式、接收中断模式等,并给出接收同步错误、接收移位寄存器(RSR[1,2])空、接收准备好等状态。此外可以进行接收复位。SPCR1各位的定义如图8-20所示,其各位的功能描述见表8-9。

图8-20 SPCR1的位结构定义

表8-9 SPCR1的位功能说明

(续)

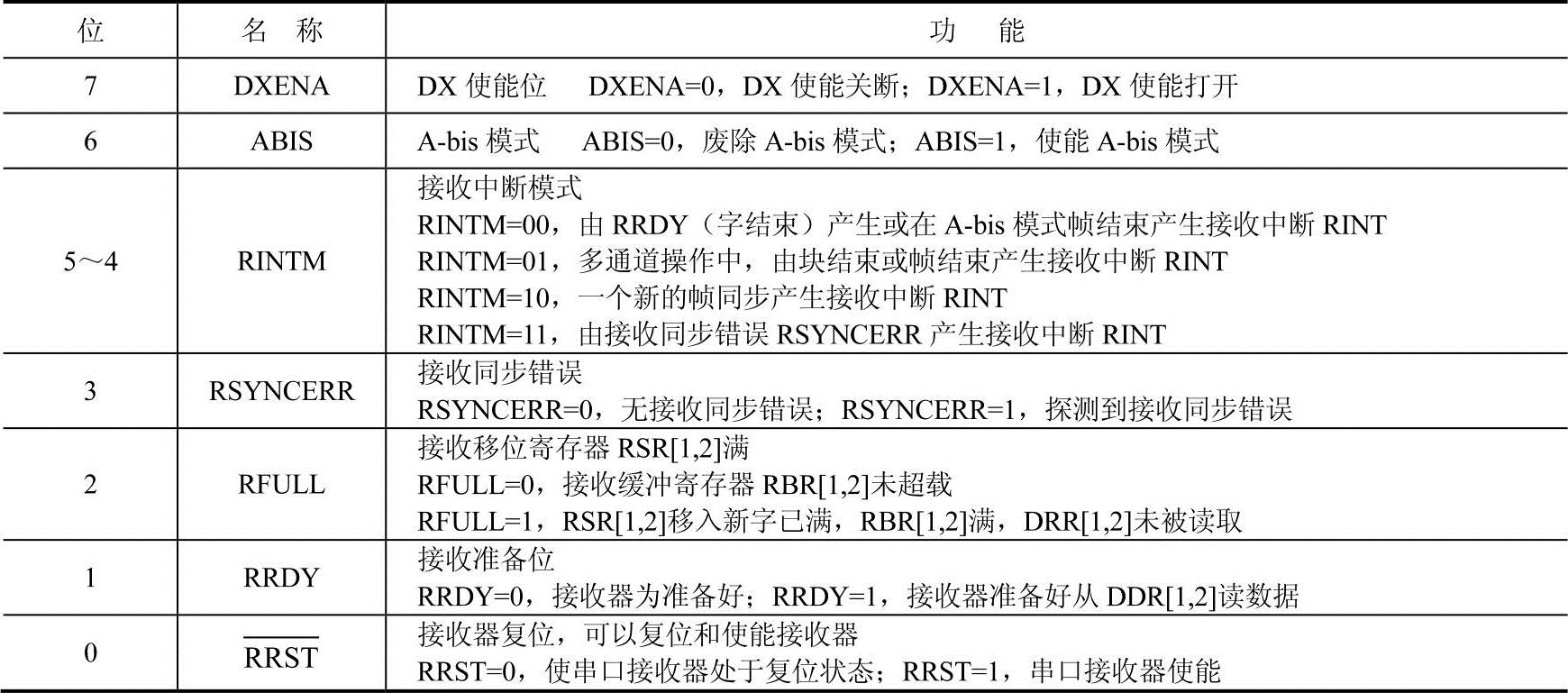

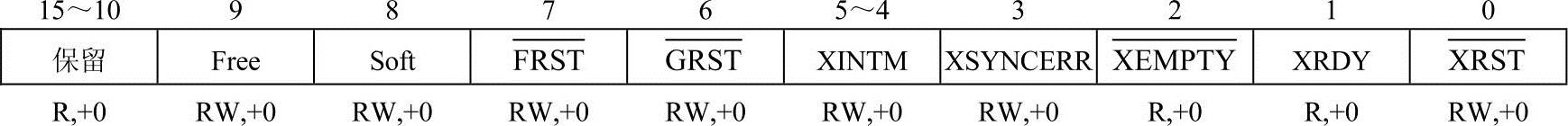

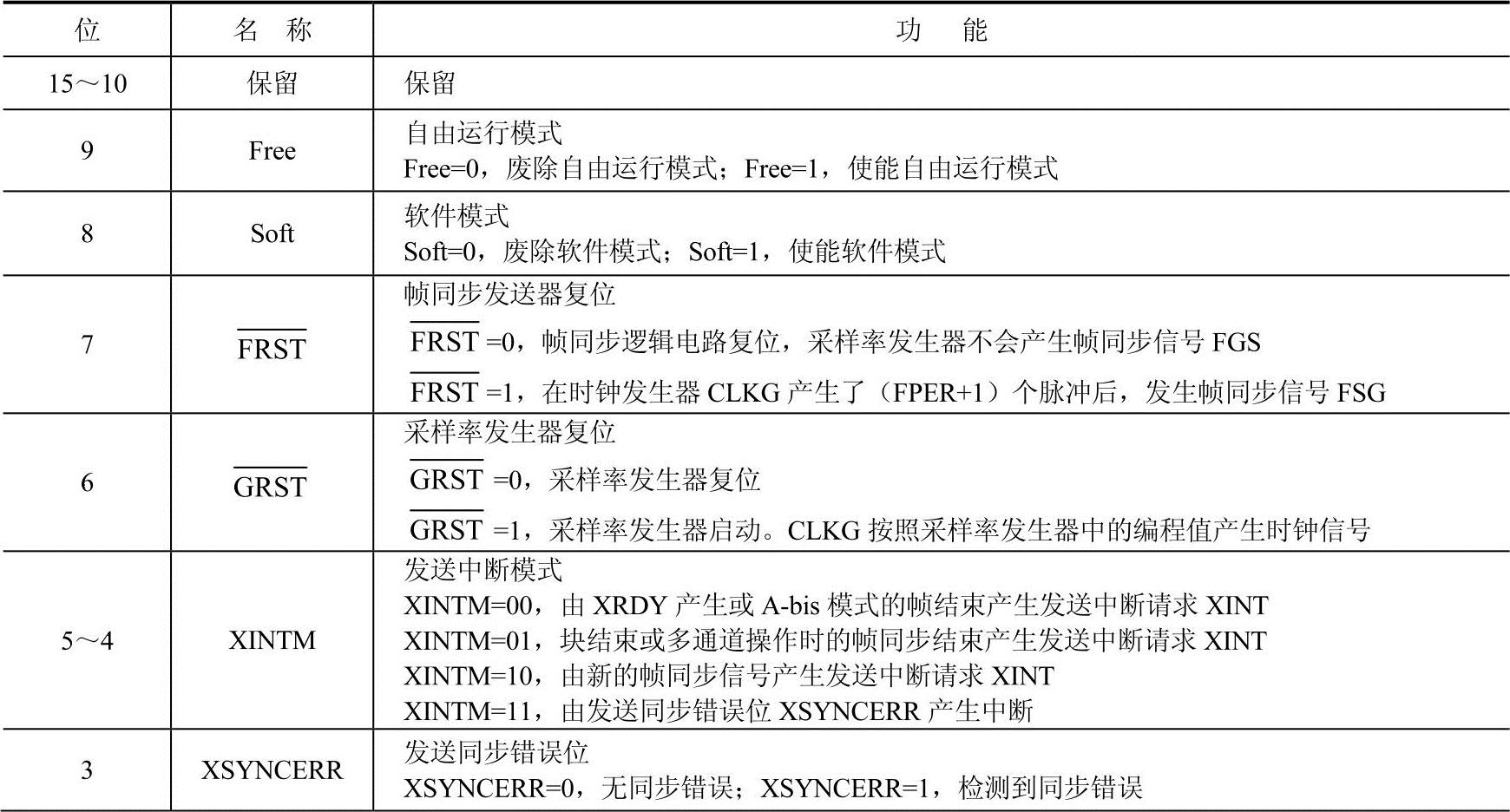

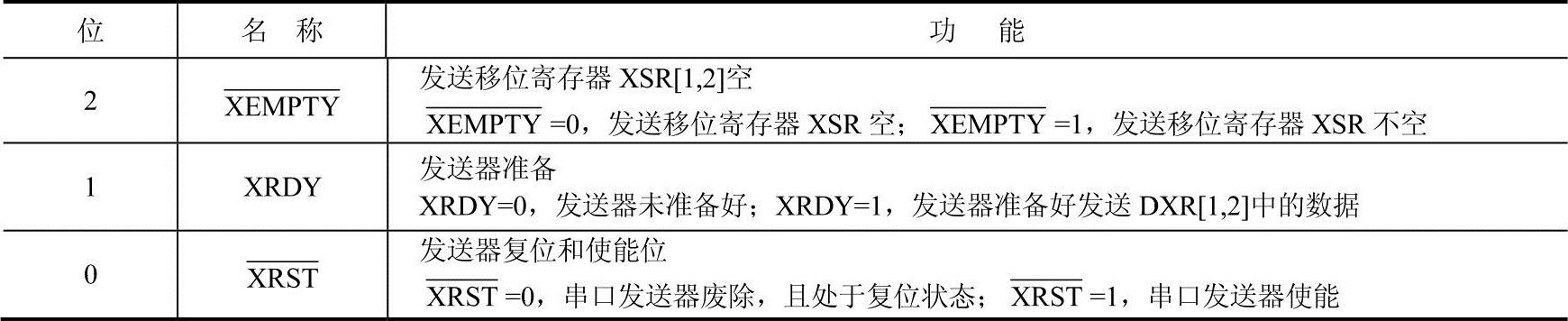

(2)McBSP的控制寄存器SPCR2

SPCR2设置McBSP自由运行模式、SOFT模式、发送中断模式,并给出发送同步错误、发送移位寄存器(XSR[1,2])空、发送准备好等状态。此外可以进行发送复位、采样率发生器复位、帧同步发生电路复位。SPCR2的位结构定义如图8-21所示,其各位的功能描述见表8-10。

图8-21 SPCR2的位结构定义

表8-10 SPCR2的位功能说明

(续)

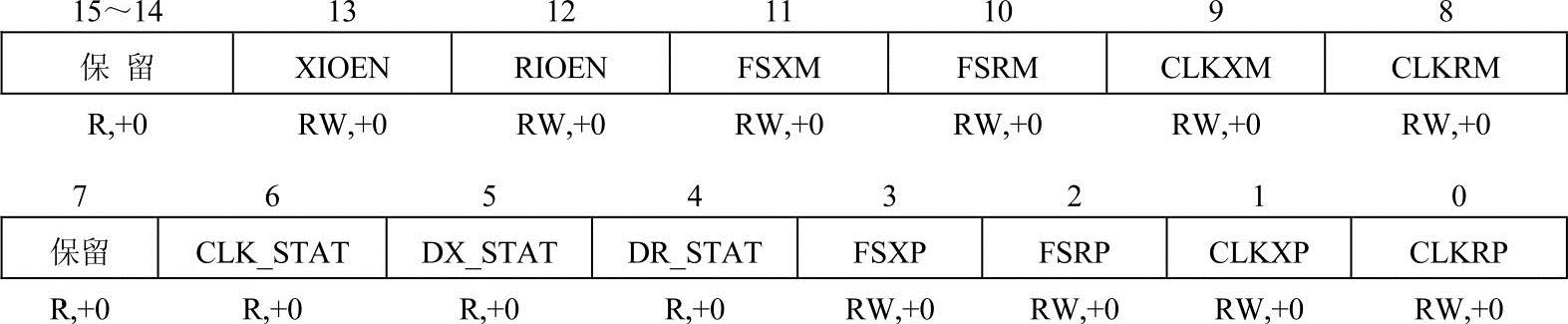

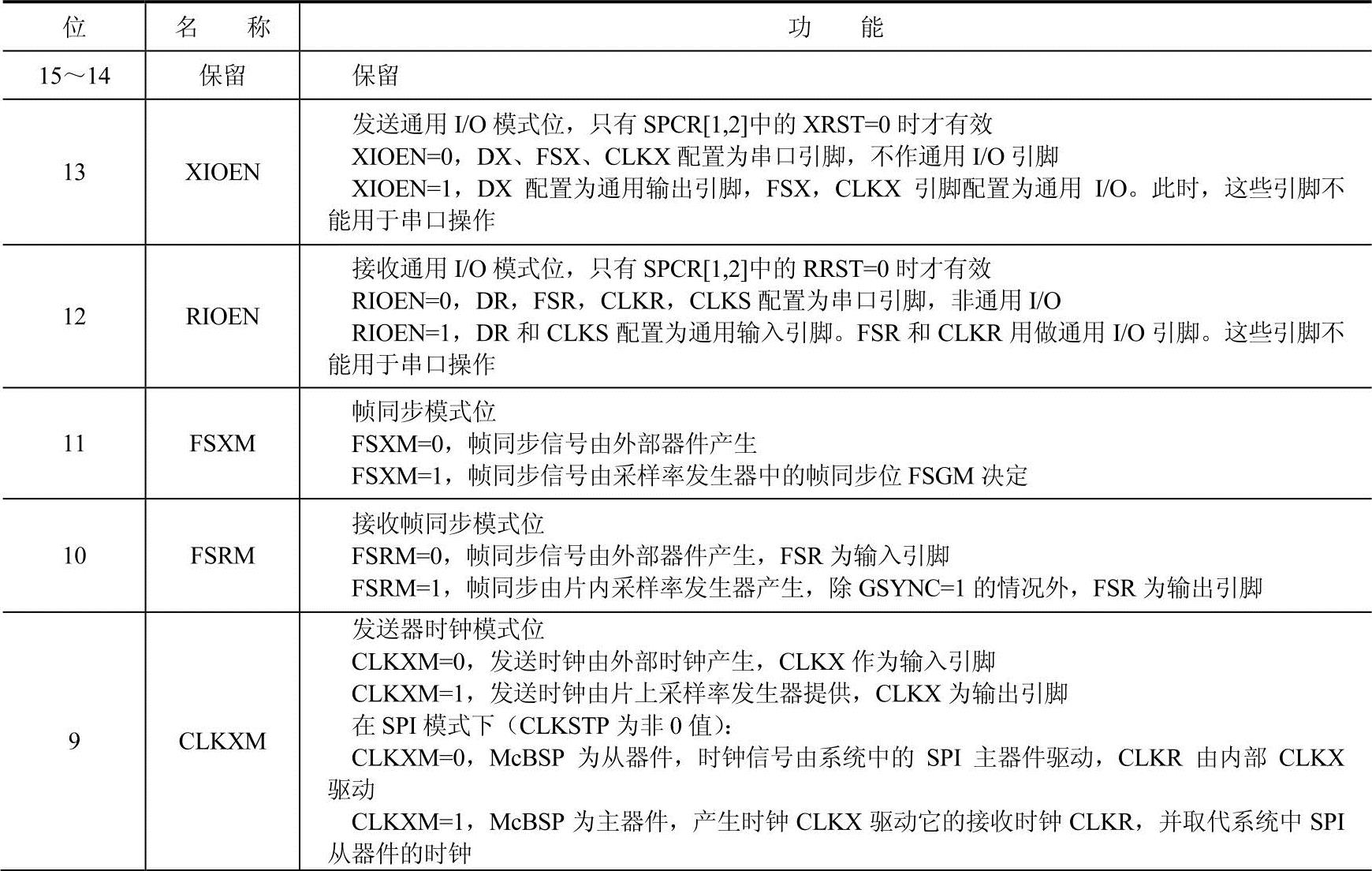

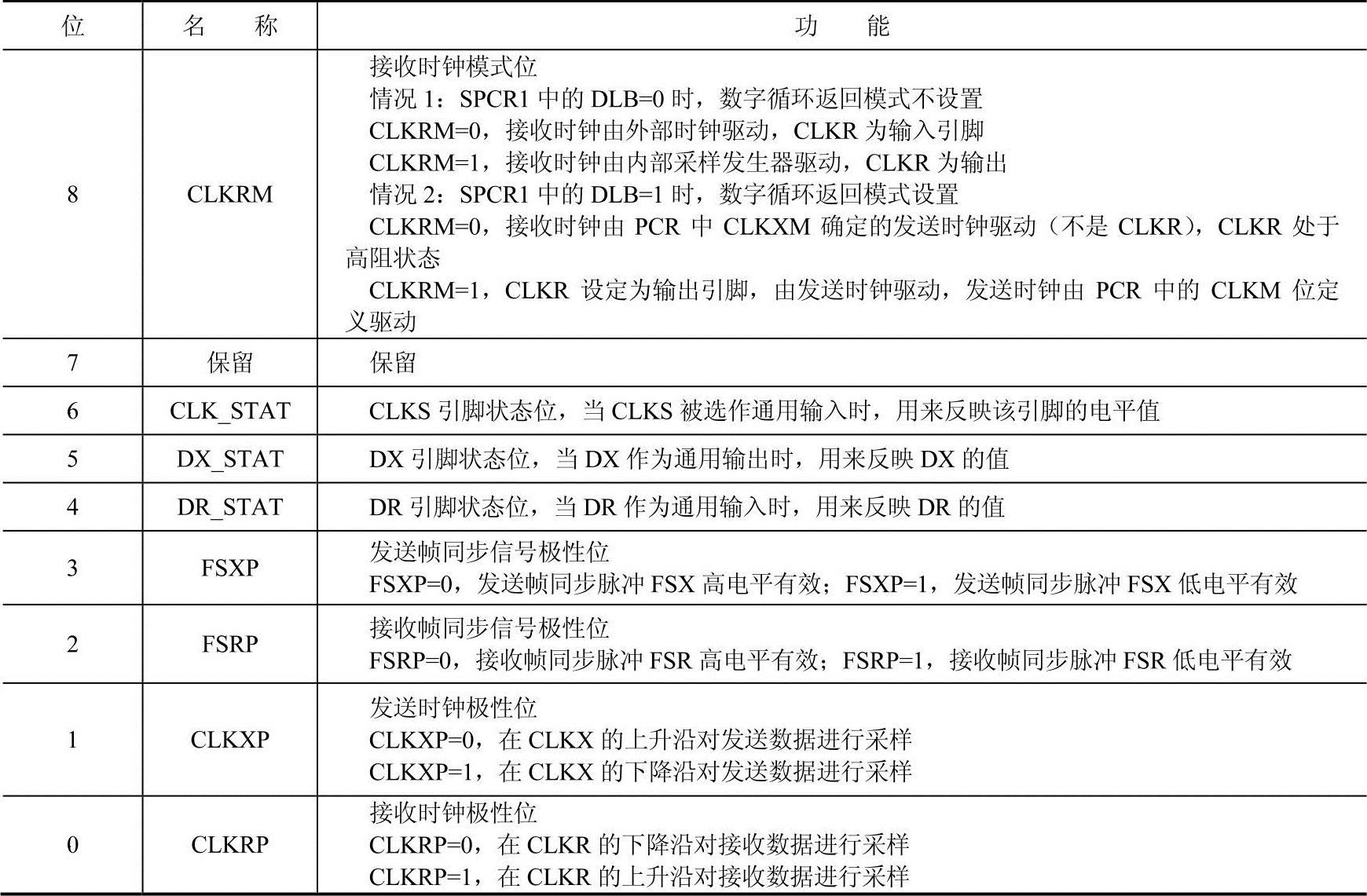

(3)McBSP的引脚控制寄存器PCR

PCR设置McBSP传输帧同步模式、接收帧同步模式、发送时钟模式、接收时钟模式、发送帧同步信号的极性、接收帧同步信号的极性、发送时钟极性、接收时钟极性,并给出CLKS、DX、DR脚的状态。此外PCR还定义发送和接收部分在复位时相应引脚是否配置为通用I/O。PCR各位的定义如图8-22所示,其各位的功能描述见表8-11。

图8-22 PCR的位结构定义

表8-11 PCR的位功能说明

(续)

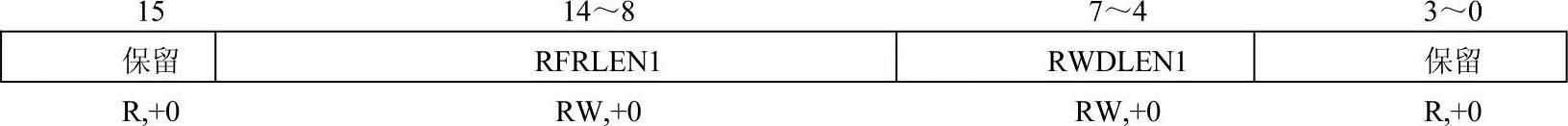

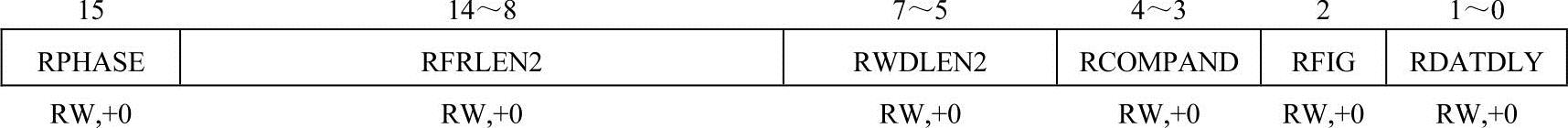

(4)McBSP的接收控制寄存器RCR1

RCR1设置McBSP接收时第一相(FIRSTPHASE)的接收帧长度可选择1~128个字,接收字长度可选择8位、12位、16位、20位、24位、32位。RCR1各位的定义如图8-23所示,其各位的功能描述见表8-12。

图8-23 RCR1的位结构定义

表8-12 RCR1的位功能说明

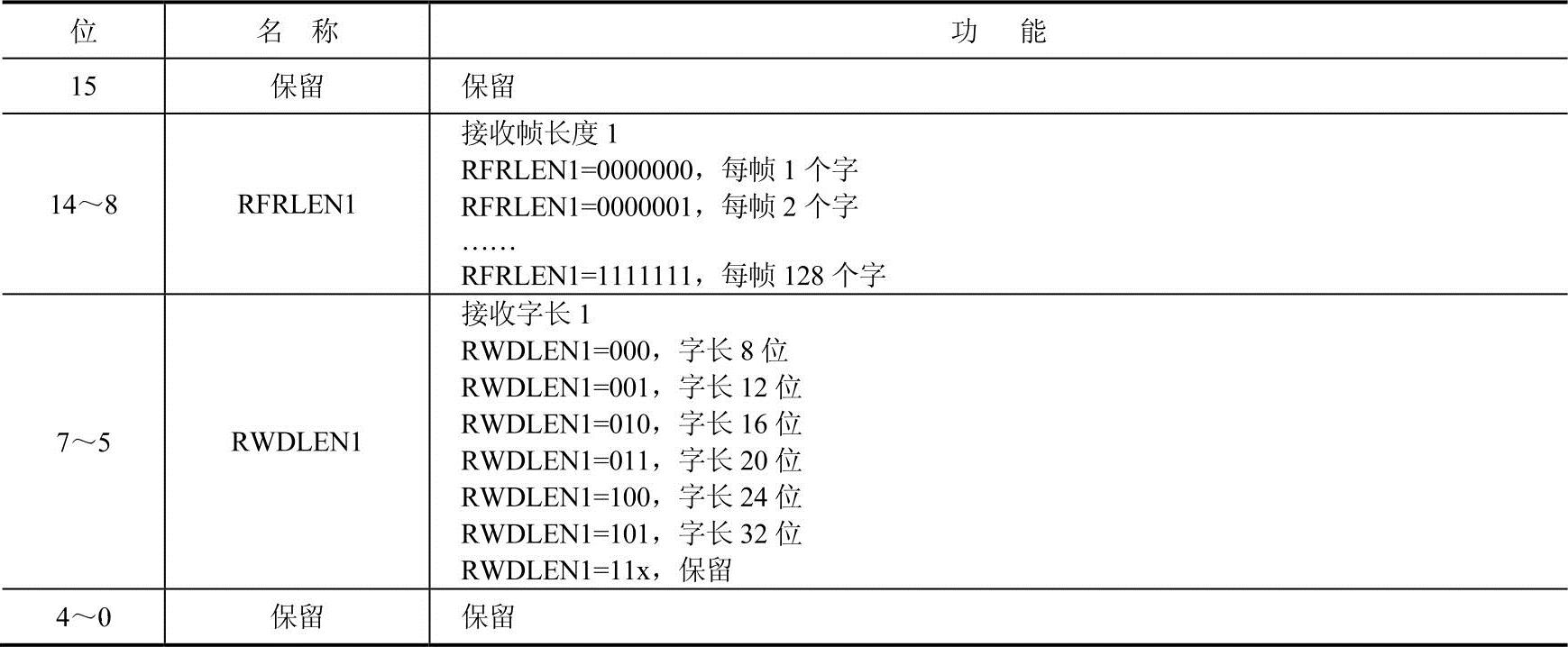

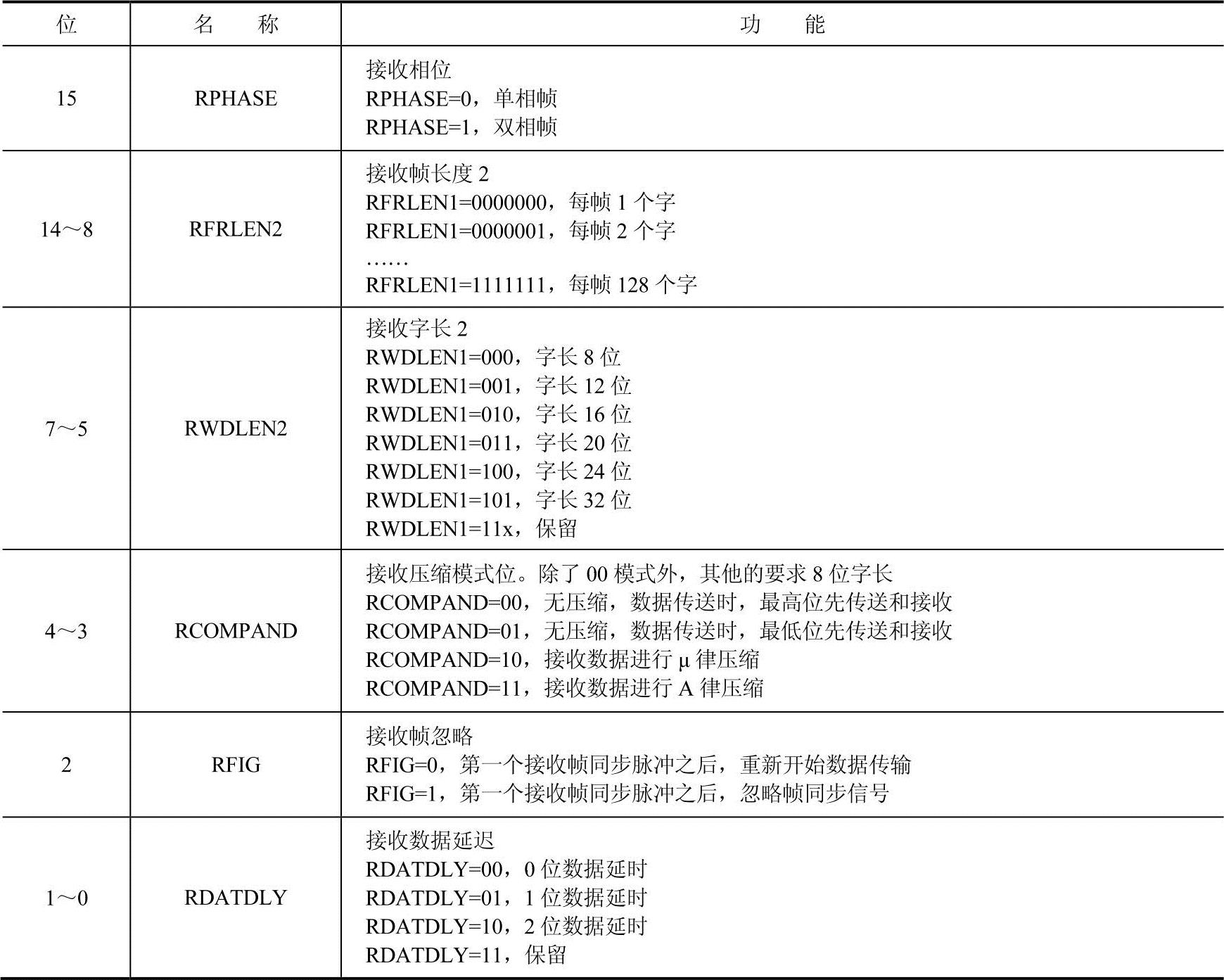

(5)McBSP的接收控制寄存器RCR2

RCR2设置McBSP接收时是否允许第二相(RPHASE=1)。如果允许,设置McBSP接收时第二相的接收帧长度可选择1~128个字,接收字长度可选择8位、12位、16位、20位、24位、32位。此外,RCR2设置McBSP接收时的接收压缩模式、接收同步帧忽略模式、接收数据延迟。RCR2各位的定义如图8-24所示,其各位的功能描述见表8-13。

图8-24 RCR2的位结构定义

表8-13 RCR2的位功能说明

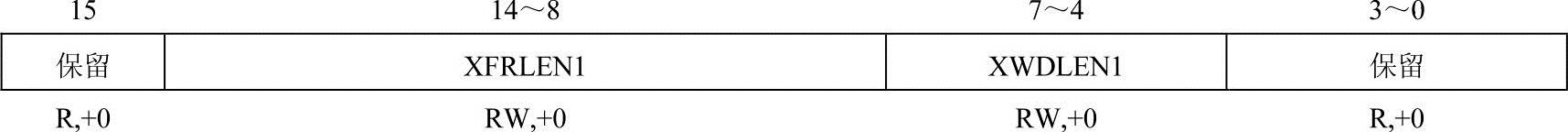

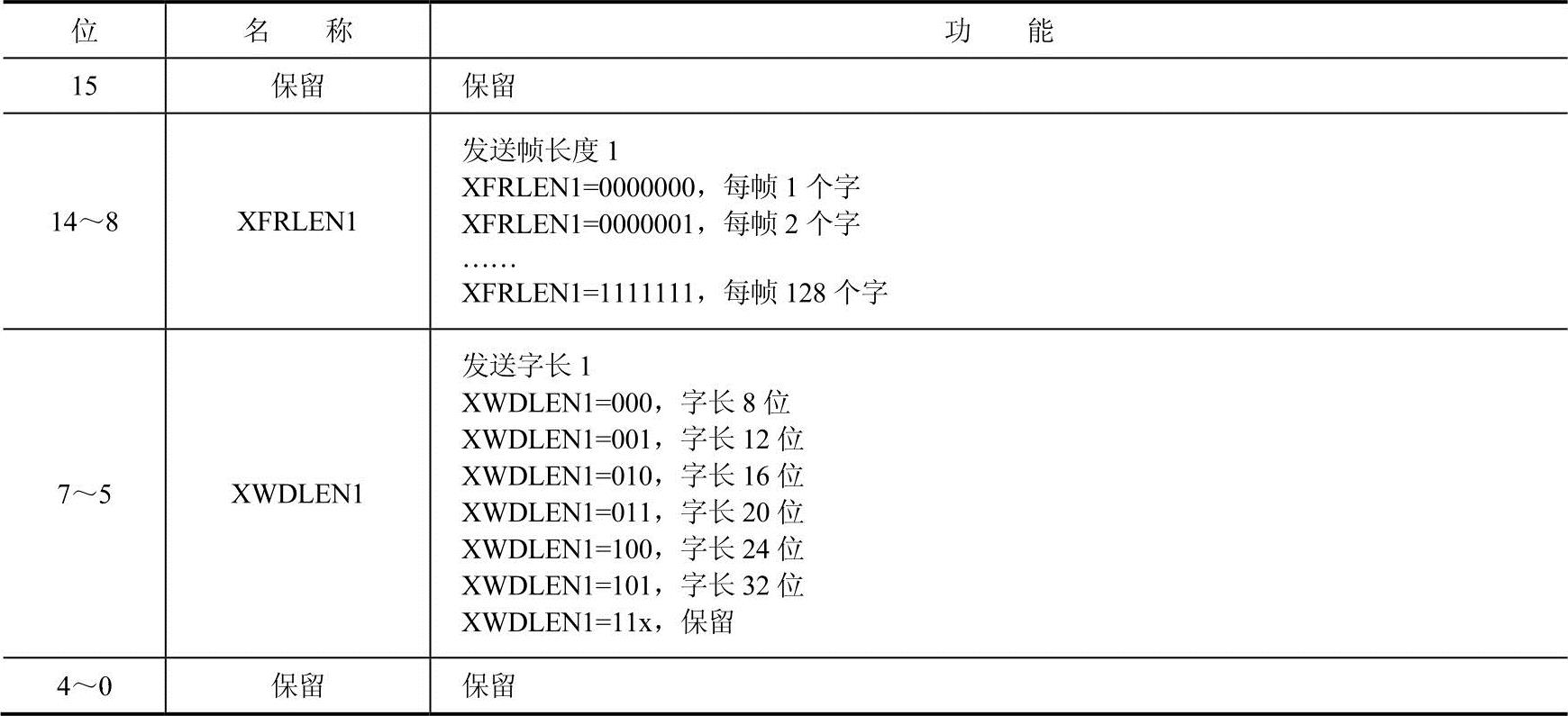

(6)McBSP的发送控制寄存器XCR1

XCR1设置McBSP发送时第一相(FIRSTPHASE)的发送帧长度可选择1~128个字,发送字长度可选择8位、12位、16位、20位、24位、32位。XCR1各位的定义如图8-25所示,其各位的功能描述见表8-14。

图8-25 XCR1的位结构定义

表8-14 XCR1的位功能说明

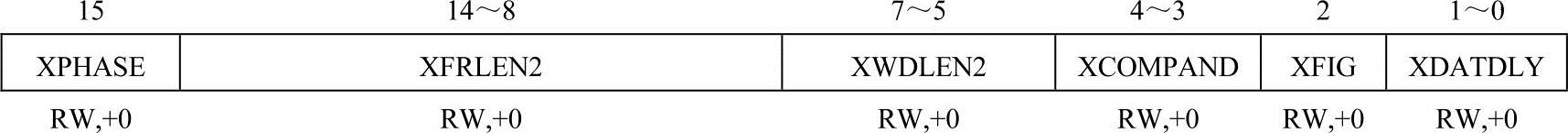

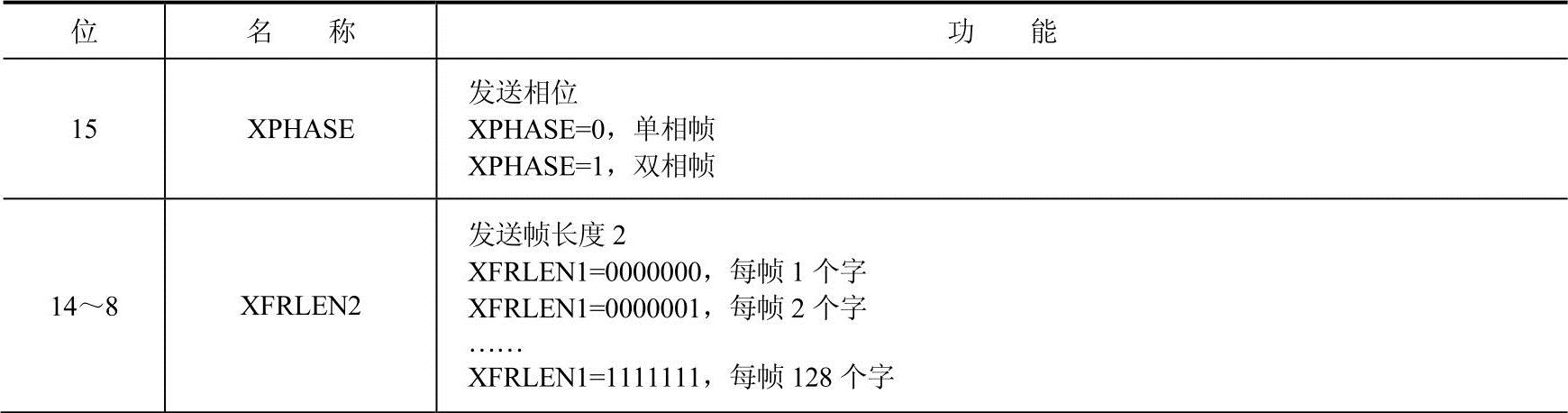

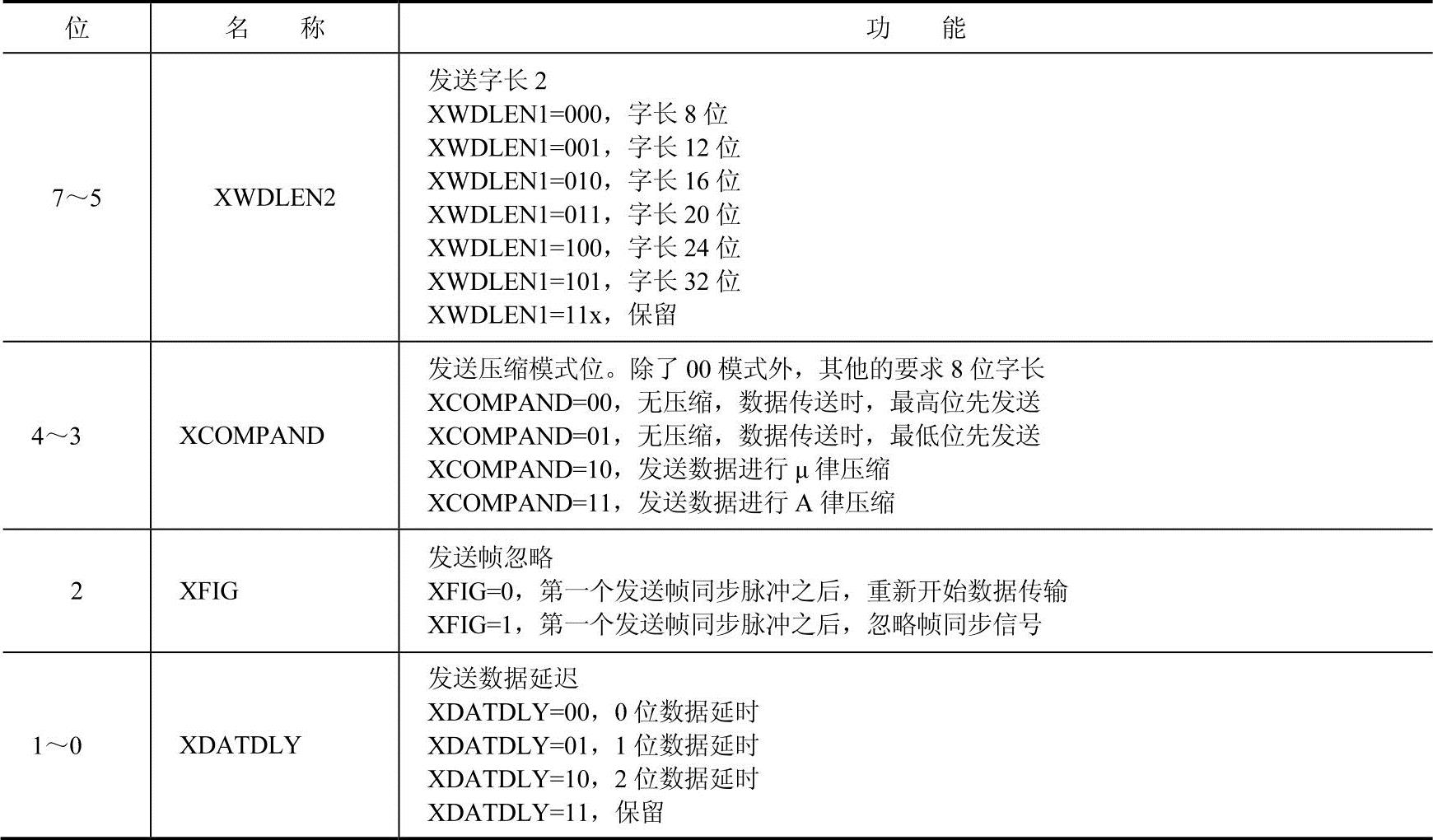

(7)McBSP的发送控制寄存器XCR2

XCR2设置McBSP发送时是否允许第二相(XPHASE=1)。如果允许,设置McBSP时第二相的发送帧长度可选择1~128个字,发送字长度可选择8位、12位、16位、20位、24位、32位。此外,XCR2设置McBSP发送时的发送压缩模式、发送同步帧忽略模式、发送数据延迟。XCR2各位的定义如图8-26所示,其各位的功能描述见表8-15。

图8-26 XCR2的位结构定义

表8-15 XCR2的位功能说明

(续)(https://www.xing528.com)

3.McBSP串口的控制操作

(1)McBSP串行口的复位

McBSP串行口的复位有两种方式,分别是系统复位和McBSP复位方式。

1)系统复位,是指通过DSP复位端 复位。当

复位。当 时,使串口发送器、接收器、采样率发生器复位;RS复位完成后,串口仍然处于复位状态,此时

时,使串口发送器、接收器、采样率发生器复位;RS复位完成后,串口仍然处于复位状态,此时 、

、 、

、 、

、 均为0。

均为0。

2)McBSP复位方式,是指利用McBSP控制寄存器的控制位复位。通过对控制寄存器中的 、

、 和

和 位清0,可分别对发送器、接收器和采样率发生器进行复位。

位清0,可分别对发送器、接收器和采样率发生器进行复位。

表8-16列出了两种复位情况下串口各引脚的状态。

表8-16 McBSP复位状态

(续)

(2)McBSP串行口的初始化

McBSP复位后,可进行初始化,其步骤如下:

1)对控制寄存器的复位位(接收/发送复位)置0,即使RRST、XRST和GRST位为0。

2)根据串口复位的要求,对McBSP的寄存器进行编程配置。

3)等待2个时钟周期,以保证内部时钟同步。

4)对DXD写信息,设置数据通道。

5)将XRST和RRST置1,使串口处于使能状态。

6)如果需要内部帧同步信号,则设定FRST=1。

7)等待2个时钟周期后,接收器和发送器被激活。

(3)McBSP串口的多通道选择配置

使用单相帧同步设置McBSP,可为发送器、接收器选择独立的多通道工作模式。每一帧代表一个时分复用(TDM)数据流。用(R/X)FRLEN1位设定的每帧字数来表示所选的有效通道数。当采用时分复用数据流时,TMS320C54x仅需要处理少数通道。为了节省存储空间和总线带宽,多通道选择允许对发送和接收的多通道进行单独配置。McBSP的多通道选择配置可以通过设定多通道控制寄存器来进行。下面介绍各组寄存器的功能使用。

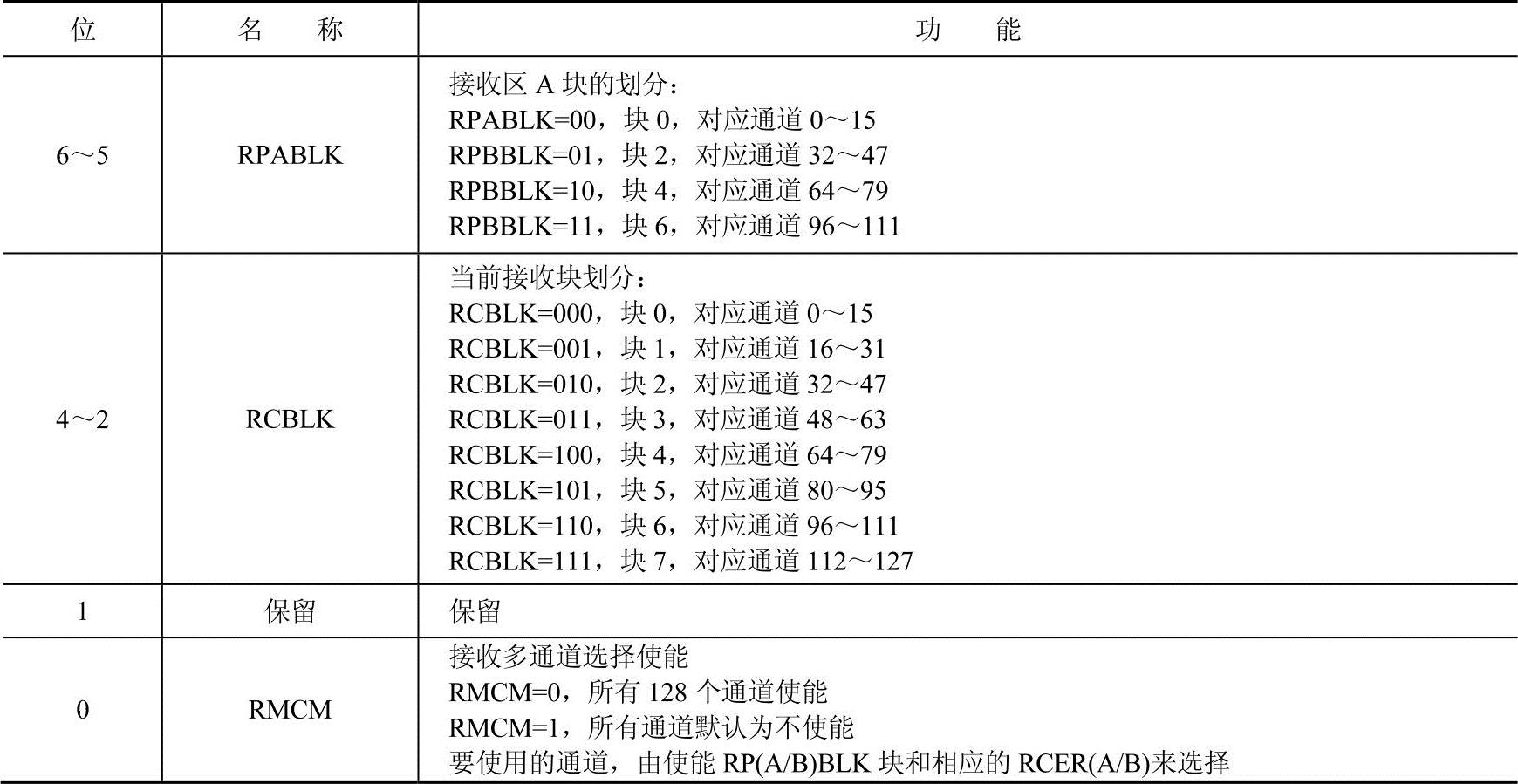

1)多通道控制寄存器MCR1

MCR1设置McBSP在多通道工作模式时的接收PART-B的块结构、接收PART-A的块结构、当前可接收块、接收多通道选择。MCR1各位的定义如图8-27所示,其各位的功能描述见表8-17。

图8-27 MCR1的位结构定义

表8-17 MCR1的位功能说明

(续)

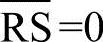

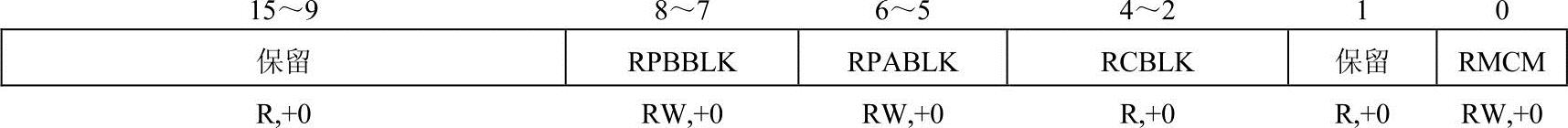

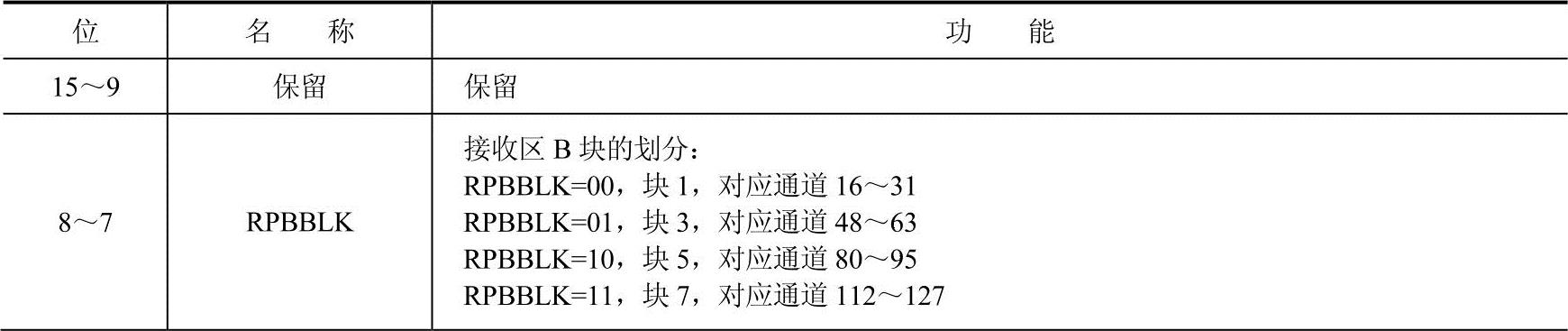

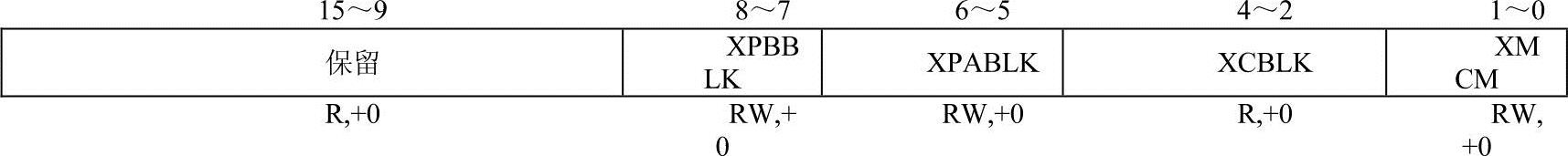

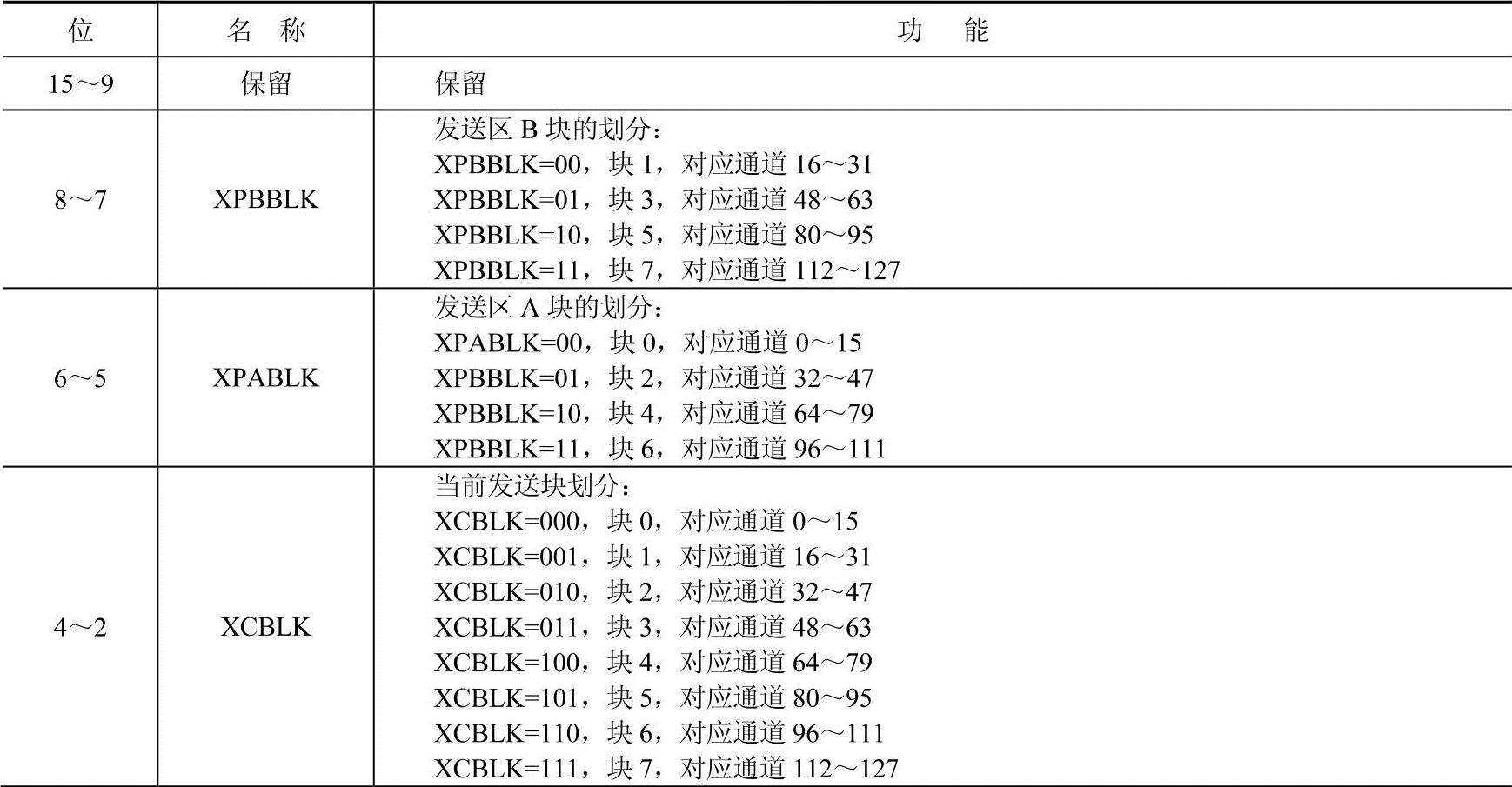

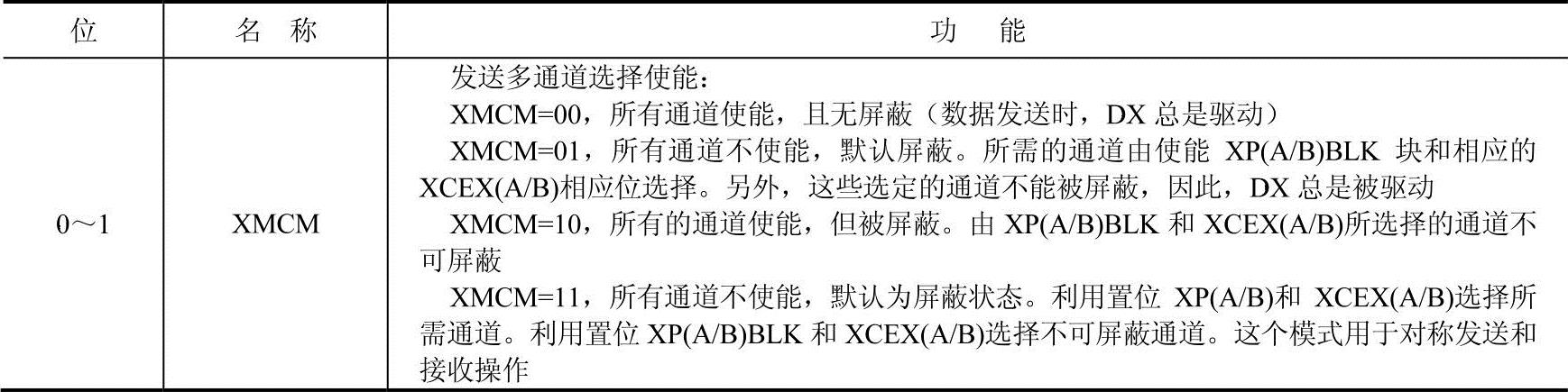

2)多通道控制寄存器MCR2

MCR2设置McBSP在多通道工作模式时的发送PART-A块结构、发送PART-B块结构、当前发送块、发送多通道选择。MCR2各位的定义如图8-28所示,其各位的功能描述见表8-18。

图8-28 MCR2的位结构定义

表8-18 MCR2的位功能说明

(续)

3)接收通道使能寄存器RCERx

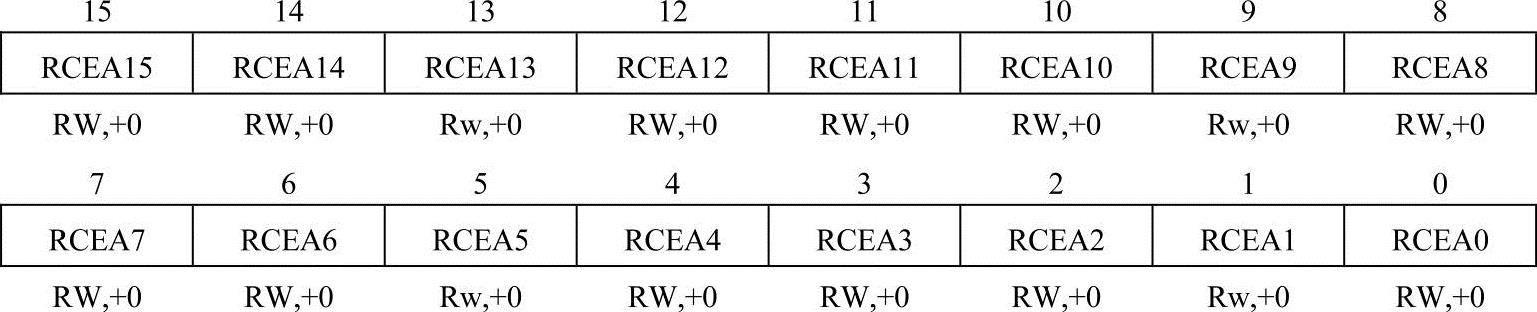

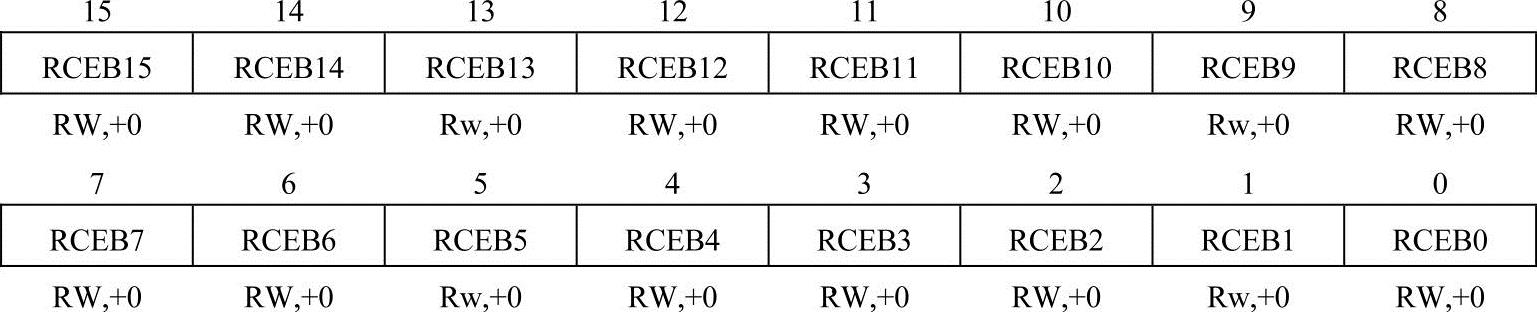

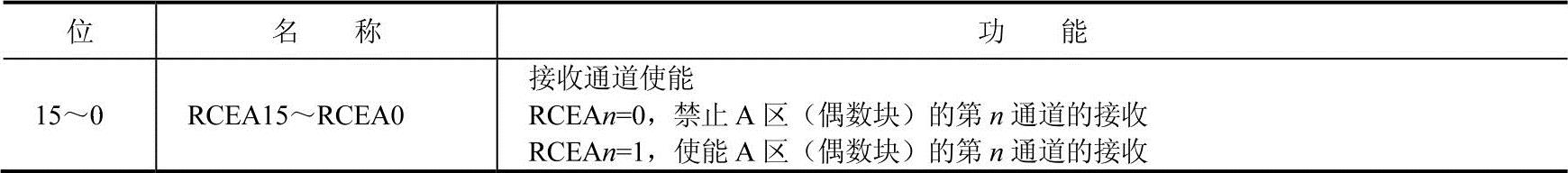

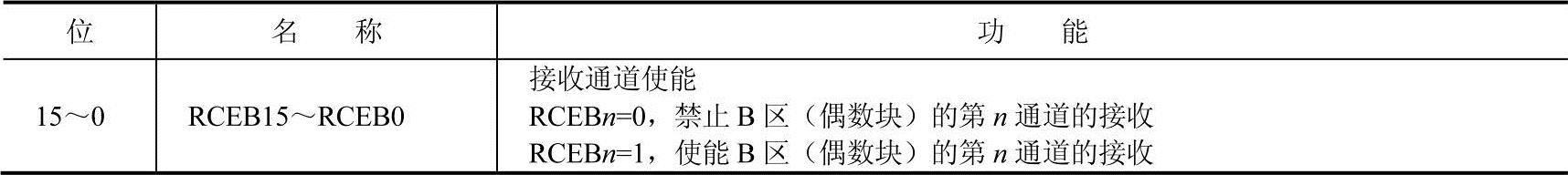

接收通道使能寄存器RCERx,用于使能32个通道的接收,其中A区和B区各有16个通道,对应的通道使能寄存器分别为RCERA和RCERB。RCERA和RCERB各位的定义分别如图8-29和图8-30所示。RCERA和RCERB各位的功能描述分别见表8-19和表8-20。

图8-29 RCERA的位结构定义

图8-30 RCERB的位结构定义

表8-19 RCERA的位功能说明

表8-20 RCERB的位功能说明

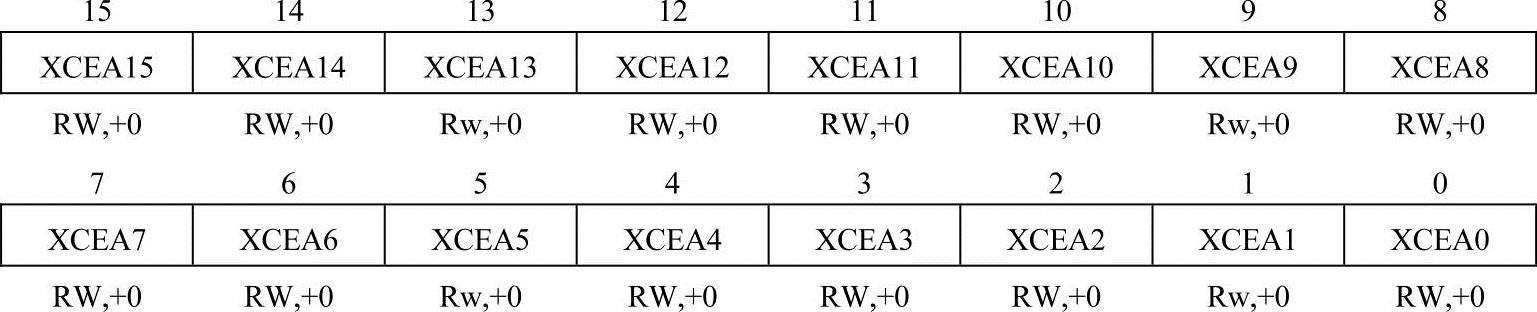

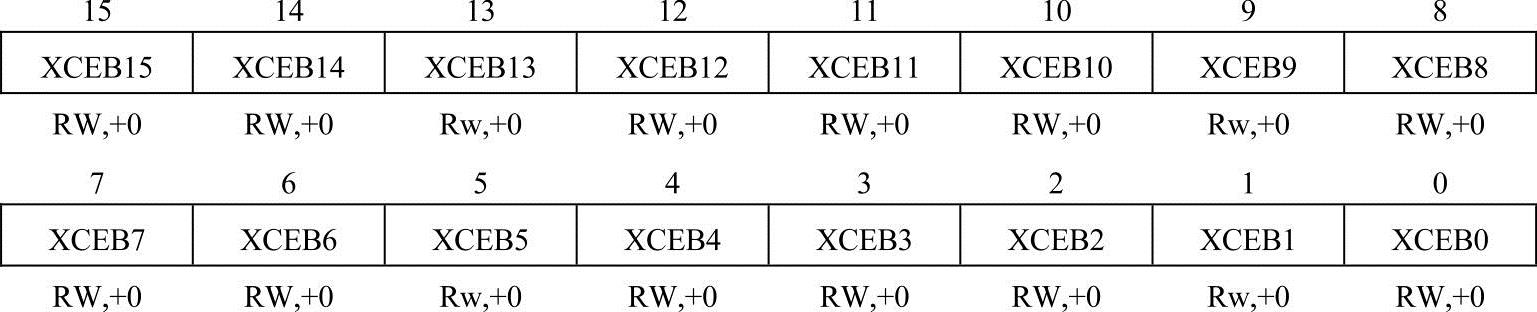

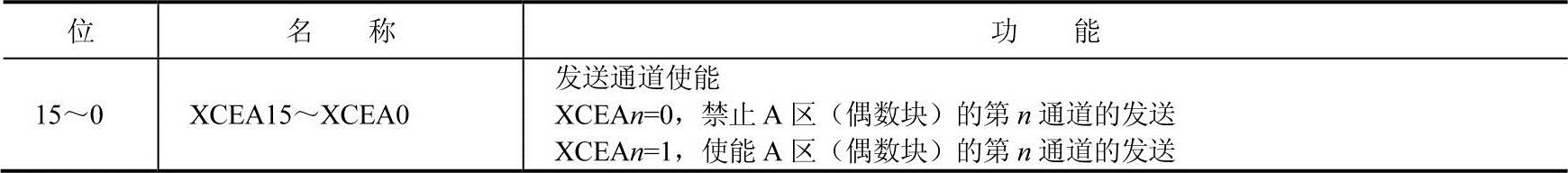

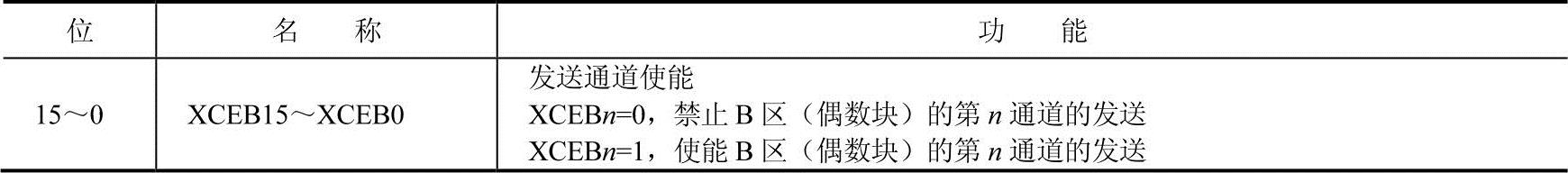

4)发送通道使能寄存器XCERx

发送通道使能寄存器XCERx,用于使能32个通道的发送,其中A区和B区各有16个通道,对应的通道使能寄存器分别为XCERA和XCERB。XCERA和XCERB各位的定义分别如图8-31和图8-32所示。XCERA和XCERB各位的功能描述分别见表8-21和表8-22。

图8-31 XCERA的位结构定义

图8-32 XCERB的位结构定义

表8-21 XCERA的位功能说明

表8-22 XCERB的位功能说明

4.McBSP的通信应用

在时钟信号和帧同步信号控制下,接收和发送通过DR和DX引脚与外部器件直接通信。如图8-11所示的连接方式,TMS320C54x对McBSP的操作是利用16位控制寄存器,通过片内外设总线进行存取控制。

(1)数据发送过程

1)TMS320C54x通过外设总线,将数据写入数据发送寄存器DXR[1,2]。

2)McBSP串口将DXR[1,2]中的发送数据传送到发送移位寄存器XSR[1,2]中。

3)通过发送移位寄存器XSR[1,2],将数据经DX引脚移出发送。

(2)数据接收过程

1)McBSP串口通过DR引脚,将接收数据移入接收移位数据寄存器RSR[1,2]中。

2)将RSR[1,2]中的接收数据复制到接收缓冲寄存器RBR[1,2]。

3)将RBR[1,2]中的接收数据复制到数据接收寄存器DRR[1,2]。

4)TMS320C54x或DMA控制器从DRR[1,2]中读出数据。

McBSP的工作模式有多种:多通道缓冲模式、SPI模式、A-bis模式、数据回路模式、GPIO模式、省电模式。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。