【摘要】:当模拟信号由A/D转换成数字信号后,往往都需要输入DSP作进一步处理。所以,一个较好的解决办法是利用小容量的FIFO作为两者之间的接口,对A/D采样数据先做一下缓冲,积累到一定数量,再向DSP发出中断申请,成批传送给DSP处理。

当模拟信号由A/D转换成数字信号后,往往都需要输入DSP作进一步处理。但是,A/D转换后的数据输出速率一般很难与DSP的I/O读操作速率精确配合。由于A/D采样速率是3M/s,DSP外部存储器时钟为100MHz,为了读到总线上的数据,DSP外部存储器读写时钟也必须控制在3MHz,结果只能大大降低了DSP的总线使用效率。

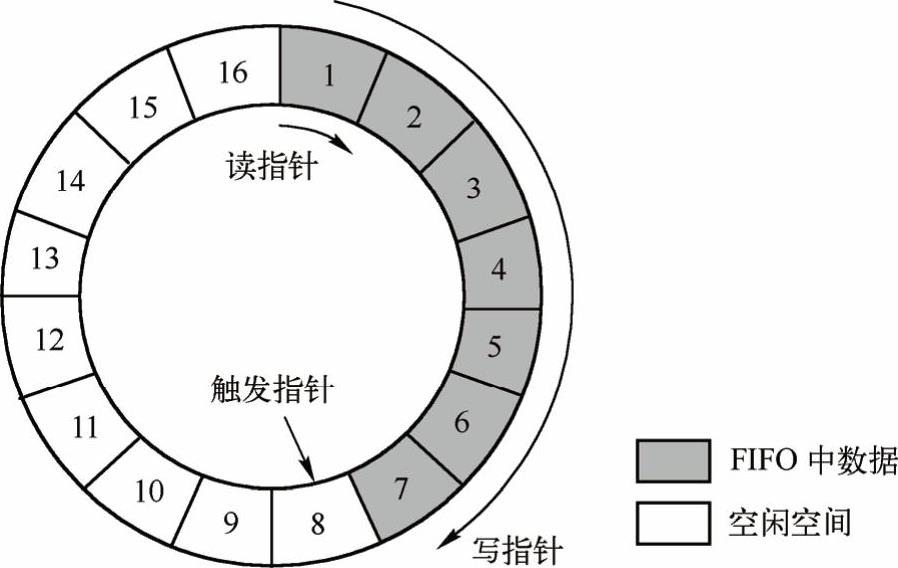

同时,再加上DSP需要一定的时间集中处理数据所读回的数据,过于频繁的总线操作会持续打断正进行的处理,效率降低。所以,一个较好的解决办法是利用小容量的FIFO作为两者之间的接口,对A/D采样数据先做一下缓冲,积累到一定数量,再向DSP发出中断申请,成批传送给DSP处理。恰好THS1206内置了一个FIFO循环缓冲队列,如图7-23所示。

图7-23 THS1206内置FIFO循环队列

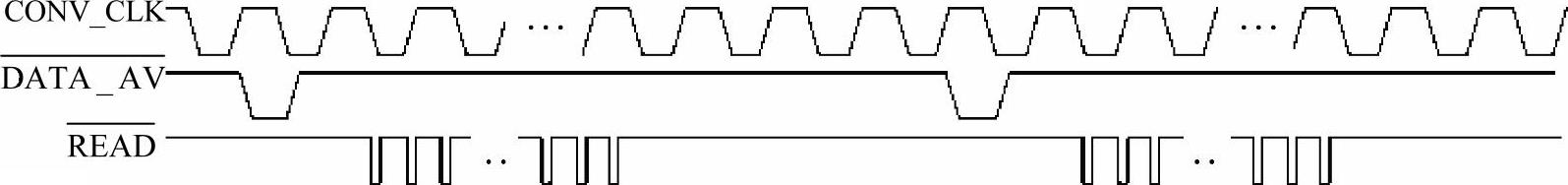

THS1206内置FIFO的读取时间可以达到每次10ns,读取时序如图7-24所示。

图7-24 THS1206内置FIFO的读取时序

我们可以事先设置数据有效深度,例如设定为9,当THS1206转换完成9个有效数据之后,就会通过 DATA_AV信号向DSP发出中断申请,DSP就可以集中连续读取9个有效数据。

DATA_AV信号向DSP发出中断申请,DSP就可以集中连续读取9个有效数据。

1.使用C编程实现DSP高速采样程序

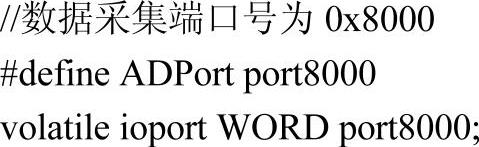

使用C语言编写实现DSP高速采样的C程序源代码ccd.c如下:

(https://www.xing528.com)

(https://www.xing528.com)

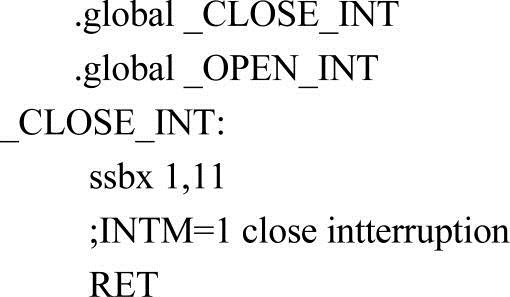

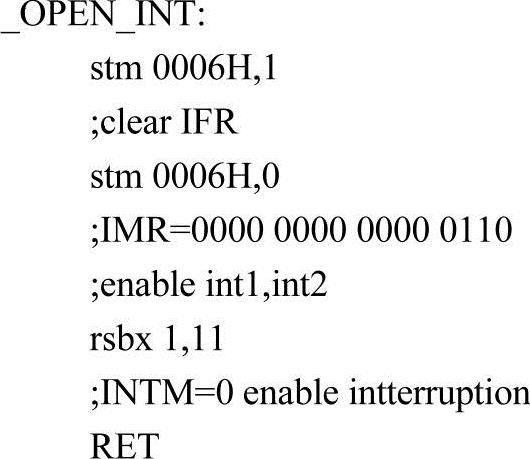

2.使用汇编编程实现DSP高速采样子程序

使用汇编语言编写实现DSP高速采样的汇编子程序源代码fcmd.asm如下:

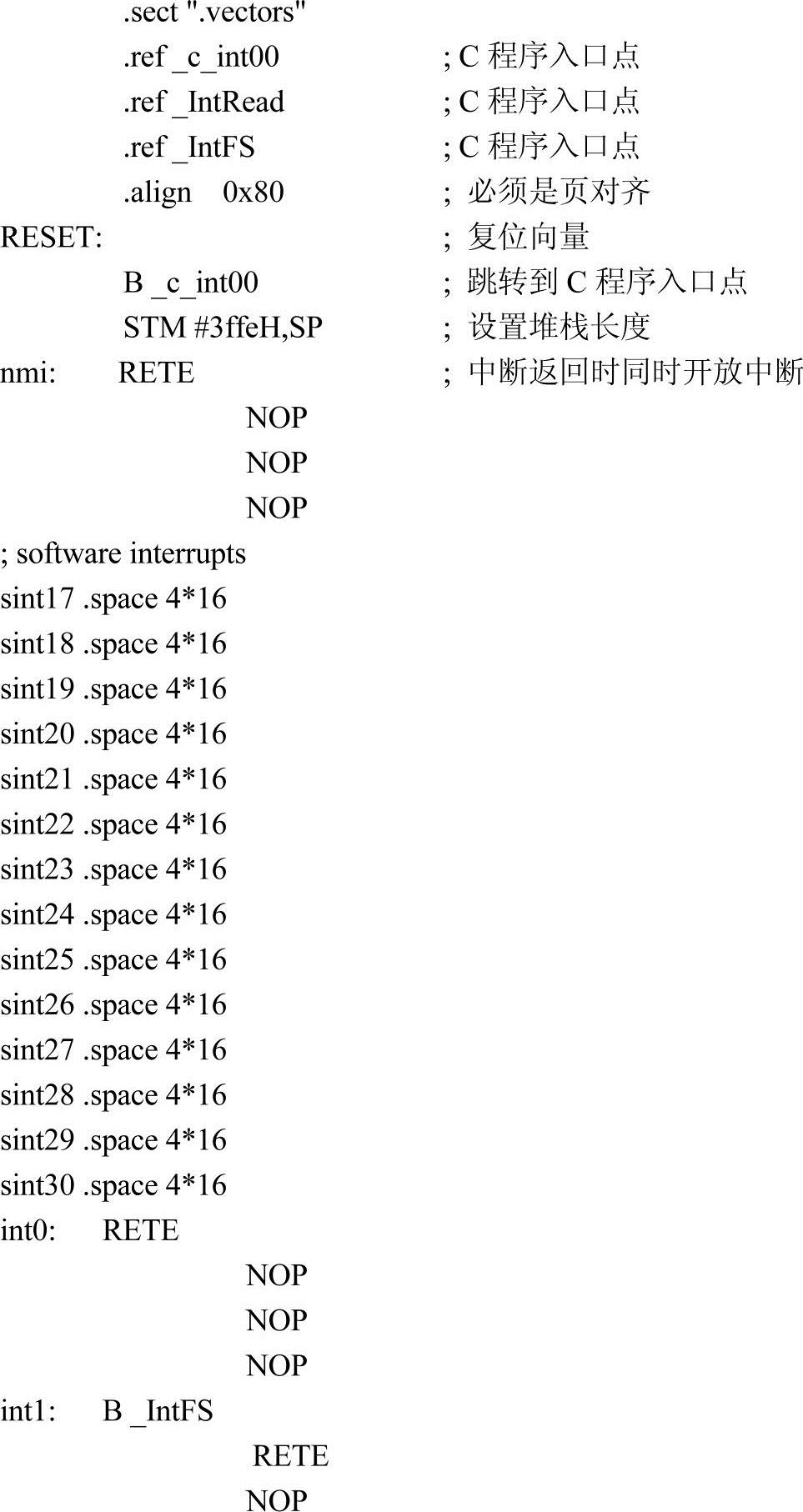

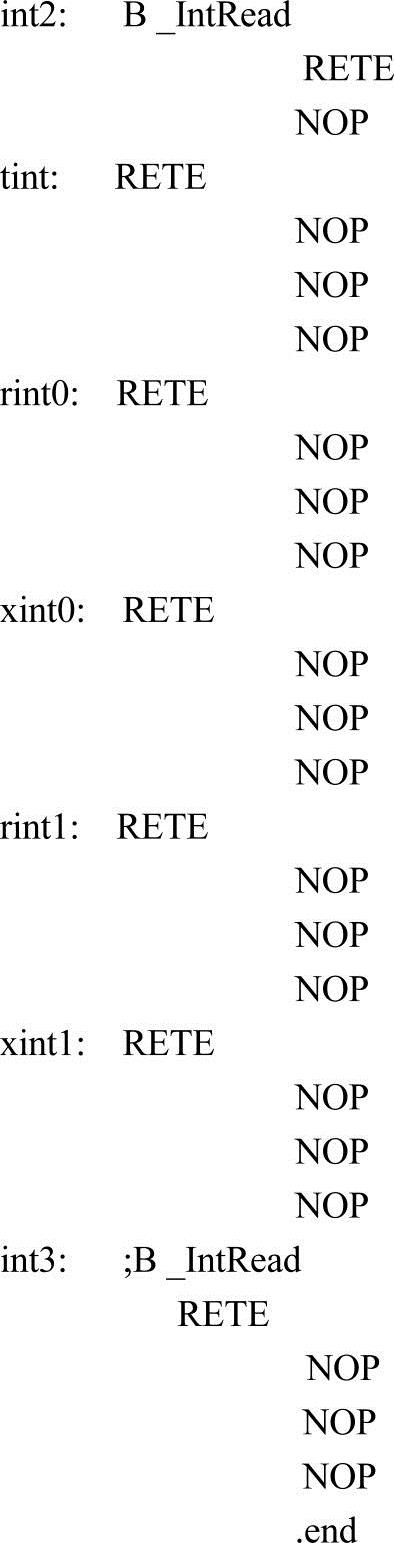

3.使用汇编编程实现DSP高速采样的中断向量文件

使用汇编语言编写实现DSP高速采样的中断向量文件源代码vector.asm如下:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。