高速采样硬件设计的重点,一是DSP外扩接口;另一个是高速A/D采样信号设计。

1.DSP外扩接口设计

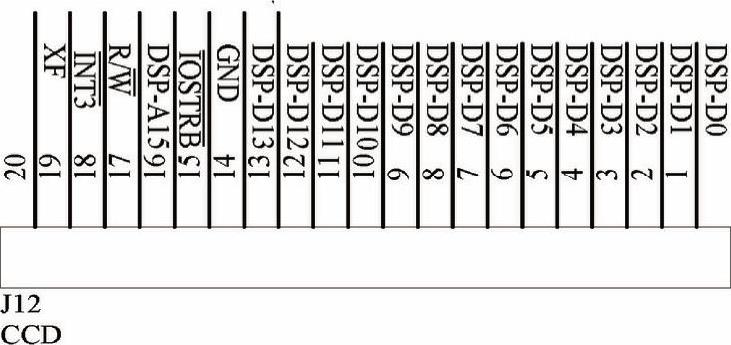

DSP外扩接口设计中,把A/D电路映射为TMS320VC5402系统I/O空间的外设,以TMS320VC5402系统I/O空间的总线信号控制A/D的工作。TMS320VC5402外扩接口中汇总了双向数据传输总线D0~D15、地信号GND、I/O空间读写数据有效信号 、读写方向信号R/W

、读写方向信号R/W 、地址信号A15、外部中断信号

、地址信号A15、外部中断信号 等,用于控制A/D完成信号采样工作。正常采样时,数据总线、地址总线、读写信号可完成TMS320VC5402与A/D芯片的数据双向传输;A/D转化数据帧完成后可通过

等,用于控制A/D完成信号采样工作。正常采样时,数据总线、地址总线、读写信号可完成TMS320VC5402与A/D芯片的数据双向传输;A/D转化数据帧完成后可通过 向TMS320VC5402提出中断申请。此外,使用外部通用I/O控制信号XF作为A/D采样的开始/停止转换指示信号。两者互联的接口电路如图7-17所示。

向TMS320VC5402提出中断申请。此外,使用外部通用I/O控制信号XF作为A/D采样的开始/停止转换指示信号。两者互联的接口电路如图7-17所示。

2.A/D采样电路设计

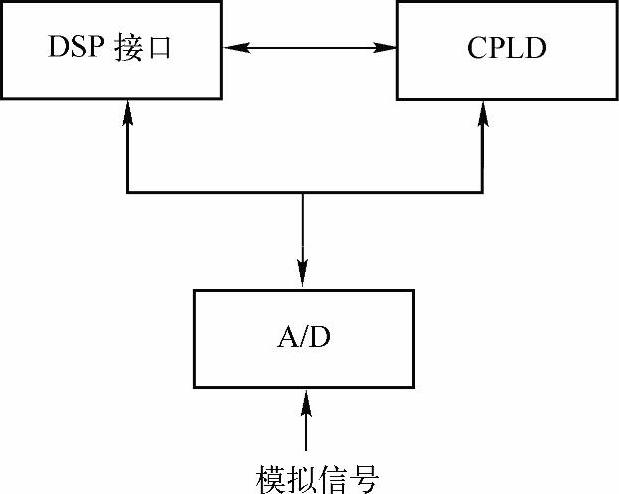

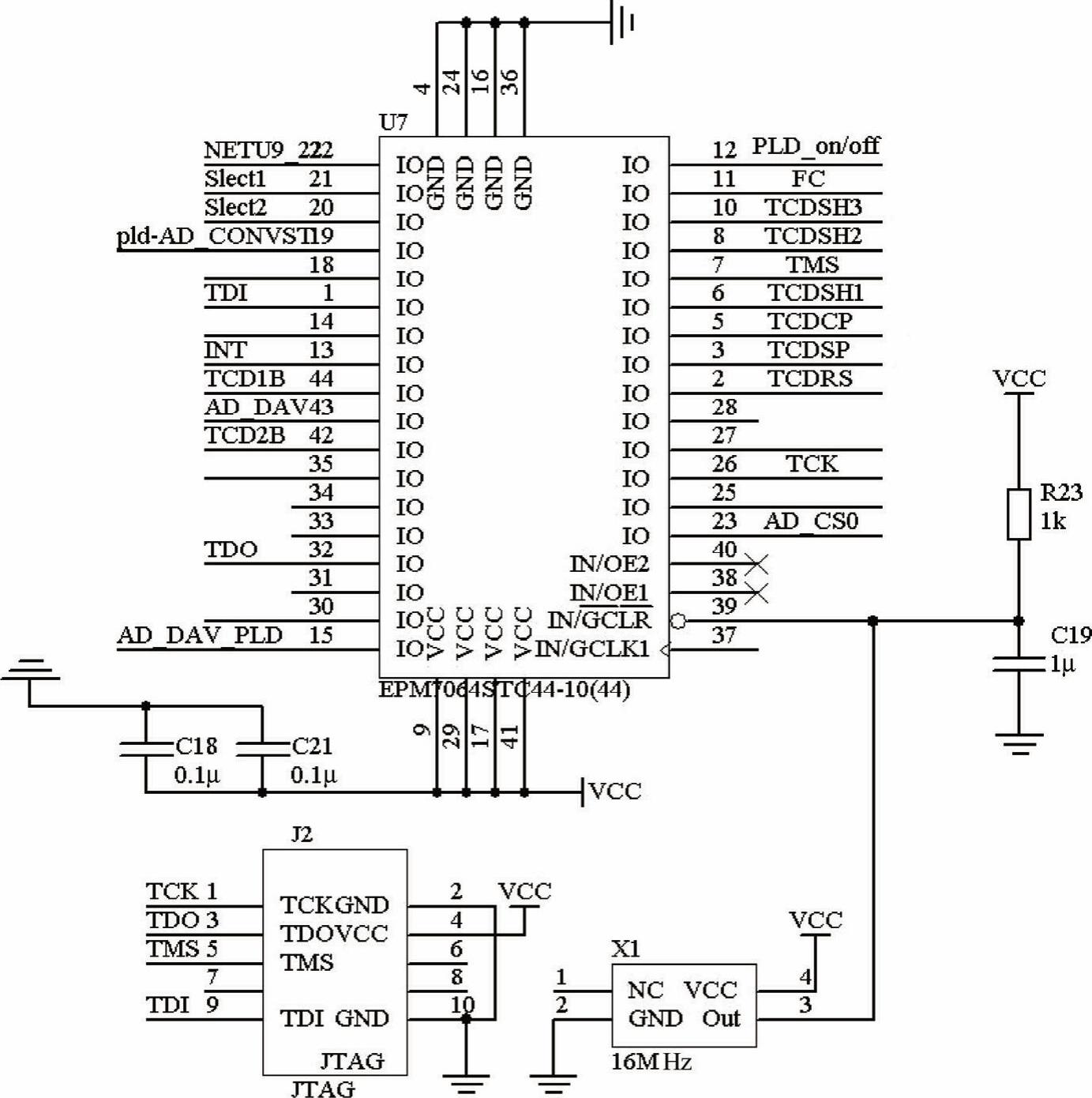

A/D采样电路设计结构如图7-18所示,A/D采样电路是DSP的外设,DSP作为主控CPU通过接口控制A/D的工作;CPLD作为辅助逻辑译码,在TMS320VC5402开始信号的指示下,为A/D采样芯片提供时序驱动信号。

图7-17 DSP外扩接口信号

图7-18 A/D采样电路设计结构

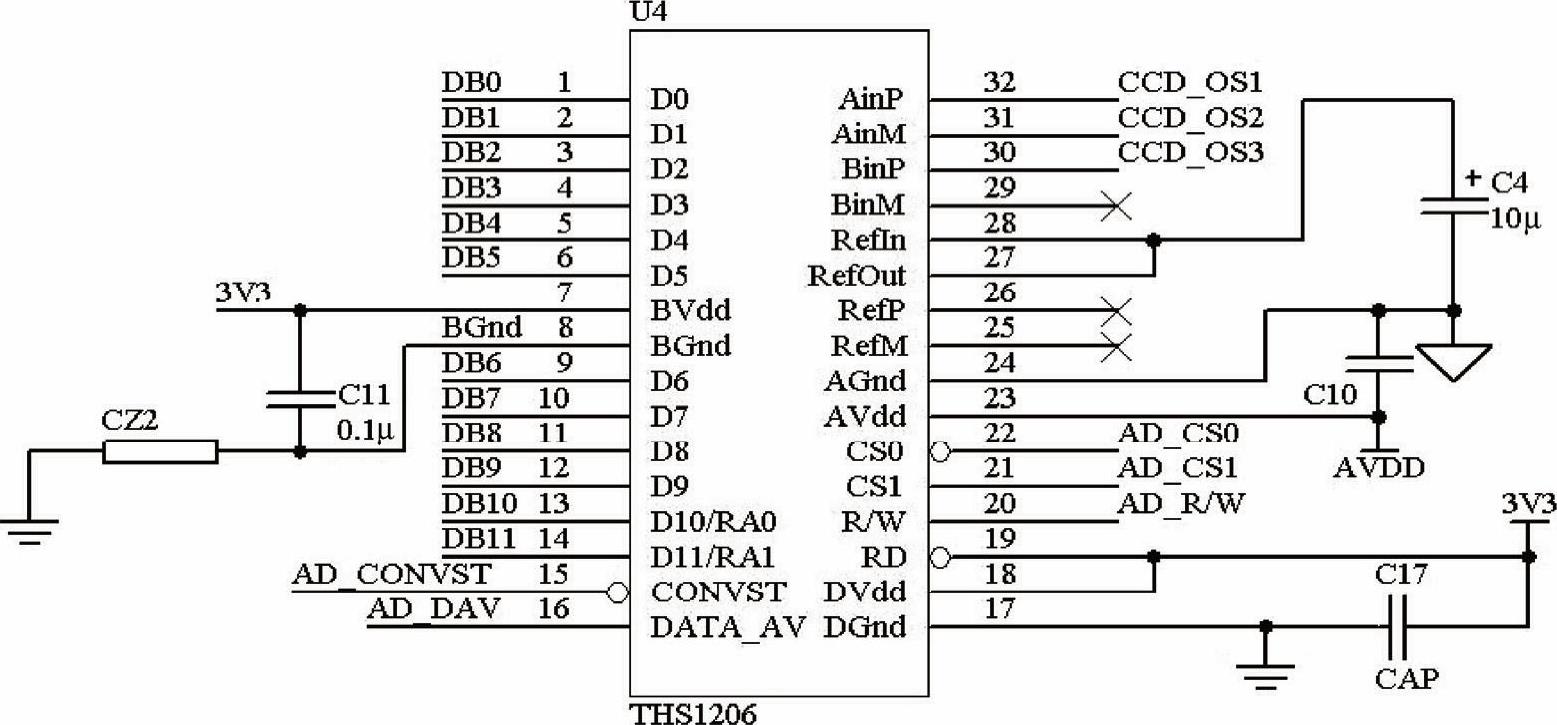

A/D转换器选用的是TI公司的THS1206。THS1206是一个CMOS、低功耗(最大216mW)、12位、最高可达6MHz采样率的模数转换器。THS1206拥有4个独立输入通道,可以被自动连续扫描;也可以编程实现差分输入。THS1206内置16个字深度的FIFO缓冲器;兼容3V或5V数字电平接口;允许内置或外部输入转换基准电压。THS1206内部有配置寄存器,用户可以根据需要自行配置,使其工作于不同的模式。

在此高速采样设计中,THS1206有3路独立输入,工作于自动连续扫描模式,每路采样率为1MHz,转换完成后自动存入FIFO。当FIFO中有效数据超过9个时,THS1206向CPLD发出数据有效指示,再由CPLD向TMS320VC5402发出中断申请信号。

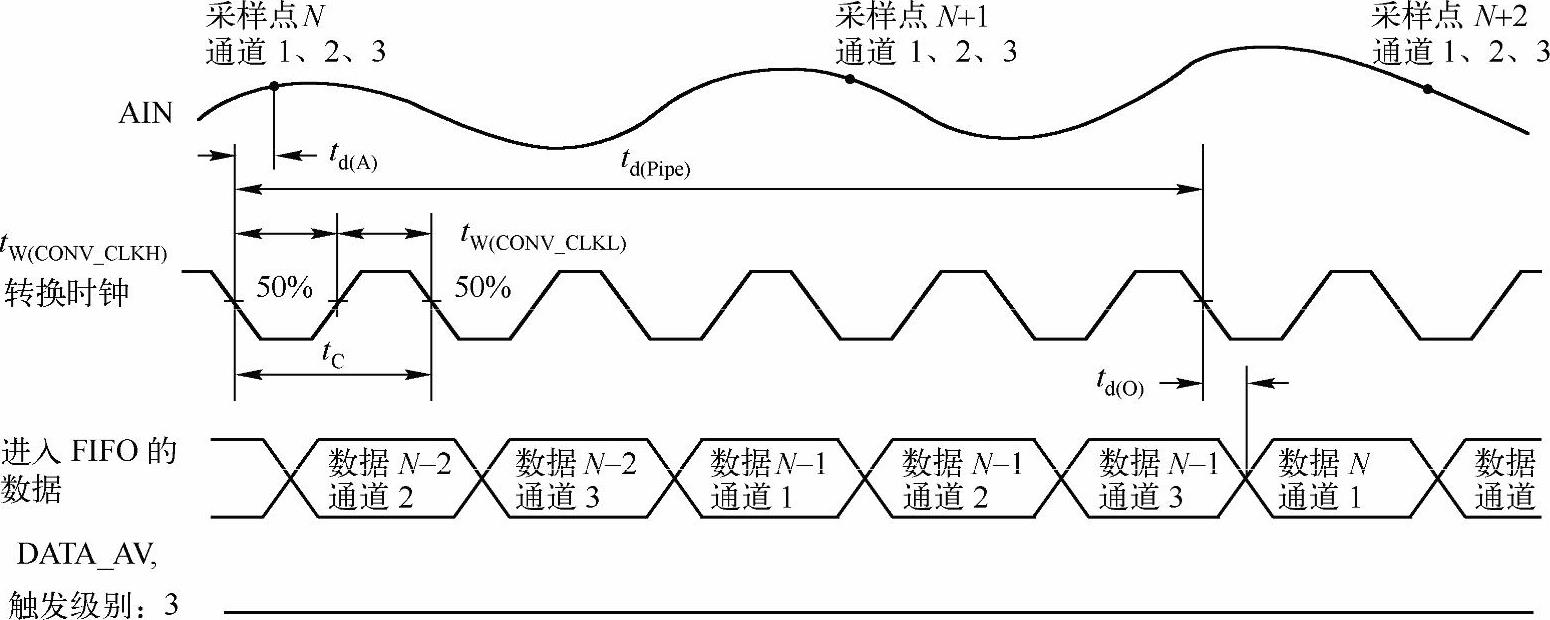

THS1206自动连续扫描3路模式下的时序如图7-19所示。(https://www.xing528.com)

转换脉冲CONV_CLK周期为3,在每个周期的第一个下降沿,同时采样保持3路模拟信号,第一路数据需要5个CONV_CLK之后完成。自动连续扫描状态下,模/数转换以流水线方式工作,在每个上升沿保存转换完成的有效数据到FIFO,所以长时间平均下来,一次转换只需要一个CONV_CLK脉冲周期。CPLD提供的CONV_CLK脉冲频率为3MHz。

图7-19 THS1206自动连续扫描3路模式下的时序

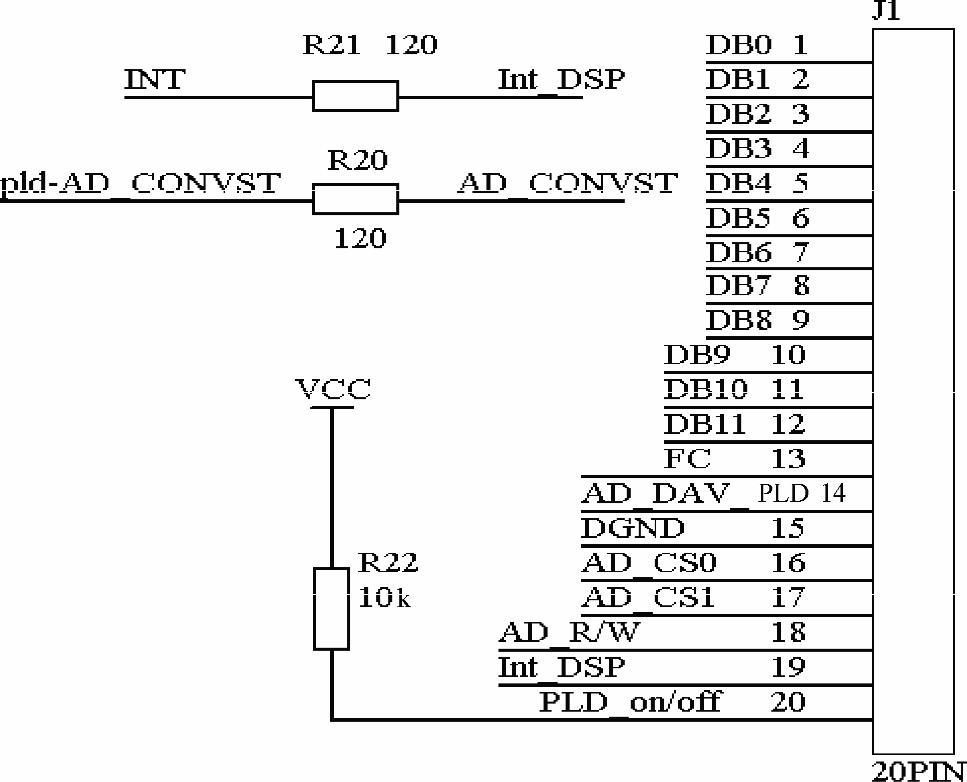

图7-18中所示三个组成部分的具体硬件设计如图7-20~图7-22所示,三者整合在一起,作为TMS320VC5402系统的高速A/D采样外设电路。

图7-20 A/D模块与DSP的接口信号

图7-21 A/D采样芯片的电路驱动设计

图7-22 CPLD对A/D时序驱动电路设计

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。