DSP最小系统的设计中,选用TMS320VC5402作为主控DSP,硬件设计部分主要包括以下4个方面。

(1)电源设计

系统选用的核心处理器TMS320VC5402,内核电压和片上I/O接口供电电压分别为1.8V和3.3V,由于系统采用的是5V统一供电,因此可通过稳压芯片调节产生内核和I/O接口需要的1.8V和3.3V电压。

(2)FLASH接口设计

设计FLASH与DSP接口时,主要解决以下几个问题:

1)通过DSP仿真系统,能够将程序和数据写入FLASH中。

2)系统独立运行时,能够从FLASH读出程序装入RAM。

3)接口尽量简单。

(3)SRAM设计

外扩一定数量的SRAM,合理映射地址空间、配置访问时间,利于DSP高效读写暂存数据。

(4)DSP其他外围设计

DSP设计主要考虑以下几个方面:

1)DSP工作时钟。为发挥DSP高速数字信号处理的优势,应该仔细考虑其工作主频。

2)复位电路。设计复位电路能够保证上电复位自动执行设计者的启动代码。

3)外部存储器空间分配。

4)外接口扩展。

1.电源设计

由于DSP系统工作频率高,数据吞吐量大,功耗也相对较高,因此供电系统的好坏将直接影响到系统的稳定性,所以设计高效率高性能的供电系统具有极其重要的意义。

TMS320VC5402的内核和片上I/O接口供电电压分别为1.8V和3.3V。因此需要考虑它们的配合问题。在加电过程中,如果只有内核获得供电,片上I/O接口没有得到供电,对处理器不会产生任何伤害,只是对外没有输入/输出能力而已;相反,如果片上I/O接口供电先于内核加电,则有可能会导致内核逻辑和片上I/O引脚同时作为输出端,此时如果双方输出的逻辑电平是相反的,那么两输出端就可能会因反向驱动产生一个瞬时大电流,这将影响器件的使用寿命,甚至会损坏器件。同样,在关闭电源时,如果内核先掉电,也有可能产生大电流。因此,在加电过程中,至少要保障内核电源CVdd先于片上I/O接口电源DVdd(至少是同时)加电,当然最好是内核电源CVdd先加电;相反,关闭电源时,最好先关DVdd,再关CVdd。

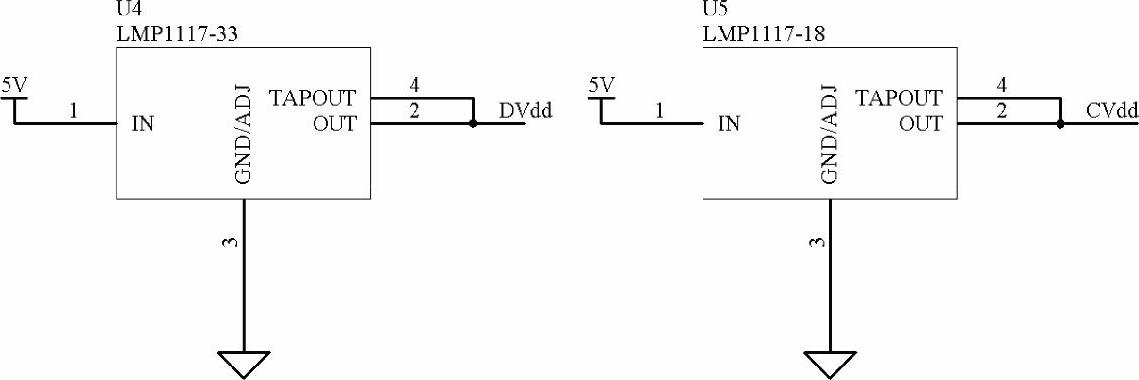

电源设计图如图7-2所示。由图可知,系统采用5V供电,并采用线性稳压方式得到3.3V和1.8V两种电压,采用LM1117系列的稳压芯片。该设计方案硬件电路设计简单,成本低,电压谐波小,功耗低。上电时,DSP内核和片上I/O可以同时上电,完全可以满足DSP的上电次序要求。

LM1117系列的低压差线性调压器,在负载电流为800mA时压差为1.2V,并提供过电流保护和热保护,而且输出电流大,线性度高,负载大,市场零售价仅为一元左右,具有极高的性价比。

图7-2 电源设计图

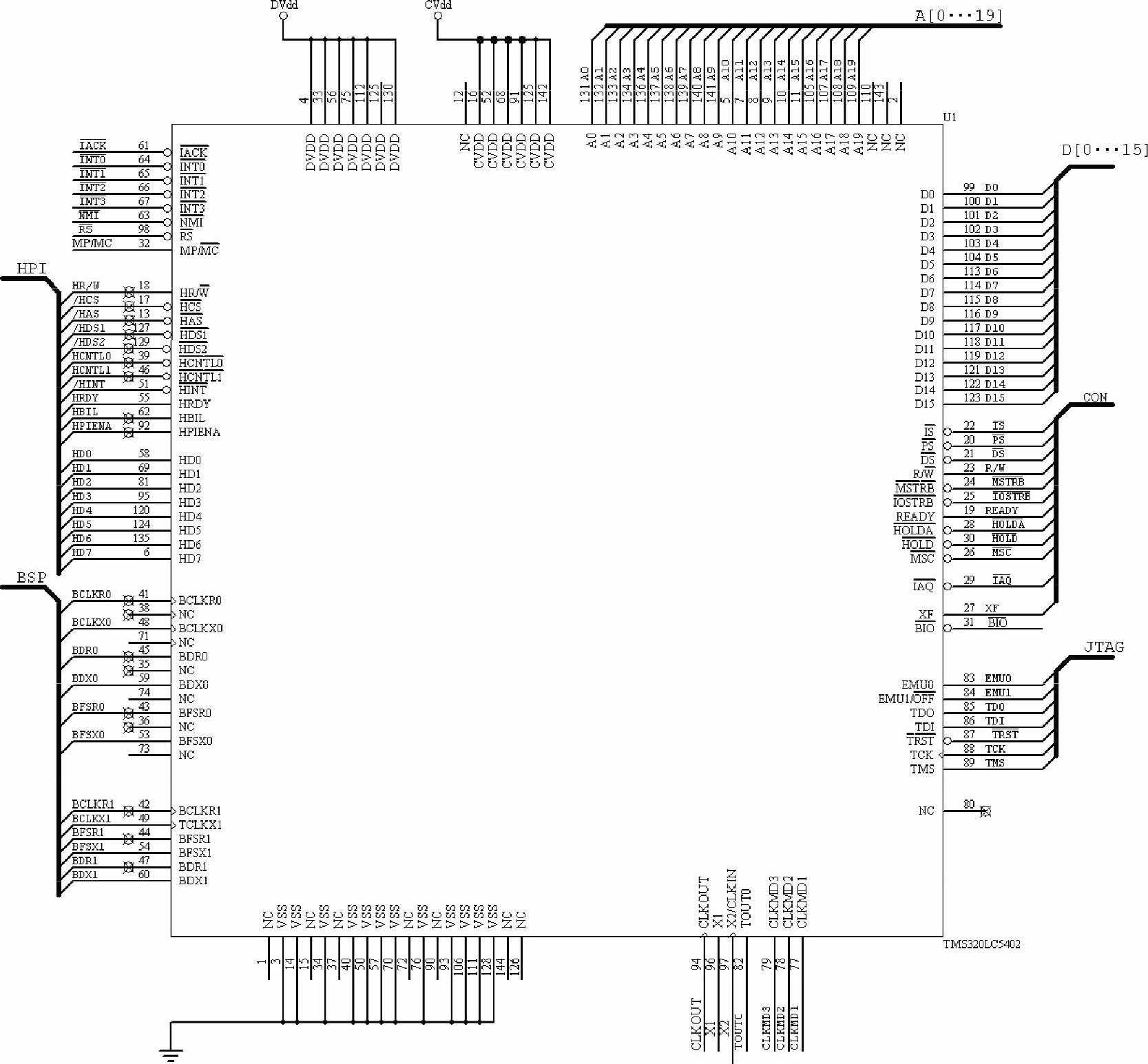

2.DSP设计

工作时钟的设定:外部输入的时钟经过倍频以后,产生CPU的工作时钟以及同步接口所需的时钟信号,时钟信号的好坏直接决定了系统的稳定性,TMS320VC5402提供了内部和外部两种方式的时钟发生模式。本系统采用的是外部振荡方式,如图7-3所示。其中晶体振荡器的频率为10MHz,因为TMS320VC5402的工作频率为100MHz,采用倍频系数为10的时钟模式。即CLKMD1、CLKMD2、CLKMD3分别设置为“0”、“0”、“1”。TMS320VC5402各时钟模式见表3-16。

3.SRAM与DSP的接口设计

TMS320VC5402片内自带了64K×16bit的RAM,其中一部分用来运行程序,另外一部分可以用来存储数据,但在进行大量运算时,片内的RAM存储器不能满足数据存储容量的要求,因此还要扩充一部分RAM。

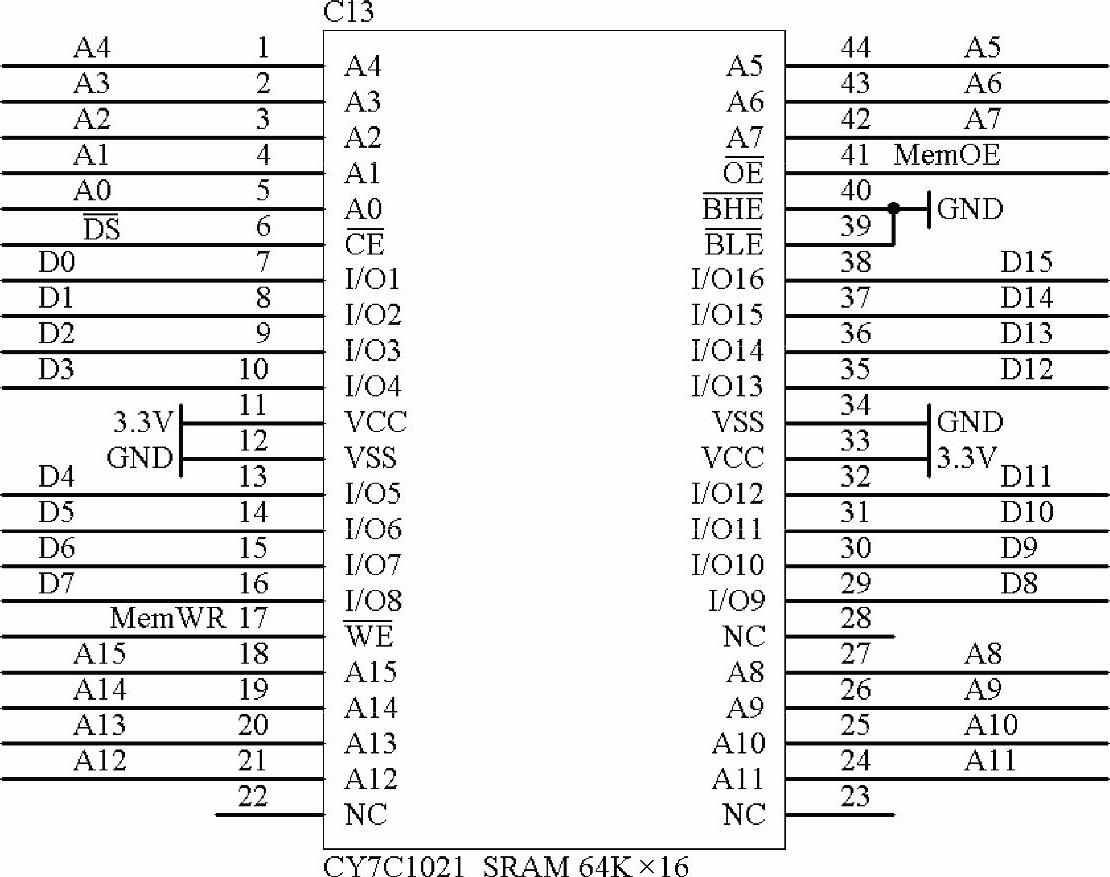

考虑到本系统所涉及的各软件算法对系统外部存储器容量的要求,以及SRAM的访问速度、价格因素等问题,本系统采用Cypress公司生产的CY7C1021 SRAM芯片作为外部扩充的数据存储器。CY7C1021的存储器容量为64K×16bit,基本可以满足各种软件算法对系统外部数据存储器容量的要求。采用CMOS工艺,具有自动低功耗模式功能,能高效地降低系统功耗和保证低散热量。工作电压为3.3V,与TMS320VC5402工作电压一样,因此便于电路设计。CY7C1021读操作时间为10/12/15ns。激活时功耗最大为576mW,不处于操作状态时,能自动置于省电模式,省电模式功耗为18mW。

图7-3 TMS320VC5402主处理器信号连接图

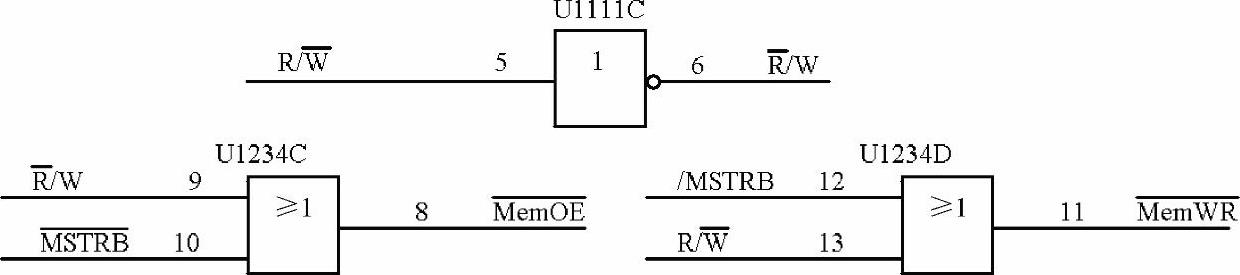

CY7C1021存储器的信号定义有别于TMS320VC5402的读写信号,其区别关键在于读写控制信号上,两者互联需要重新构造读写控制信号,如图7-4所示。

图7-4 存储器与TMS320VC5402接口读写信号连接图

CY7C1021连接到TMS320VC5402作为其外部数据存储器,如图7-5所示。CY7C1021的地址和数据总线连接到TMS320VC5402的外部总线。片选信号 与TMS320VC5402的

与TMS320VC5402的 相连;

相连; 与图7-4中的

与图7-4中的 连接,当

连接,当 为低电平时,可对SRAM进行编程和擦除操作;OE与图7-4中的MemOE相连,当

为低电平时,可对SRAM进行编程和擦除操作;OE与图7-4中的MemOE相连,当 为低电平时,可对SRAM进行读操作。

为低电平时,可对SRAM进行读操作。

图7-5 SRAM与TMS320VC5402接口连接图

4.FLASH与DSP的接口设计

在能脱离开发环境独立运行的DSP系统中,一定有非掉电丢失数据的存储芯片存在,比如选用ROM或FLASH存储用户代码,这样才能保障系统在加电后自动装载运行。目前大多采用可重复擦写的FLASH器件,方便设计开发。

FLASH存储器是在EPROM和EEPROM的基础上发展起来的一种高密度、非易失性的电可擦写存储器,在掉电情况下仍能保证数据不丢失,并能够在不离开电路板或拆卸设备的情况下实施擦除和再编程操作。它具有结构简单、维护便利、存取速度快、对环境适应能力强、抗震性能好等优点,而且单位存储比特的价格比传统的EPROM要低。十分适合于低功耗、小尺寸和高性能的便携式系统。对它的编程操作,除了可以采用专用的硬件编程器把代码烧写到FLASH中之外,也可以很方便地利用在线编程技术来实现。(https://www.xing528.com)

接着就要考虑具体FLASH存储器型号的选择问题。在考虑到本系统所涉及的各种软件算法对系统外部程序存储器容量的要求、FLASH与DSP运算速度的匹配问题、FLASH与DSP间的电压兼容问题和节约成本等问题的基础上,本设计选择AMD公司的AM29LV800B FLASH芯片,原因如下:

TMS320VC5402最高可工作在120MHz,但系统的测试实例设计工作主频为100MHz(外部时钟源的频率为10MHz,内部进行10倍频),其指令周期为10ns,外部存储器寻址需要2个指令周期,可软件插入0~7个等待周期,所以在不添加硬件等待时序的情况下,读写时间为20~90ns的外存储器都可以直接与DSP直接相连。

AM29LV800B的存储器容量为1M×8bit,基本可以满足各种软件算法对本系统外存储器容量的要求;访问速度为70ns,可以无需硬件等待时序电路直接与DSP连接;供电电压为3.3V,所以省去了数据和地址线的缓冲和电平变换;市场售价非常便宜,具有很高的性价比。FLASH在系统中映射为DSP的片外程序存储空间数据。

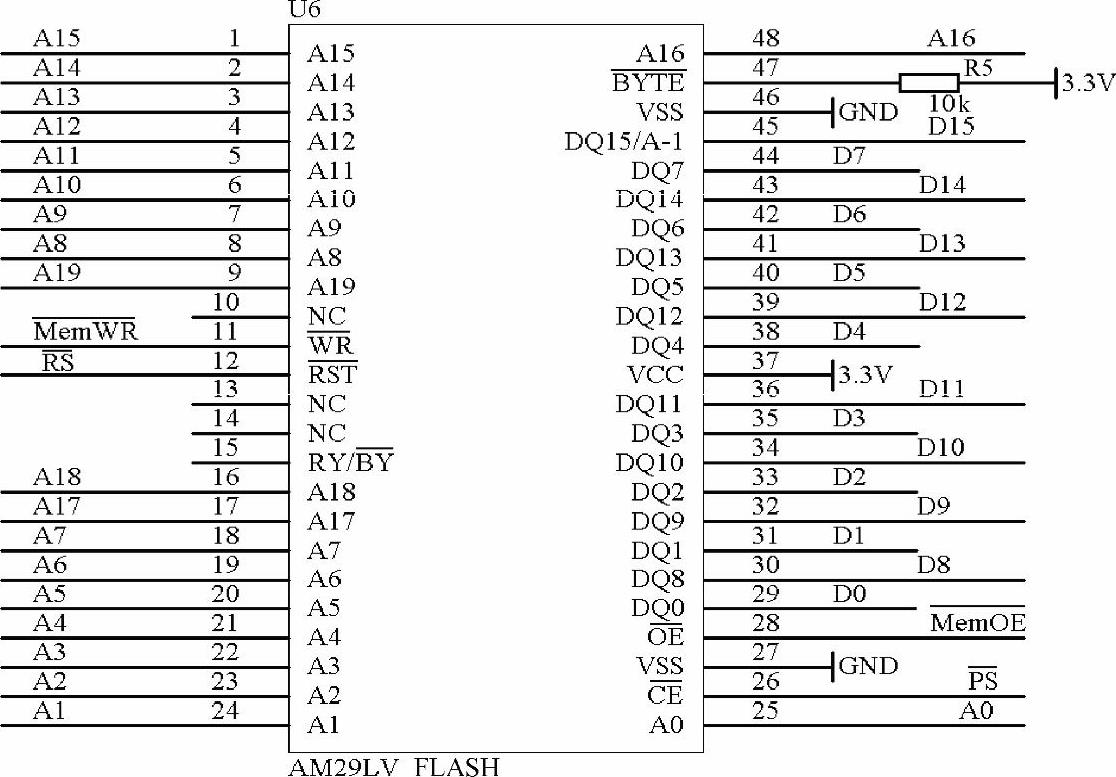

FLASH与TMS320VC5402的硬件接口连接设计:

与之前的CY7C1021存储器连接方式同样的考虑,AM29LV800B连接到TMS320V-C5402作为其外部程序存储器,如图7-6所示。

图7-6 AM29LV800B与DSP连接图

AM29LV800B的地址和数据总线连接到TMS320VC5402的外部总线。片选信号CE与TMS320VC5402的 相连;

相连; 与图7-4中的

与图7-4中的 连接,当

连接,当 为低电平时,可对闪存进行编程和擦除操作;OE与图7-4中的

为低电平时,可对闪存进行编程和擦除操作;OE与图7-4中的 相连,当

相连,当 为低电平时,可对FLASH进行读操作。

为低电平时,可对FLASH进行读操作。

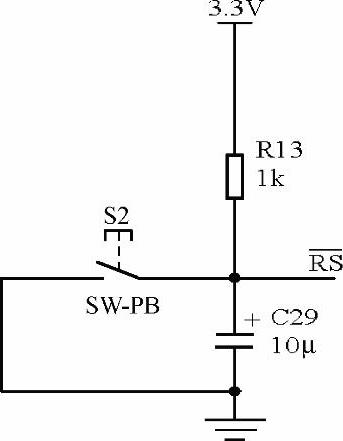

5.复位电路设计

复位电路对DSP系统非常重要,为了保证DSP在电源未达到要求的电平时不会出现不受控制的状态,就必须在系统中加入复位电路。在系统加电过程中,当内核电压和外围端口电压未达到要求的电平时,复位电路确保DSP始终处于复位状态。同时,电源电压一旦降到门限值以下,复位电路就会强制DSP进入复位状态,从而确保系统稳定工作。

对于复位电路的设计,一方面应确保复位的低电平时间足够长(一般需要20ms以上),保证DSP可靠复位;另一方面应确保电路具有良好的稳定性,防止DSP误复位。为了使系统能被复位信号正确初始化,复位信号的脉冲宽度必须至少为10个指令周期以上,TMS320VC5402的指令周期为10ns,则复位时间至少为10×10ns=100ns。同时要考虑到系统振荡器达到稳定工作状态至少需要20ms,复位电路至少需要产生10个机器周期,约为21ms低电平复位脉冲。设计时实际复位时间参数应大于21ms,复位电路如图7-7所示,该电路具备手动和自动复位功能。

图7-7 RC复位电路图

6.JTAG接口

20世纪70年代末,由于电子技术的发展,PC的密度增加,芯片封装变小,传统测试的局限性日益显现。在此条件下,人们提出了IEEEl149.1,即JTAG标准。此后,由于BGA封装的广泛使用,JTAG技术在板级测试中的优势越来越明显,逐渐为各处理器芯片厂商所采用。近年来,由于数据传输技术的进一步发展,JTAG应用从直流连线网络扩展到交流耦合连线网络,并提出了新的数模混合测试标准口。同时,片上系统(System On a Chip,SOC)的发展和千兆时钟的采用,使得在设计中,信号完整性问题成为瓶颈,噪声和延迟常常导致系统功能降低,以至失效。使用扩展后的JTAG技术,对测试信号完整性有很大帮助。此外,JTAG技术在SOC中的重要应用还包括嵌入式仿真器和调试模块的设计。这种设计可以提高内部信号的可控性和可观性,缩短产品开发周期,提高查错效率。

JTAG硬件电路结合仿真器和仿真软件(Emulator),可以访问DSP内部的所有资源,包括片内寄存器以及所有的存储器,从而可提供实时硬件在线仿真与调试的环境,便于开发人员进行系统软件调试。

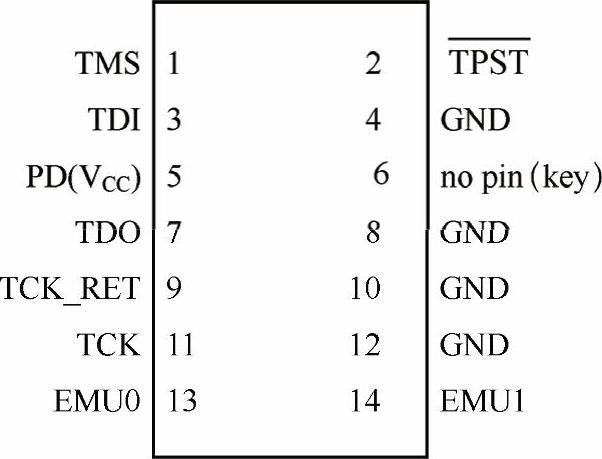

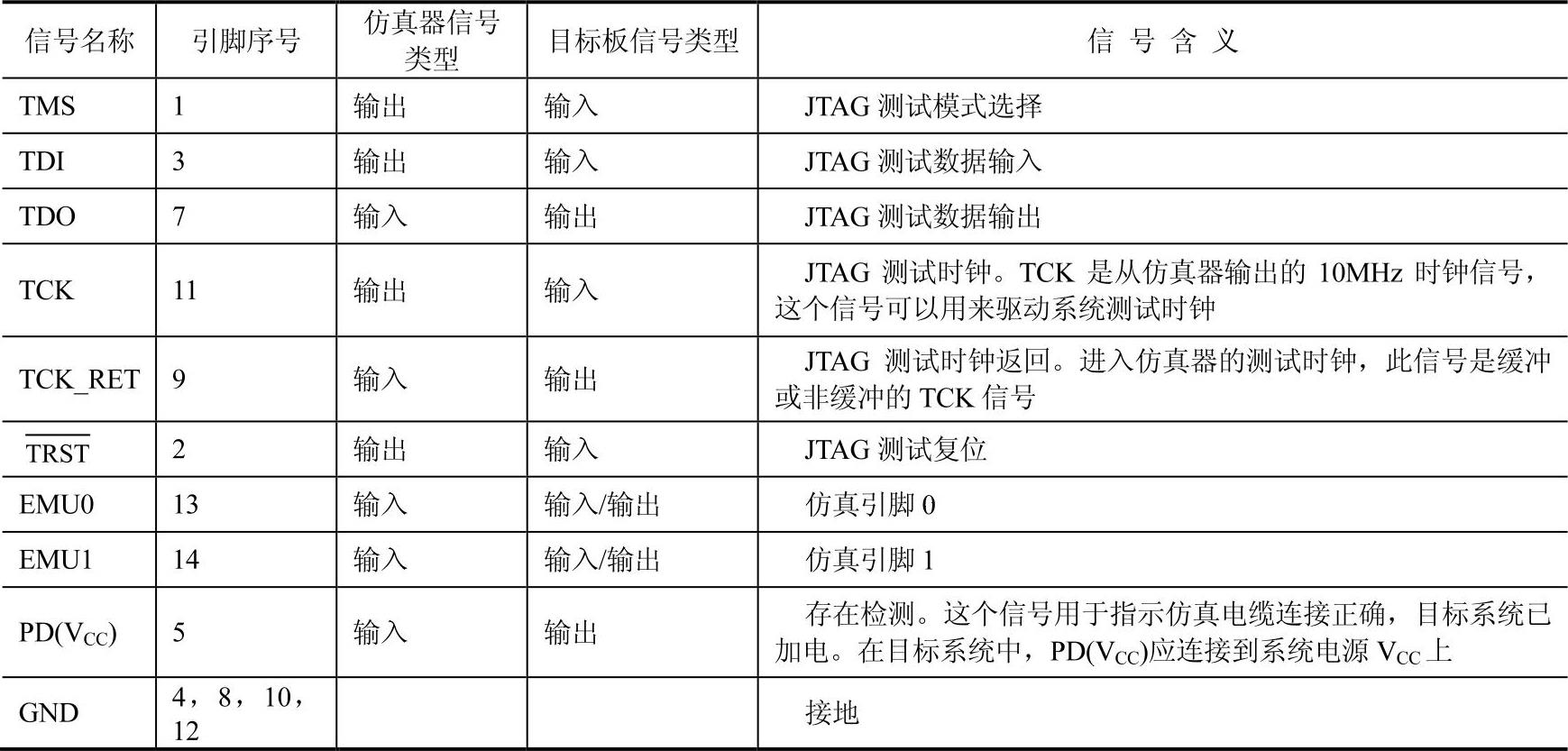

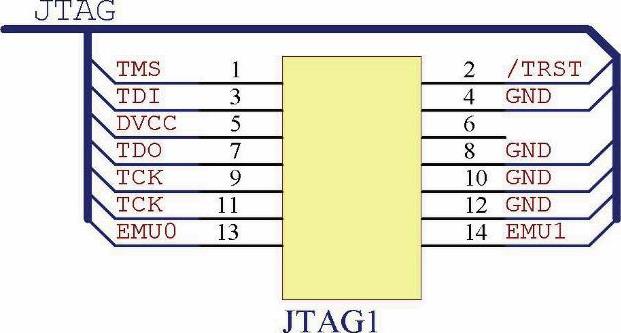

仿真器通过一个14针的接口与DSP的JTAG端口进行通信。图7-8是JTAG14针接口上的信号定义。表7-1列出了JTAG接口的各信号含义。

图7-8 JTAG14针接口上的信号定义

表7-1 JTAG接口信号含义

TMS320VC5402提供了片上的JTAG接口,为方便仿真调试,只需将TMS320VC5402的关键信号TMS、TDO、TDI、 、TCK、EMU0、EMU1共7个引脚接出,做成一个如图7-8所示的标准的14针插座,就可以供仿真器调试目标板。最小系统硬件板上JTAG仿真接口实现电路如图7-9所示。

、TCK、EMU0、EMU1共7个引脚接出,做成一个如图7-8所示的标准的14针插座,就可以供仿真器调试目标板。最小系统硬件板上JTAG仿真接口实现电路如图7-9所示。

需要注意的是,为防止接口插件在连接时出现位置插错的现象,TI公司DSP的JTAG连接器要求第6引脚是没有插针的(同样道理,仿真器的JTAG连接线的连接器头的第6引脚没有针孔)。连接器插反会存在将仿真器烧毁的风险。为保障信号的完整性、电路工作的可靠性,TI公司DSP的仿真器JTAG连接线的长度有一定的限制,一般不超过15.24cm(6in)。

7.预留外扩展接口

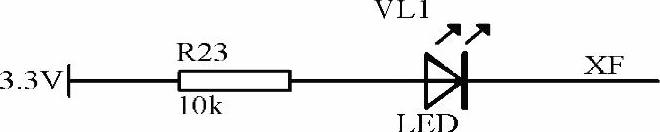

本系统在XF引脚上接了一个LED指示灯,可通过编程更改XF的电平状态,控制灯的亮与灭,如图7-10所示。

图7-9 JTAG连接图

图7-10 LED连接图

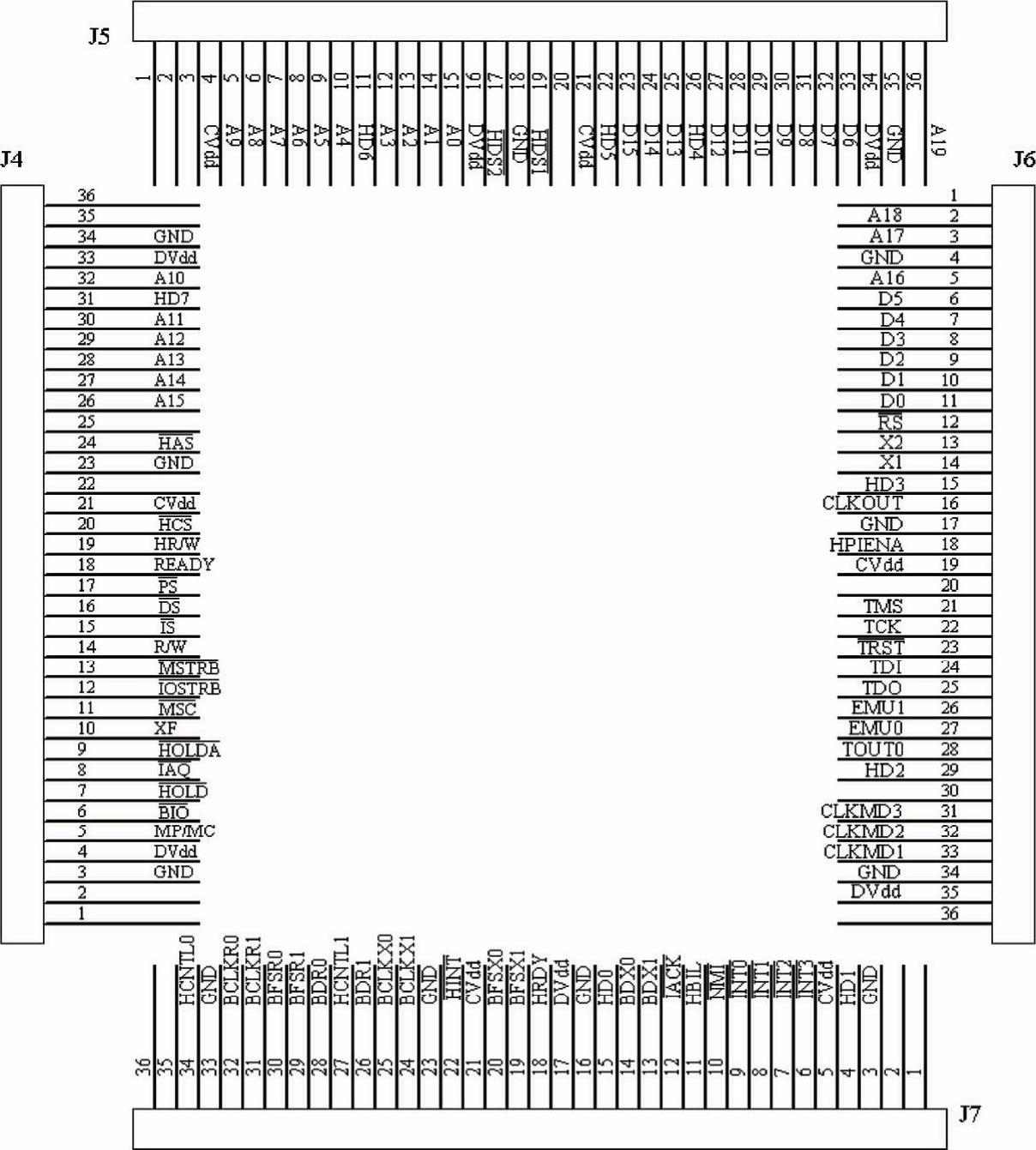

为了保障系统的对外接口的扩展性,在本系统设计中,把TMS320VC5402的所有引脚都连接到了总线插槽上,大大方便了外设扩展设计,如图7-11所示。

图7-11 预留外扩端口

8.硬件实物

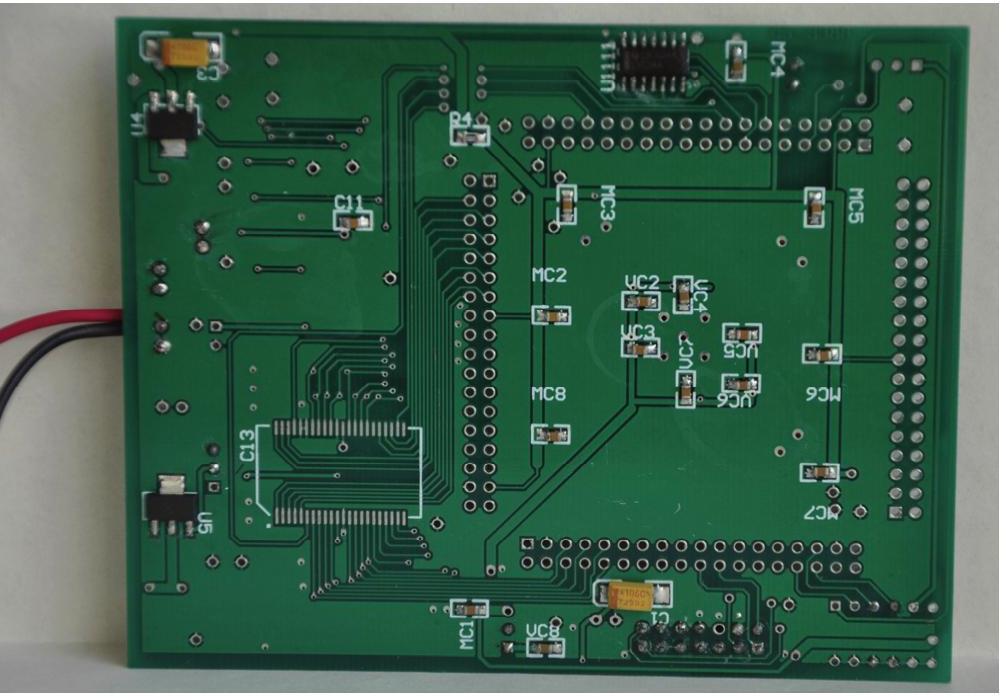

电路板实物图如图7-12、图7-13所示,经过实际检测,最小系统可以正常运行。

图7-12 实物正面

图7-13 实物反面

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。