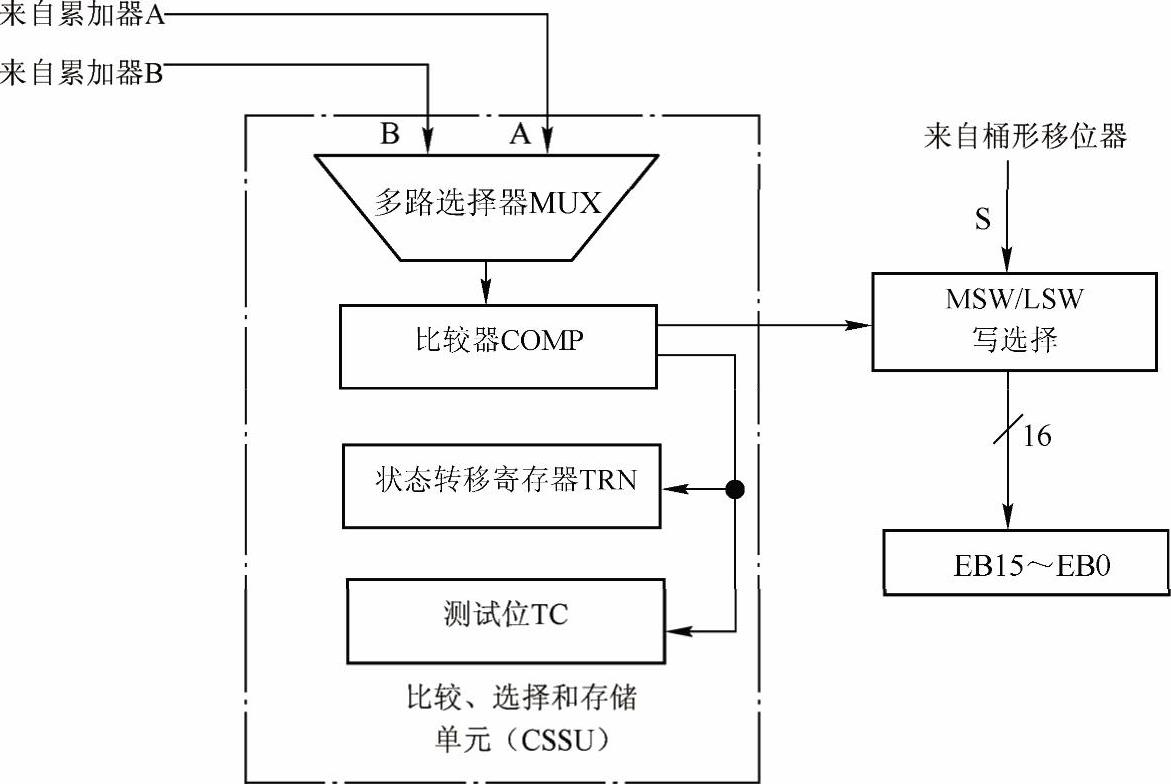

在数据通信、模式识别等领域,往往要用到Viterbi(维特比)算法。TMS320C54x中的比较、选择和存储单元(CSSU)就是专门为Viterbi算法设计进行加法/比较/选择(ACS)运算的硬件单元,其功能框图如图3-8所示。CSSU由多路选择器MUX、比较器COMP、状态转移寄存器TRN和测试位TC组成,它与ALU相配合实现快速ACS运算。

图3-8 比较、选择和存储单元的功能框图

CSSU主要完成累加器的高位字和低位字之间的最大值比较,即选择累加器中较大的字,并存储在数据存储器中,不改变状态寄存器ST0中的测试/控制标志位TC和传送寄存器(TRN)的值。CSSU的工作过程如下:首先比较电路COMP将累加器A或B的高位字与低位字进行比较,并将比较结果分别送入TRN的第0位和TC中,将比较结果记录下来以便程序调试,然后将比较结果输出至写选择MSW/LSW选择累加器中较大的16位数据,并将其通过总线EB存入指定的数据存储单元中。

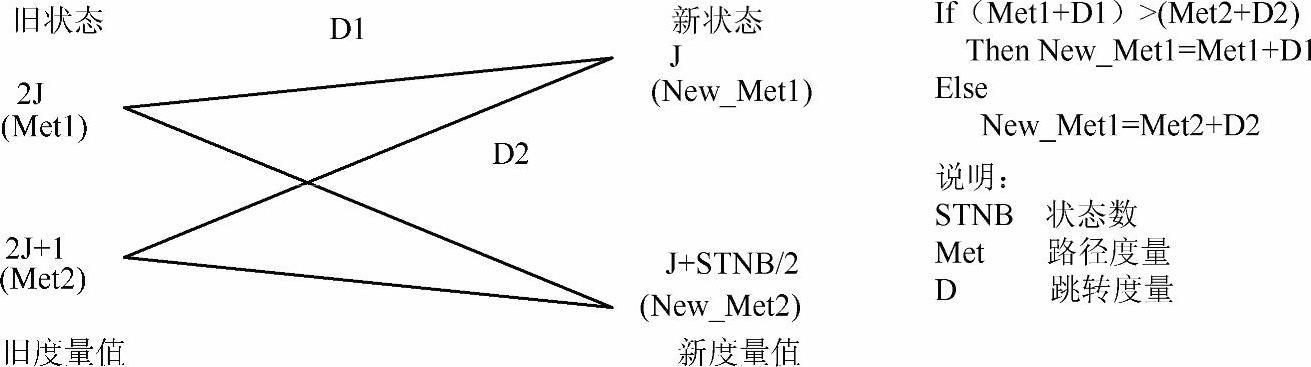

CSSU支持均衡器和信道译码器所用的各种Viterbi算法。图3-9给出了一种Viterbi算法的示意图。

(https://www.xing528.com)

(https://www.xing528.com)

图3-9 Viterbi算法

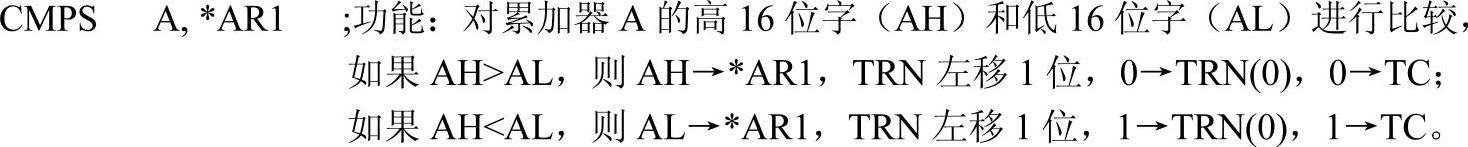

图3-9中所示的Viterbi算法包括加法、比较和选择3部分操作。其中加法运算是由ALU完成的。将状态寄存器ST1中的C16位置1,ALU就被配置成双16位工作方式。这样,就可以在一个机器周期内执行两次加法运算,其结果(Met1+D1和Met2+D2)都是16位数,分别存放在累加器的高16位和低16位中。然后CCSU通过CMPS指令完成比较、选择操作,也就是对累加器的高16位和低16位进行比较,并选择出较大的一个数存放到指令所指定的存储单元中。例3-5说明了由CMPS指令执行的比较和选择操作。

【例3-5】 CMPS指令的操作。

由此可见,在CMPS指令执行的过程中,状态转移寄存器TRN将自动地记录比较的结果,这在Viterbi算法中是有用的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。