TMS320C54xCPU内有两个40位的累加器A和B,它们用于存储ALU或乘法器/加法器单元输出的数据,也能输出数据到ALU或乘法器/加法器中。

1.累加器结构

累加器A和B都可分为3部分,分别为保护位39~32(AG或BG)、高位字31~16(AH或BH)和低位字15~0(AL或BL),如图3-4所示。

图3-4 累加器A和B

其中,保护位作为计算时的高位余量位,用于防止在迭代运算(如自相关)中产生溢出,在进行有符号运算时为扩展符号位。AG、BG、AH、BH、AL、BL都是存储器映射寄存器,可以使用寄存器寻址的方式对其进行操作。在保存和恢复文本时,可以用PSHM或POPM指令将它们压入堆栈或者弹出堆栈。累加器A和B之间的唯一区别是累加器A的32~16位可以作为乘法器的一个输入,而累加器B不能。

2.带移位的累加器存储操作(https://www.xing528.com)

利用STH、STL、STLM和SACCD指令或并行存储指令,可将累加器的内容存入数据存储器中。在存储过程中,有时需要对累加器的内容进行移位操作。

要将累加器的16个最高有效位移位并存入存储器,可以使用STH、SACCD和并行存储指令。进行右移操作时,AG和BG中的各数据位分别移入AH和BH中;进行左移操作时,AL和BL中的各数据分别移入AH和BH中,而AL和BL的低位填0。

要将累加器的16个最低有效位移位并存入存储器,可以使用STL指令。进行右移操作时,AH和BH中的各数据位分别移入AL和BL中;进行左移操作时,AL和BL中填0。由于移位操作是在移位寄存器中进行的,累加器的内容保持不变。

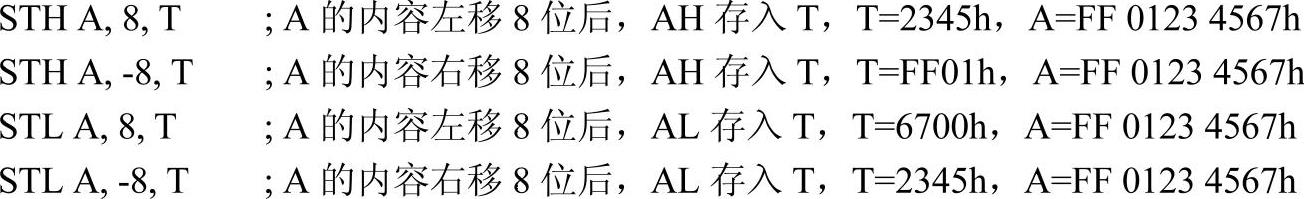

【例3-2】 累加器A=FF01234567h,执行带移位的STH和STL指令后,求暂存器T和A的内容。

TMS320C54x有一些专用的并行操作指令,有了它们,累加器可以实现一些特殊的运算。其中包括利用FIRS指令实现对称有限冲激响应(FIR)滤波器算法;利用LMS指令实现自适应滤波器算法;利用SQDST指令计算欧几里德距离以及其他的并行操作指令。该功能的好处是用一条指令就可以完成原本需要几条指令才能完成的操作,大大提高了执行复杂算法的速度。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。