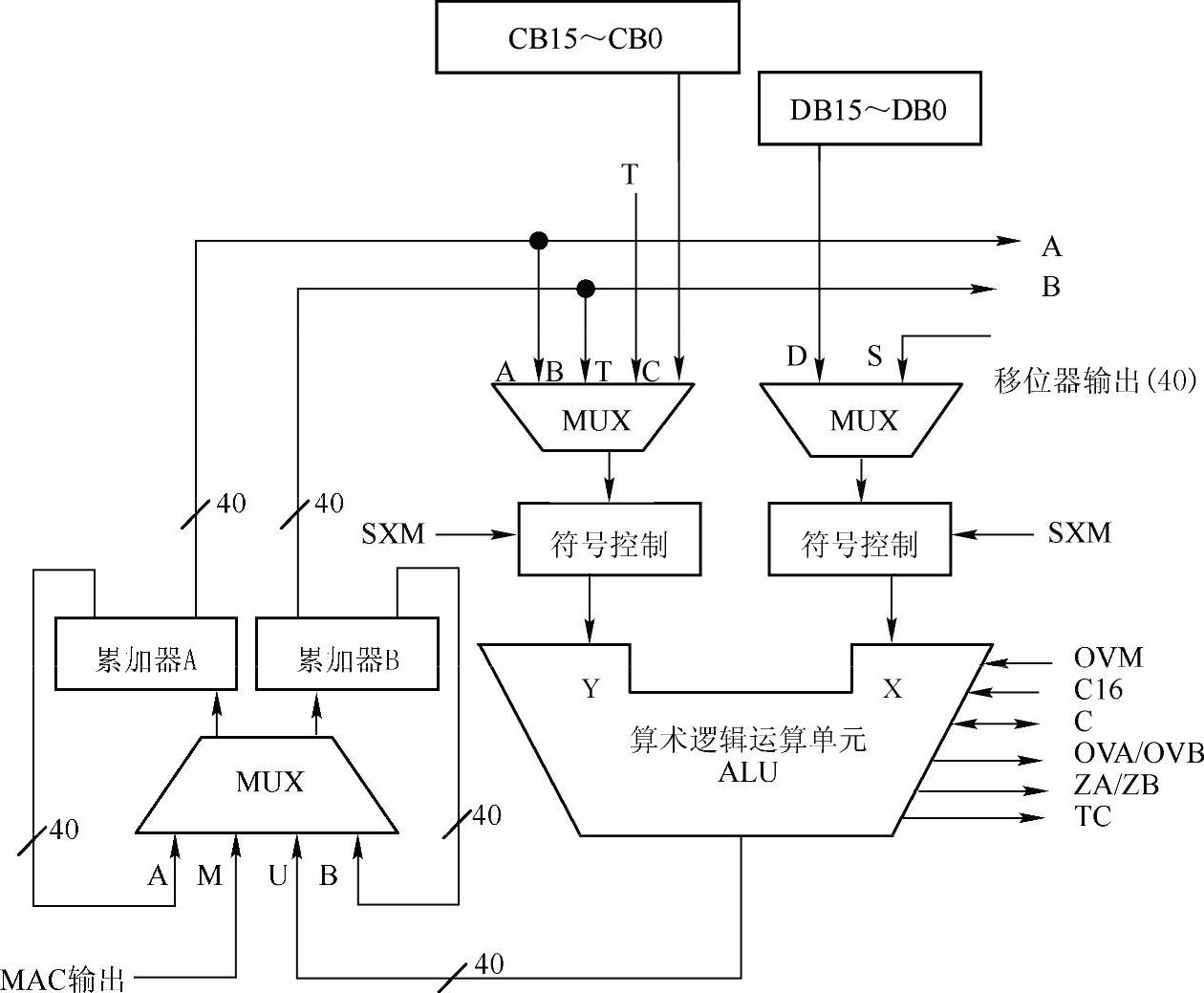

算术逻辑运算单元(ALU)可以实现加/减法运算、逻辑运算等大部分算术和逻辑功能,且大多数的算术逻辑运算指令都是单周期指令。除存储操作指令(ADDM、ANDM、ORM和XORM)外,ALU的运算结果通常都被传送到目的累加器(累加器A和B)。40位ALU功能框图如图3-3所示。

1.ALU的输入和输出

如图3-3所示,ALU有X和Y两个输入端,其中,ALU的X输入端有以下两种数据来源,即:

图3-3 40位ALU功能框图

1)来自移位寄存器的输出(32位或16位数据存储器操作数及累加器中的数值,经移位寄存器移位后输出)。

2)来自数据总线DB的数据存储器操作数。

ALU的Y输入端有以下4种数据来源,即:

1)来自累加器A中的数据。

2)来自累加器B中的数据。

3)来自数据总线CB的数据存储器操作数。

4)来自暂存器T的值。

当一个16位数据存储器操作数通过数据总线DB或CB加到40位ALU的输入端时,40位ALU将按如下两种方式之一对操作数进行预处理:

1)若数据存储器的16位操作数在低16位时,则当状态寄存器ST1中的符号扩展方式控制位SXM=0时,高24位(39~16位)用0填充;当SXM=1时,高24位(39~16位)进行符号位扩展。

2)若数据存储器的16位操作数在高16位时,则当SXM=0时,39~32位和15~0位用0填充;当SXM=1时,39~32位进行符号位扩展,15~0位置0。

ALU的输出为40位,被送往累加器A或B。

2.溢出处理

ALU的饱和逻辑通过将结果保持为一个最大值(或最小值)来防止溢出。这个特性对降低运算误差很有用。当状态寄存器ST1的溢出方式控制位OVM=1时,ALU的饱和逻辑功能就被使能。

当一个运算结果出现溢出时,将按如下方式进行处理:(https://www.xing528.com)

1)如果OVM=0,则将ALU的结果不作任何调整,直接装入累加器中。

2)如果OVM=1,则根据溢出方向,对ALU的结果进行调整。当正向溢出时,将32位最大正数007FFFFFFFh装入累加器;当负向溢出时,将32位最小负数FF80000000h装入累加器。

3)溢出发生后,相应的溢出标志位(OVA或OVB)置1,直到复位或执行溢出条件指令。

注意:用户可以用SAT指令对累加器进行饱和处理,而不必考虑OVM值。

3.进位位(C)

ALU的进位位(C)受大多数ALU指令(包括循环和移位操作)影响,可以用来支持扩展精度的算术运算。进位位不受累加器加载指令、逻辑操作指令、非算术运算和控制类指令的影响,利用两个条件操作数C和NC,可以根据进位位的状态,进行分支转移、调用、返回和条件执行操作。可通过RSBX和SSBX指令对进位位进行置位和复位。在硬件复位时,进位位被置1。

4.双16位算术运算

用户只要置位状态寄存器ST1的双16位/双精度算术运算方式控制位C16,就可以让ALU在单个周期内进行特殊的双16位算术运算,即进行两次16位加法或两次16位减法运算。该模式对于维持加减/比较/选择操作特别有用。

5.其他控制位

除SXM、OVM、C、C16、OVA、OVB外,ALU还有两个控制位。TC为测试/控制标志,位于ST0的12位;ZA/ZB是累加器结果为0标志位。

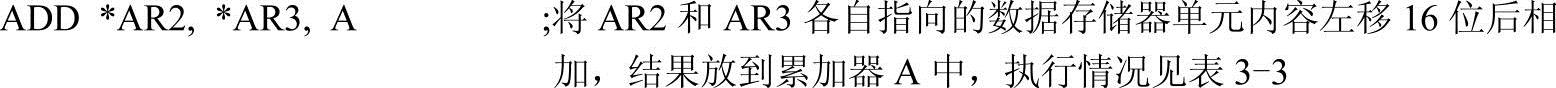

【例3-1】 设(AR2)=0060h,(AR3)=0070h,数据存储器(0060h)=A678h,(0070h)=7234h,分析指令“ADD*AR2,*AR3,A”的执行情况:

(1)在执行指令时ALU中输入端X和Y的情况。

(2)各控制位的变化对执行结果的影响。

(3)指令执行后的结果及标志位的状态。

表3-3 ALU的加法操作举例

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。