从基本功能上看,RAM与第7章中介绍的数码寄存器并无本质区别,只是RAM 的存储容量要比数码寄存器的存储容量大得多,功能远强于数码寄存器。因此,可把RAM看作是由很多数码寄存器组合起来所构成的大规模集成电路。

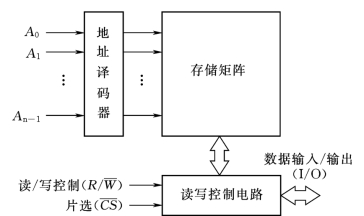

RAM主要包括地址译码器、存储矩阵和读/写控制电路等。图8.2给出了RAM的典型结构示意框图。

1.存储矩阵

存储矩阵是存储器的主体,含有大量存储单元。RAM中的存储单元因排列成矩阵形式而得名存储矩阵。存储矩阵属多字1位结构,1024个字排列而成的矩阵,中间的每个小方块代表一个存储单元,它与外面电路的连接由地址译码器输出信号控制。有10根地址线、1024个地址,每个地址有一个存储单元。RAM 中的一个存储单元只能存储一位二进制数码“1”或 “0”,8位二进制数称为一个字节。存储器中的每一个字节都依次用从0开始的整数进行编号,这些编号称为地址。存储矩阵的容量是由地址码的位数N和字长的位数M 决定的。当一个存储矩阵的地址数为N,每个字长所包含的位数是M时,存储矩阵的容量=N×M。存储矩阵的存储容量越大,存储的信息量就越多,RAM的存储功能就越强。

2.地址译码器

RAM中的每个寄存器都有一个地址,CPU是按地址来存取存储器中的数据。址译码器的作用就是将寄存器地址所对应的二进制数译成有效的行选信号和列选信号,从而选中该存储单元。地址译码器每次读/写信息时,只能和某一个指定地址的寄存器之间进行取出或是存入,此过程称为访问存储器。访问的地址是机器识别的二进制数,送给地址译码器译码后,由相应输出线给出信号,控制被选中的寄存器与存储器的I/O端子,使其进行读/写操作。

3.读/写控制器(https://www.xing528.com)

访问RAM时,对被选中的寄存器,究竟是读还是写,是通过读/写控制线进行控制的。一般RAM的读/写控制线高电平为读,低电平为写;也有的RAM 读/写控制线是分开的,一根为读,另一根为写。当![]() = “1”时,执行读操作,被选中单元存储的数据经数据线、数据输入/输出I/O控制线传送给CPU;当

= “1”时,执行读操作,被选中单元存储的数据经数据线、数据输入/输出I/O控制线传送给CPU;当![]() = “0”时,执行写操作,CPU将数据经过数据输入/输出I/O控制线将数据存入被选中单元。

= “0”时,执行写操作,CPU将数据经过数据输入/输出I/O控制线将数据存入被选中单元。

4.片选控制

图8.2 RAM的结构框图

由于受RAM的集成度限制,一台计算机的存储器系统往往是由许多片RAM组合而成。CPU访问存储器时,一次只能访问RAM中的某一片,即存储器中只有一片RAM中的一个地址接受CPU访问,与其交换信息,而其他片RAM与CPU不发生联系,片选就是用来实现这种控制的。通常一片RAM有一根或几根片选线,当某一片的片选线接入有效电平时,该片被选中,地址译码器的输出信号控制该片某个地址的寄存器与CPU接通;当片选线接入无效电平时,则该片与CPU之间处于断开状态。片选CS为选择芯片的控制输入端,低电平有效。当片选信号 = “1”时,RAM被禁止读写,处于保持状态,I/O接口处的三态门处于高阻状态;

= “1”时,RAM被禁止读写,处于保持状态,I/O接口处的三态门处于高阻状态; = “0”时,RAM 可在读/写控制输入R/W的作用下作读出或写入操作。

= “0”时,RAM 可在读/写控制输入R/W的作用下作读出或写入操作。

5.数据输入/输出控制

为了节省器件引脚的数目,数据的输入和输出共用相同的引脚 (I/O),因此数据输入/输出控制也简称为I/O控制。“读”操作时,I/O端子作输出端;“写”操作时,I/O端子作输入端,可一线二用。RAM 通过I/O端子与计算机的CPU交换数据,I/O端子数据线的条数与一个地址中所对应的寄存器的位数相同。例如,在1024×1位的RAM中,每个地址中只有1个存储单元(1位寄存器),因此只有1条I/O引线;而在256×4位的RAM中,每个地址中有4个存储单元 (4位寄存器),所以有4条I/O引线。有的RAM输入线和输出线采用分开的。RAM 的输出端一般都具有集电极开路或三态输出结构。由读/写控制线控制。通常RAM 中寄存器有五种输入信号和一种输出信号:地址输入信号、读/写控制输入信号 、输入控制信号

、输入控制信号 、片选控制输入信号

、片选控制输入信号 、数据输入信号和数据输出信号。

、数据输入信号和数据输出信号。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。