当时序逻辑电路的触发器位数为n,电路状态按二进制数的自然态序循环,经历的独立状态为2n个,这时,我们称此类电路为二进制计数器。

二进制计数器除按同步、异步分类外,还可按计数的增减规律分为加计数器、减计数器和可逆计数器。

1.异步二进制计数器

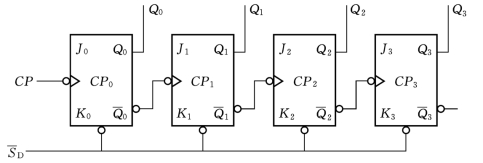

二进制计数器中各位触发器所用的计数脉冲不同,通常时钟脉冲加到最低位触发器的CP端,其他触发器的CP端分别由低位触发器的Q 端或 端控制。图7.6所示就是一个由主从型JK触发器构成的异步二进制计数器。

端控制。图7.6所示就是一个由主从型JK触发器构成的异步二进制计数器。

图7.6 由主从JK触发器构成的异步二进制计数器

在图7.5所示电路中,每一个JK触发器都接成一位计数器,只有最低位触发器的CP端与时钟脉冲相连,其余触发器的CP端均与相邻低位触发器的输出端Q 相连,即低位输出端Q为相邻高位触发器的时钟脉冲信号。该电路不存在组合逻辑电路,因此是莫尔型异步时序逻辑电路。其时钟方程分别为

![]()

驱动方程为

![]()

次态方程为

计数前各位触发器清零,使图7.5所示二进制计数器初始状态为 “0000”。当第1个CP时钟脉冲下降沿到来时,计数器开始工作,根据上述方程式可写出其逻辑状态转换真值表,见表7.3。

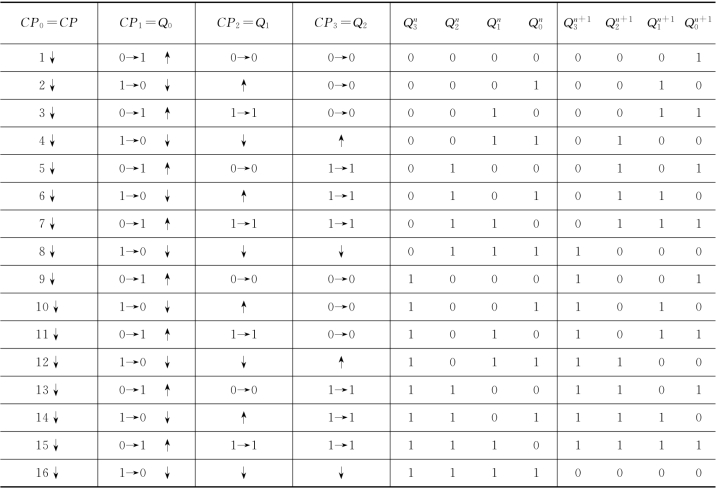

表7.3 由JK触发器构成的异步二进制计数器状态转换真值表

由表7.3可看出,该异步二进制计数器是一个模16的四位二进制加计数器。(https://www.xing528.com)

如果把电路作一改动:图7.6中除最低位外,其余各位触发器的CP端由原来与相邻低位的Q 端相连改为与相邻低位的 端相连,把直接置0端改为直接置1端,就构成了如图7.7所示的异步二进制减法计数器。

端相连,把直接置0端改为直接置1端,就构成了如图7.7所示的异步二进制减法计数器。

图7.7 由主从JK解发器构成的异步二进制减计数器

图示电路的时钟方程分别为

![]()

驱动方程为

![]()

次态方程为

计数前各位触发器置 “1”,使图7.7所示二进制计数器初始状态为 “1111”。当第1个CP时钟脉冲下降沿到来时,计数器开始工作,根据上述方程式可写出其逻辑状态转换真值表,见表7.4。

表7.4 由JK触发器构成的异步二进制减计数器状态转换真值表

由表7.4可看出,该异步二进制计数器是一个模16的四位二进制减计数器。显然,只要把主从型JK触发器的输入J和K 悬空为 “1”或都接高电平,每一位触发器都可构成一位计数器。如果把Q作为相邻高位触发器的时钟脉冲信号,就可构成多位二进制加计数器,如果把 作为相邻高位触发器的时钟脉冲信号,则可构成多位二进制减计数器。

作为相邻高位触发器的时钟脉冲信号,则可构成多位二进制减计数器。

同理,如果把D触发器的输出Q端作为相邻高位触发器的时钟信号,即可构成减计数器;若把 端作为相邻高位触发器的时钟信号,又可构成加计数器。读者可自行分析。

端作为相邻高位触发器的时钟信号,又可构成加计数器。读者可自行分析。

2.同步二进制计数器

同步二进制计数器是把计数脉冲同时加到所有触发器的时钟脉冲CP端,通过控制电路控制各触发器的状态变换,如 [例7.2]所示时序逻辑电路就是一个典型的同步二进制减计数器。同步计数器通常都包含有组合逻辑电路,因此分析起来比异步时序逻辑电路复杂。但是,同步计数器的速度要比异步计数器快得多。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。