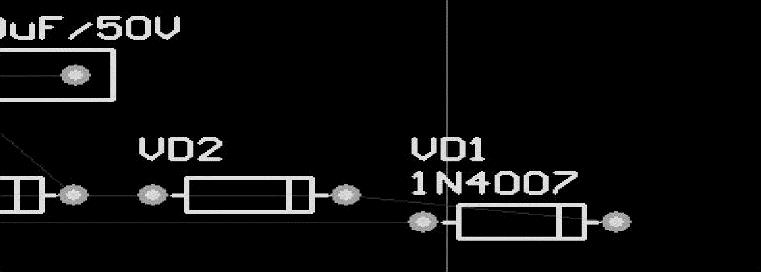

导入网络表的操作是将已有的原理图转换到一张空白的PCB上,可是如果在PCB已经布局,甚至已经布好线的情况下才发现电路设计有错误或不妥之处,这时需要对原理图进行修改。那么修改之后还需要重新载入网络表、重新编辑PCB吗?其实不必,Protel 99 SE提供了原理图和PCB的同步更新功能。对原理图修改之后,利用同步器更新PCB,原理图的相应修改会自动反映到PCB上,且PCB已有的设计成果不会遭到破坏。这里我们先将某个元器件的参数修改一下,然后观察更新PCB后的效果,比如在原理图里将二极管VD1的封装修改为“AXIAL0.3”,PCB更新前的VD1如图2-54所示。更新PCB的操作步骤如下:

图2-54 PCB更新前的VD1

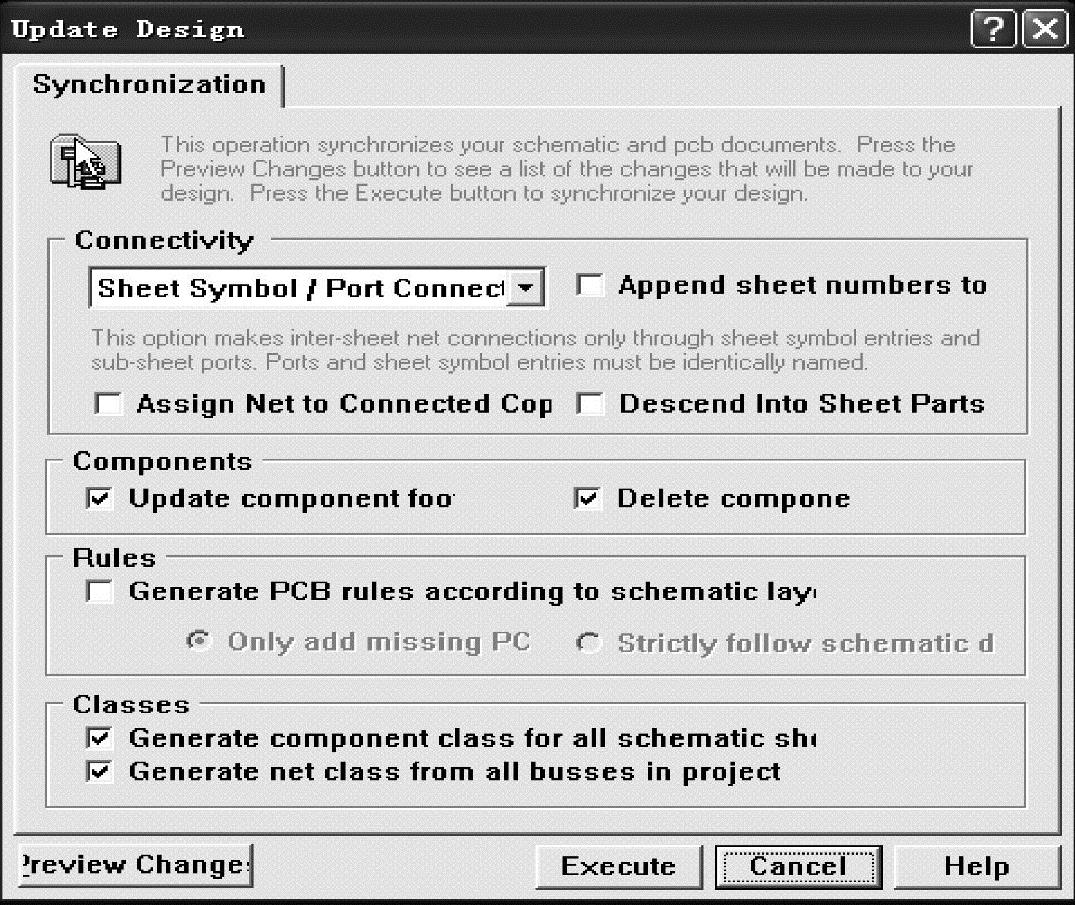

1)在原理图工作环境下,执行菜单命令“Design”→“UpdatePCB”(更新PCB),即可弹出如图2-55所示的对话框,选择所要更新的PCB文件(只有在一个数据库中有多个PCB文件时,才会出现这步),然后单击“Apply”按钮,打开如图2-56所示的“Update Design”(同步器参数设置)对话框。其中各选项的含义如下:

图2-55 选择所要更新的PCB文件

①Connectivity:原理图内部网络连线方式。

②Append sheet numbers to local net name:在网络名称上附加原理图编号。

③Assign Net to Connected Copper:在连接的敷铜区设置网络。

④Update component footprint:更新元器件封装形式。如选中该选项,则系统在遇到不同的元器件封装形式时将自动更新。

⑤Delete componen tif not in netlist:删除网络表上没有的元器件。

⑥Generate PCB rules according to schematic layout:根据原理图设计生成PCB设计规则。选中该选项后,有两种可选方式:“Only add missing PCB”(仅加入原PCB中没有的规则)方式和“Strictly follow schematic directive”(严格遵循原理图信息)方式。

⑦Generate component class for all schematic sheet:生成所有原理图元器件的类型。(https://www.xing528.com)

⑧Generate net class from all bus sesinproject:由设计方案中的所有总线生成网络类型。

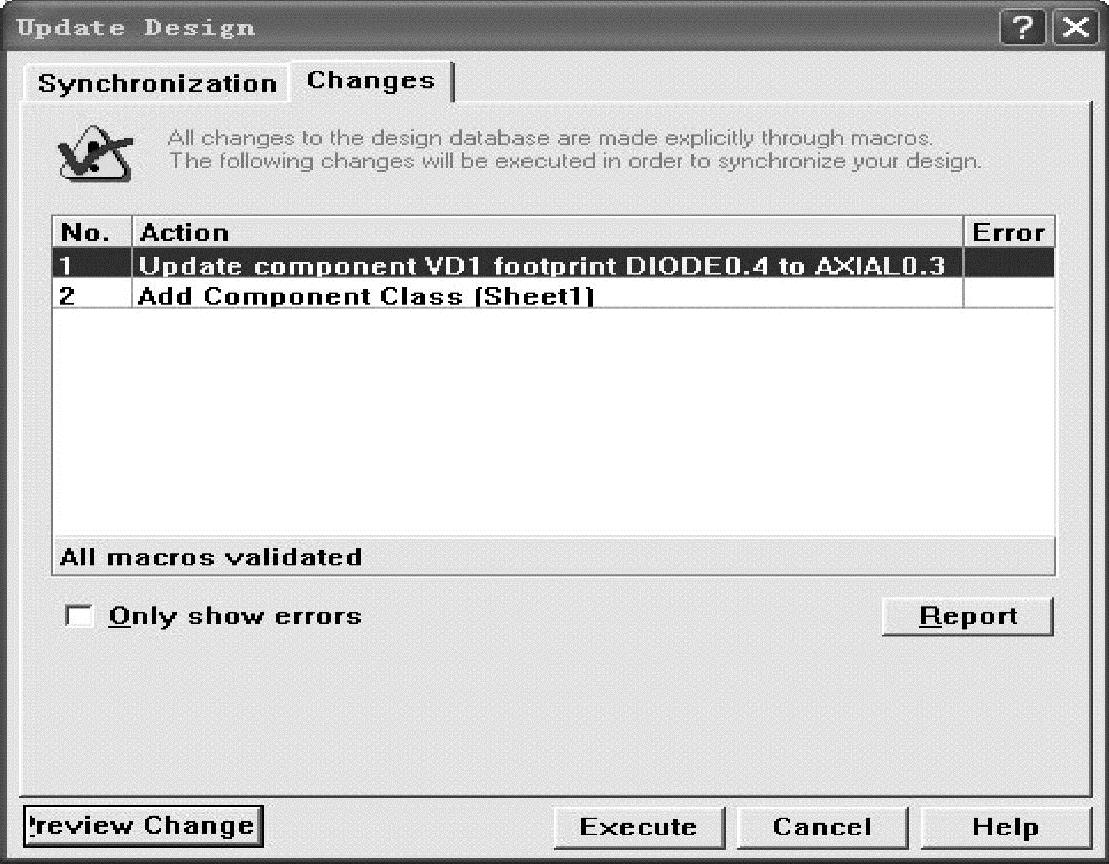

2)设置完同步器的参数后,单击图2-56中的“Preview Changes”按钮,同步器将开始扫描所选的PCB文件信息和原理图信息,之后给出PCB更新前后的对比信息。

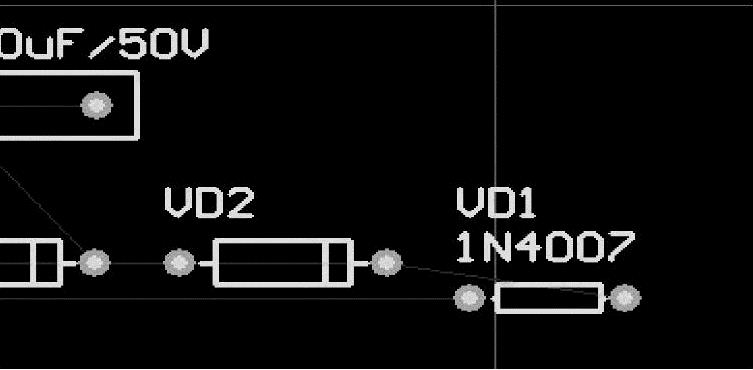

如果这时存在错误,则需要修改正确,才能进行下一步,否则将会导致PCB的不正确。如图2-57所示,从框出来的内容可以看到二极管VD1在PCB更新前后的封装信息的变化,“Reference components”列出的是即将更新的元器件信息,其中VD1的封装是“AXIAL0.3”,而“Targe tcomponents”列出的是更新前的元器件信息,其中VD1的封装是“DIODE0.4”。如何没有存在错误信息,那么单击“Apply”按钮,同步器即开始更新PCB文件,弹出如图2-58所示的对话框,该对话框列出了更新的信息,其中“Update Component VD1 footprint DIODE0.4toAXIAL0.3”明确说明了此次更新的内容是将元器件VD1的封装从DIODE0.4更新为AXIAL0.3。单击“Execute”按钮,更新完PCB后的VD1如图2-59所示。对于新建的PCB文件来说,这个更新过程即是将原理图的信息装入PCB文件的过程。

图2-56 “Update Design”(同步器参数设置)对话框

图2-57 PCB更新元器件匹配信息

图2-58 PCB更新对话框

图2-59 PCB更新后的VD1

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。