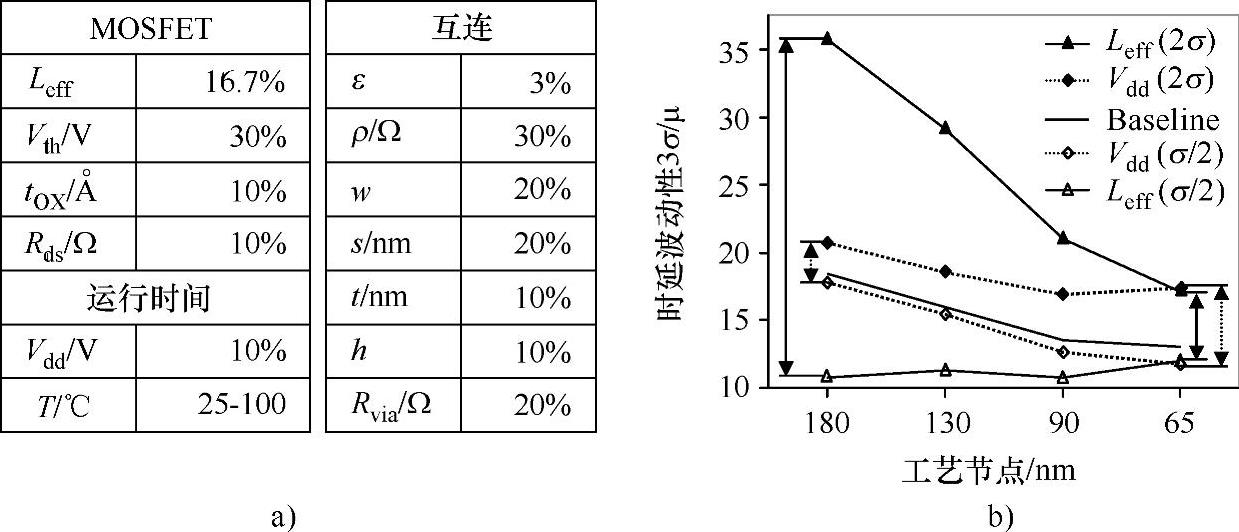

电路参数的波动涉及硅工艺(如有效沟道长度Leff、阈值电压Vth、金属宽度)或电路工作参数(如信号串扰、电源噪声和温度)与设计标称值的偏离。这些偏离来自芯片制造或运行阶段的电路工作。假定这些偏离服从正态分布,图11-1a总结了130nm技术节点主要波动源的相对偏差(3σ/均值(μ))。这些数据引自2002国际半导体技术路线图(ITRS)[1]以及一些从科研预测中得到的数据[4-6]。根据ITRS,在90nm或者更小的工艺中会有相似的或者更严重的波动,而工业界预测计的偏差还要大[7]。在这些波动源中,电路时延波动对Leff、Vth、金属尺寸、信号耦合、Vdd噪声和温度等最敏感[6]。在当前的工艺中,其他一些参数可能对性能的影响很小(如寄生的源漏电阻Rds)或它们甚至可以从先进的波动性控制中受益(如介质常数),因此,在变化分析中可以忽略它们的影响。而且,即使是一阶变化,对波动性的影响也会随着工艺的缩小而改变。例如,图11-1b所示为Leff和Vdd控制(即将参数变化减小到σ/2或使它放宽到2σ)对规范的关键路径结构性能的影响[6]。关键路径结构是基于ITRS,并且这些预测是通过使用BPTM器件和互连模型经过SPICE仿真获得的[4,5]。由于速度饱和,Leff对更短沟道的晶体管的影响很小,而Vdd的重要性随着沟道长度的减小而增加[6]。

注意,在前几代工艺中,电路性能的波动性中,晶体管和栅级的波动占主导地位,但是最近的工艺尺寸缩小已经导致片上互连参数产生了更大的波动,包括互连尺寸、电阻率(ρ)、介电常数(ε)和通孔电阻(Rvia)[8]。这些互连波动与晶体管的波动无关,并且不同层次互连之间也基本相互无关,导致基于工艺角模型对所有波动性的分析变得极其复杂。

图11-1 电路参数的波动情况及其对时延分散性的影响

a)130nm技术节点主要波动源的3σ/μ比值 b)Leff和Vdd对时延的影响

参数波动具有空间分布的特性,因此通常采用芯片内(即intradie)或芯片间(即interdie)来表征。芯片间的波动是指在同一个芯片内波动相同,因此对同一个芯片内的每个元件具有同样的影响,而在整个晶圆范围呈现随机分布。这种波动决定了芯片上每个参数的标称值,并且使得这些标称值在晶圆上各芯片之间以及在不同晶圆之间互不相同。目前的工艺中,特征尺寸总的波动中,芯片间的波动大约占特征尺寸总波动的50%[9]。芯片间的波动基本与设计无关,而与设备的特性、晶圆的放置、工艺温度等因素有关[9]。(https://www.xing528.com)

芯片内的波动表现在沿着芯片长度方向参数的波动。在以前的工艺中,它的影响可以忽略,但是在纳米时代,它达到与芯片间的波动可比拟的程度,并且在某些情况下甚至远大于芯片间的波动[7]。对关键路径时延的波动性来说,芯片内的波动直接影响着时延均值,而芯片间的波动决定了时延分散性的方差[9]。芯片内的波动可以进一步分为两部分:系统的和随机的。系统波动可以在制造前进行预测,例如版图对沟道长度分散性的影响。成功的工艺缩小依赖于工艺和设计阶段对系统波动因素的有效补偿。相反,随机波动是由于半导体工艺本身的不可预测性引起的。随机波动的例子包括沟道掺杂、栅氧厚度和介电常数等的波动。运行阶段的一些参数波动,如Vdd噪声,也被认为是随机波动,由于精确预测它们的影响极端困难,因为我们不能对随机现象进行补偿,这种波动可能最终对具有满意成品率的纳米CMOS电路设计提出巨大的挑战。

对给定的工作温度,Leff、Vth和Vdd的随机波动是逻辑门中参数分散性的最主要来源。Leff和Vdd的波动彼此相对独立,而Vth值同时与Leff、Vdd值以及晶体管尺寸有很强的关系。这是因为短沟MOSFET的Vth标称值直接受DIBL效应的影响,而DIBL效应是Leff和Vdd的函数,描述Vth分散性程度的参数σVth则依赖于晶体管尺寸,并且主要受到沟道掺杂波动的影响。下式表示的Vth分散性和晶体管尺寸之间的关系适用于纳米时代[10,11](同时请参考11.3节):

为了针对波动性进行正确的设计和优化,必须考虑这些关系;在电路级,可以利用它们之间的关系,通过调整Vdd、Vth和晶体管尺寸,获得性能、功耗和分散性之间的折衷[11]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。