【摘要】:这种毛细力将光致抗蚀剂的侧墙拉到一起,特别是当一个槽被表面活化物质完全填满而邻近的槽为部分填满时。这种对侧墙作用力的差异引起了光致抗蚀剂侧墙的崩塌。如果布线器能根据空间情况将互连之间的间距扩展开,将减小引起短路和开路的外部微观材料对成品率的影响,也能减少光致抗蚀剂分解产生的缺陷对成品率的影响。

在第11章中,我们将研究采用在制造中易于实现的构造时钟布线技术来减少波动以及实施修正。本节我们将介绍能改善其他全局布线特性的技术以及它们对成品率的影响。

即使不使用低k介质,铜互连工艺仍然是纳米CMOS芯片制造中的主要难点。首要的也是最重要的是芯片上的互连密度。理想的方法是布线器能在整个芯片上实现均匀的互连密度。实际工作中,布线器仍然不具备这种能力。目前已出现了一些工具有助于实现这样的密度要求。虽然尚不完美,至少正在向均匀性目标这一正确方向前进。结合金属填充和开槽等工作,可以实现金属密度的高度一致。

由最窄互连组成的较长平行走线是导致成品率损失的另一种机制。这种成品率损失的原因是由于漂洗期间光致抗蚀剂侧墙上的毛细现象导致光致抗蚀剂的分解。这种毛细力将光致抗蚀剂的侧墙拉到一起,特别是当一个槽被表面活化物质完全填满而邻近的槽为部分填满时。这种对侧墙作用力的差异引起了光致抗蚀剂侧墙的崩塌。

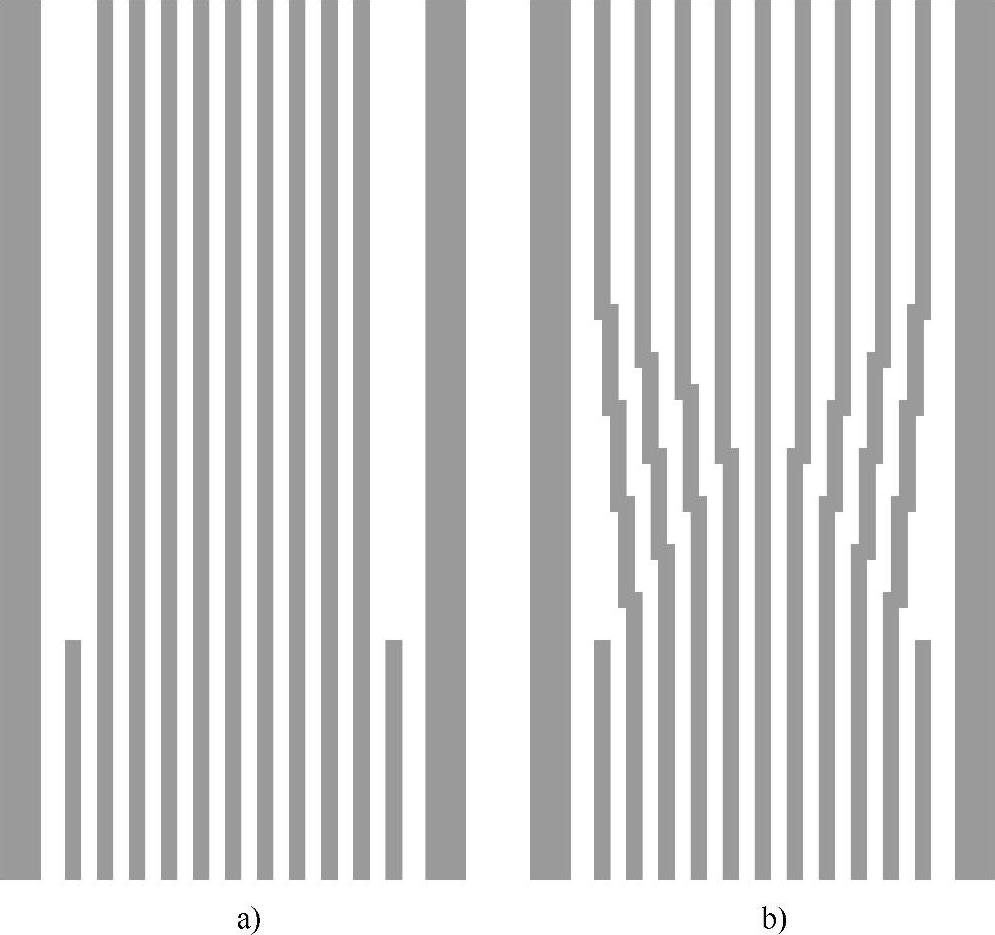

如果布线器能根据空间情况将互连之间的间距扩展开,将减小引起短路和开路的外部微观材料对成品率的影响,也能减少光致抗蚀剂分解产生的缺陷对成品率的影响。即使是几微米的互连扩展也能对成品率产生重要的影响。扩展互连的另一个优点是能改善性能和信号完整性。图10-11是互连扩展布线的一个实例。(https://www.xing528.com)

图10-11 a)传统的布线 b)互连扩展布线

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。