下面的案例研究分别说明好的和差的版图实践。在第11章中我们将探究版图对器件参数分散性的影响以及如何避免这些问题。

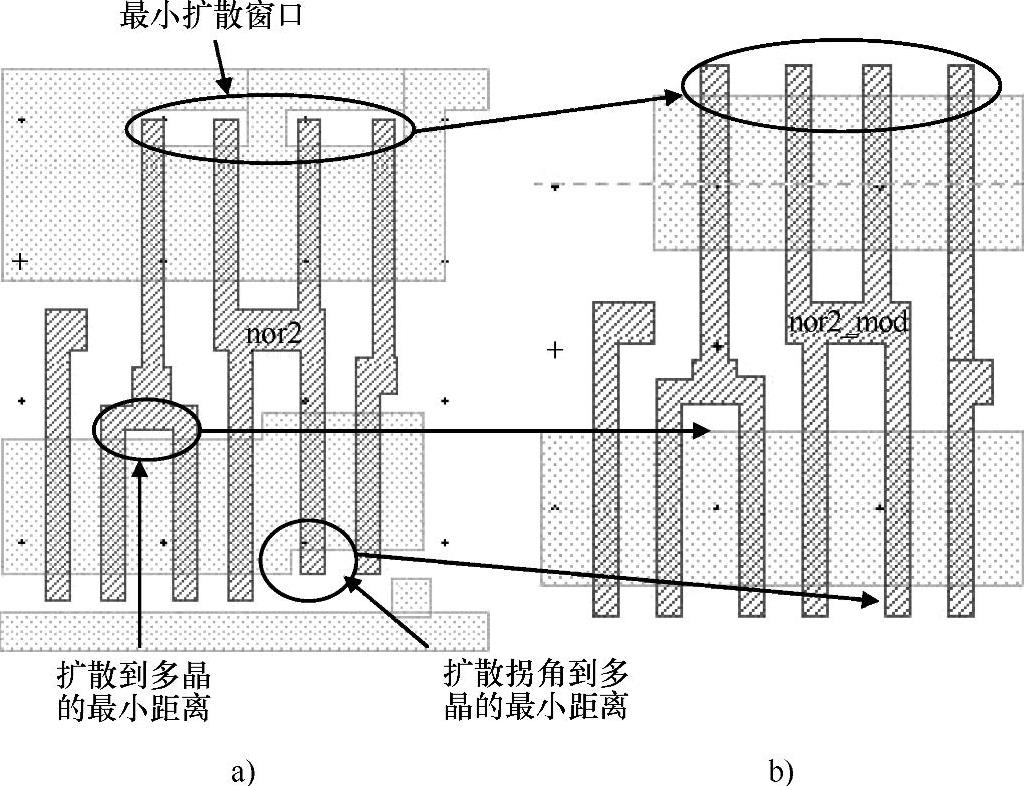

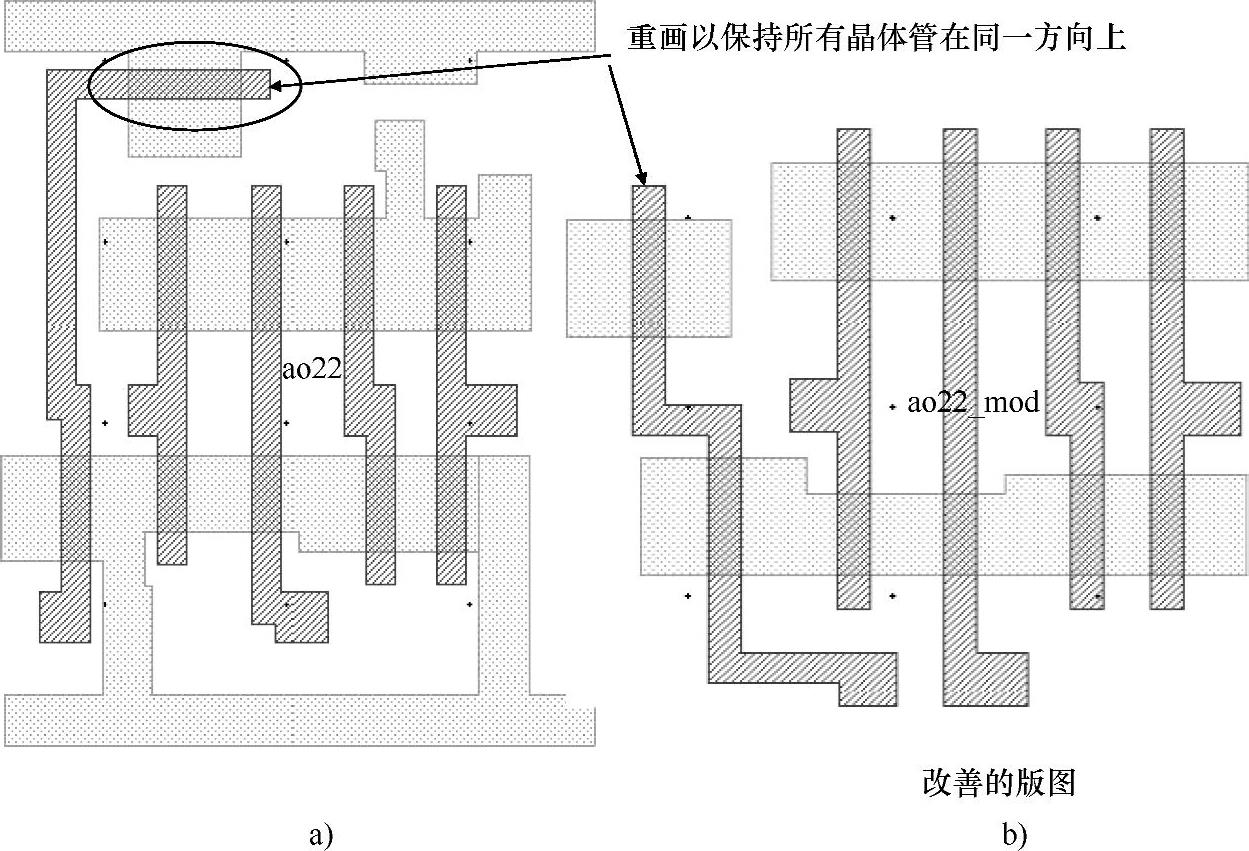

图10-1a所示为是一个库中门电路的两种不同版图。位于版图中的不同的区域使这个门变得不可缩小并且增加了它对工艺变化和晶体管末端泄漏的敏感性。最小扩散窗口的工艺变形导致端帽覆盖的损失。这又将导致严重的晶体管泄漏。

图10-1 a)一个库中的门电路的版图 b)改进的版图

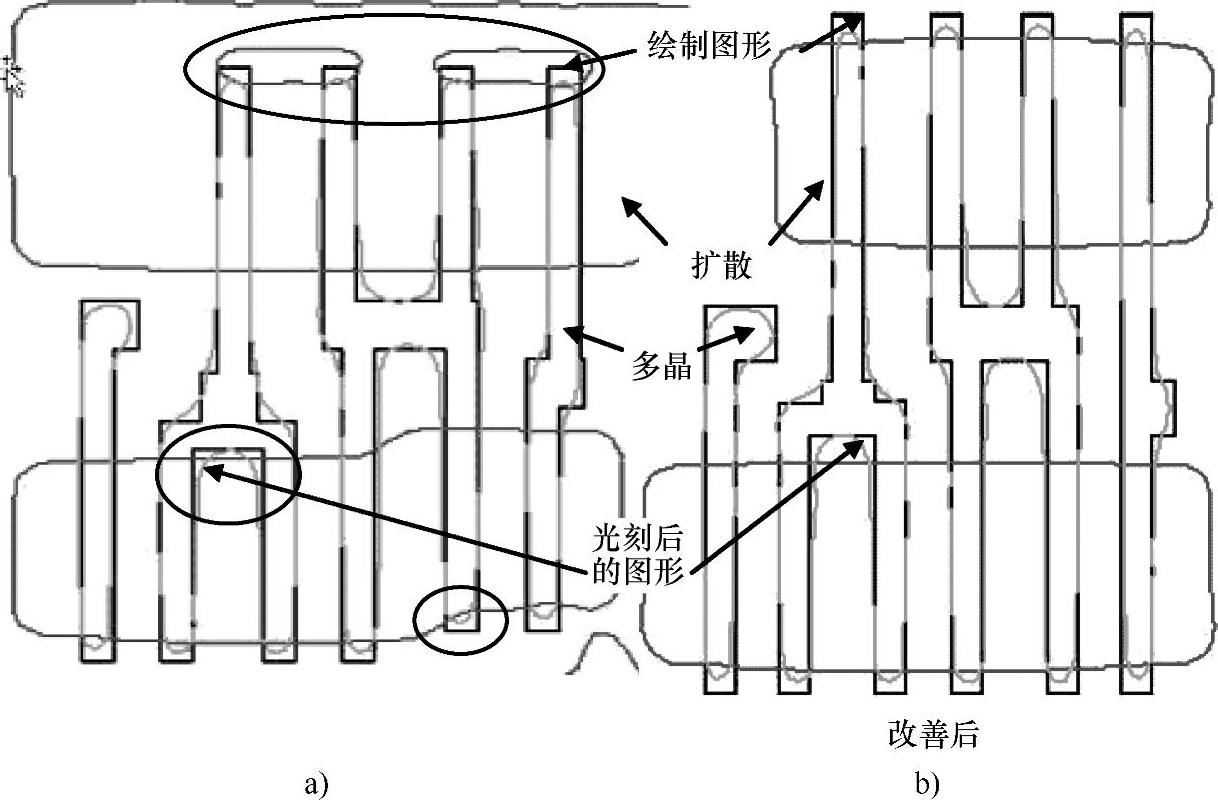

与反U型多晶硅之间的最小扩散间距导致了晶体管平均长度更长,并且因此使驱动电流更小。在理想对准情况下,扩散拐角到多晶硅的最小间距刚刚能使端帽覆盖,但是如果不能完美对准,出现偏移,即使这种情况下扩散拐角是小的急弯,也不能保证端帽覆盖。如果这个急弯的内拐角较长,情况将更加严重。这个单元是为130nm节点设计的。缩小到90nm时,光刻的单元最终虚像如图10-2所示。同一单元的改进版图如图10-1b所示,其中对原来单元中所有很差的且会引起失效的区域进行了改进。

图10-2 a)图10-1中单元的光刻最终虚像 b)改进版图的效果

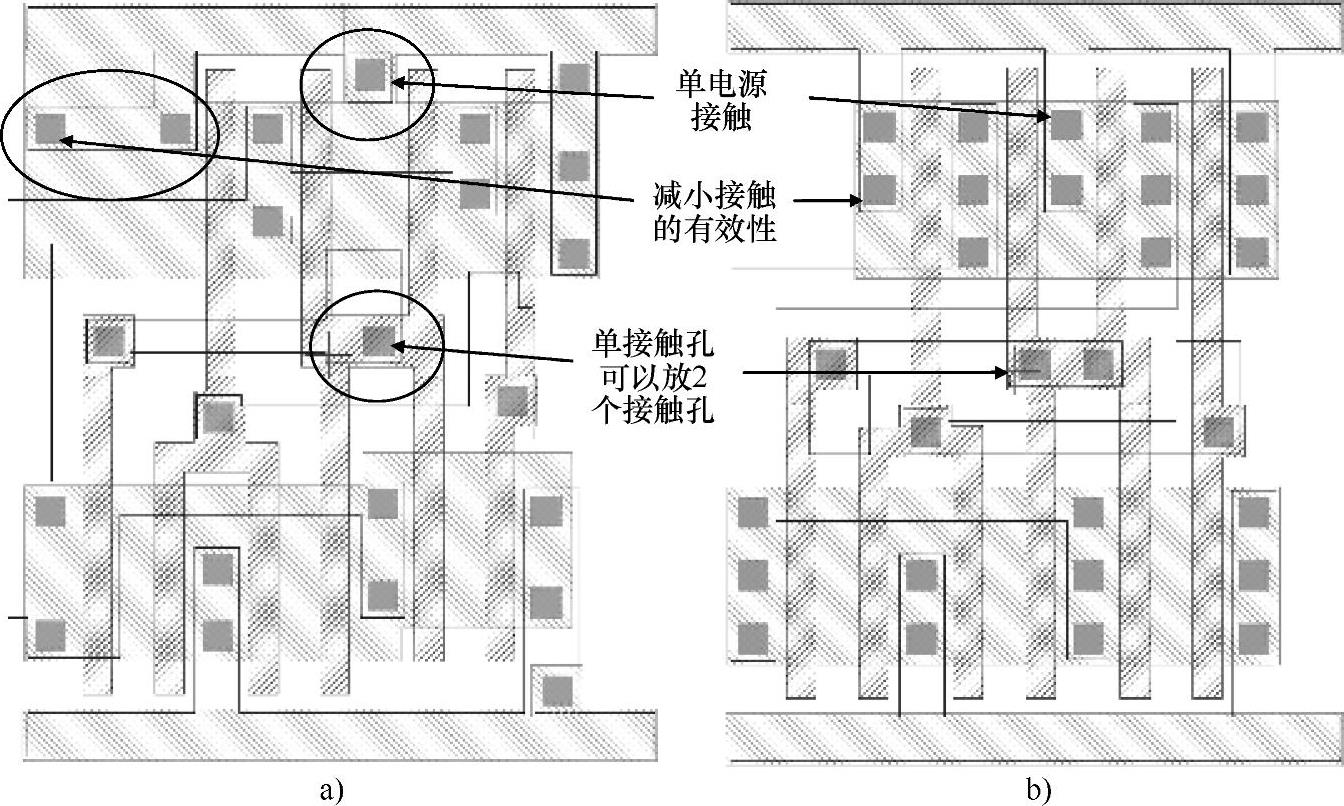

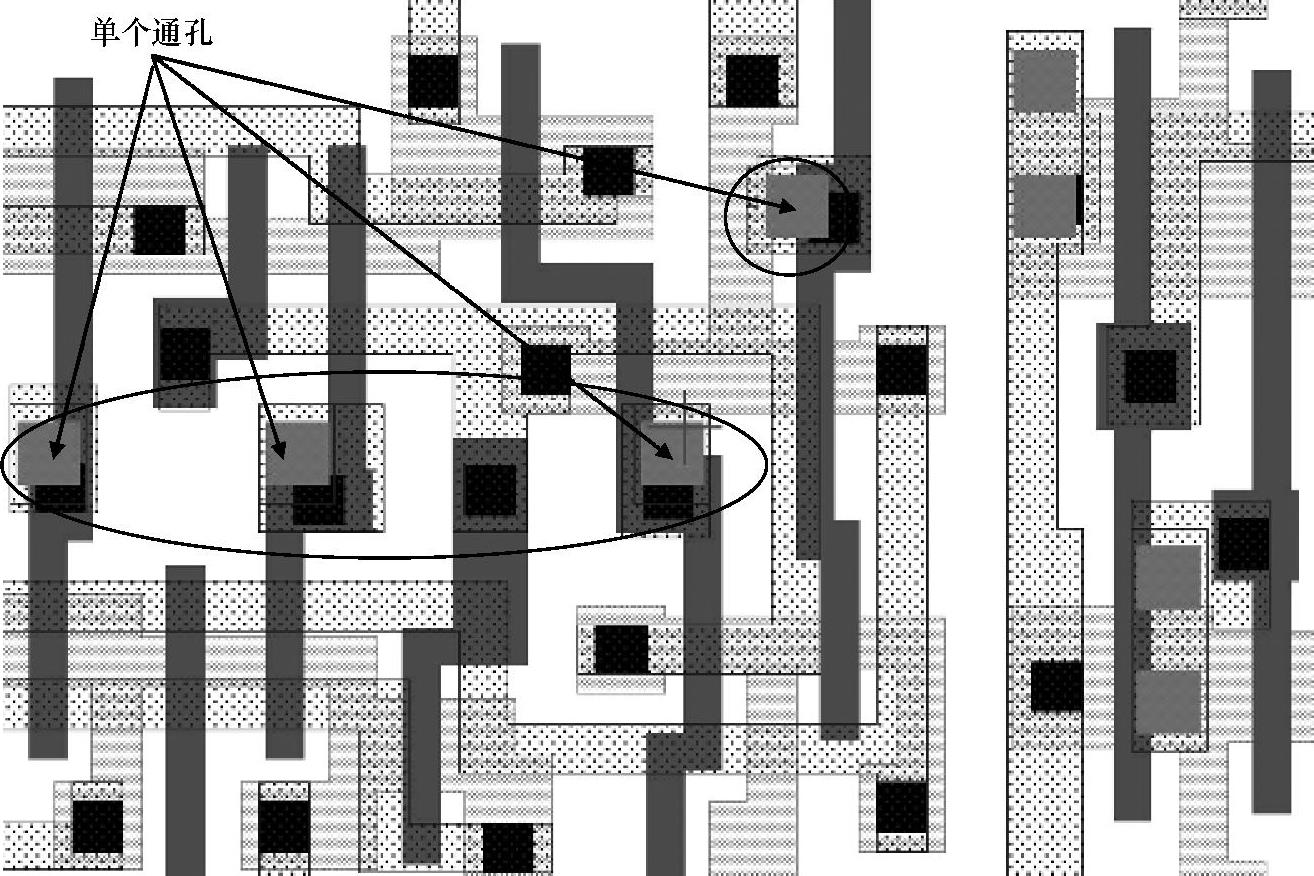

接触孔和通孔开口是另一种影响成品率的因素。因此应该谨慎使用两个中间有间距的接触孔。图10-3显示的是一个版图实例以及改进方法。图10-4是使用单个通孔的单元;重画了金属1与通孔相连的接触区,使其大于通孔面积,将能够改善产品的成品率。

图10-3 a)采用两个接触孔的版图 b)改进的版图

对纳米CMOS技术,如果设计中所有晶体管都朝一个方向的话,控制poly-CD应该更容易。如果需要偏置来修正光学和刻蚀变形,只要使晶体管多晶同向排列,在设计中就能够比较容易地实现上述修正要求。这点对模拟电路、存储器位单元、读出放大器和其他关键电路来说特别重要。图10-5a是晶体管垂直排向和水平排向的版图。图10-5b是将所有晶体管同一排向的版图。这个版图还包括了前面我们讨论的其他改善。

图10-4 采用单个通孔的版图

图10-5 a)包括垂直和水平方向晶体管的版图 b)改进的版图

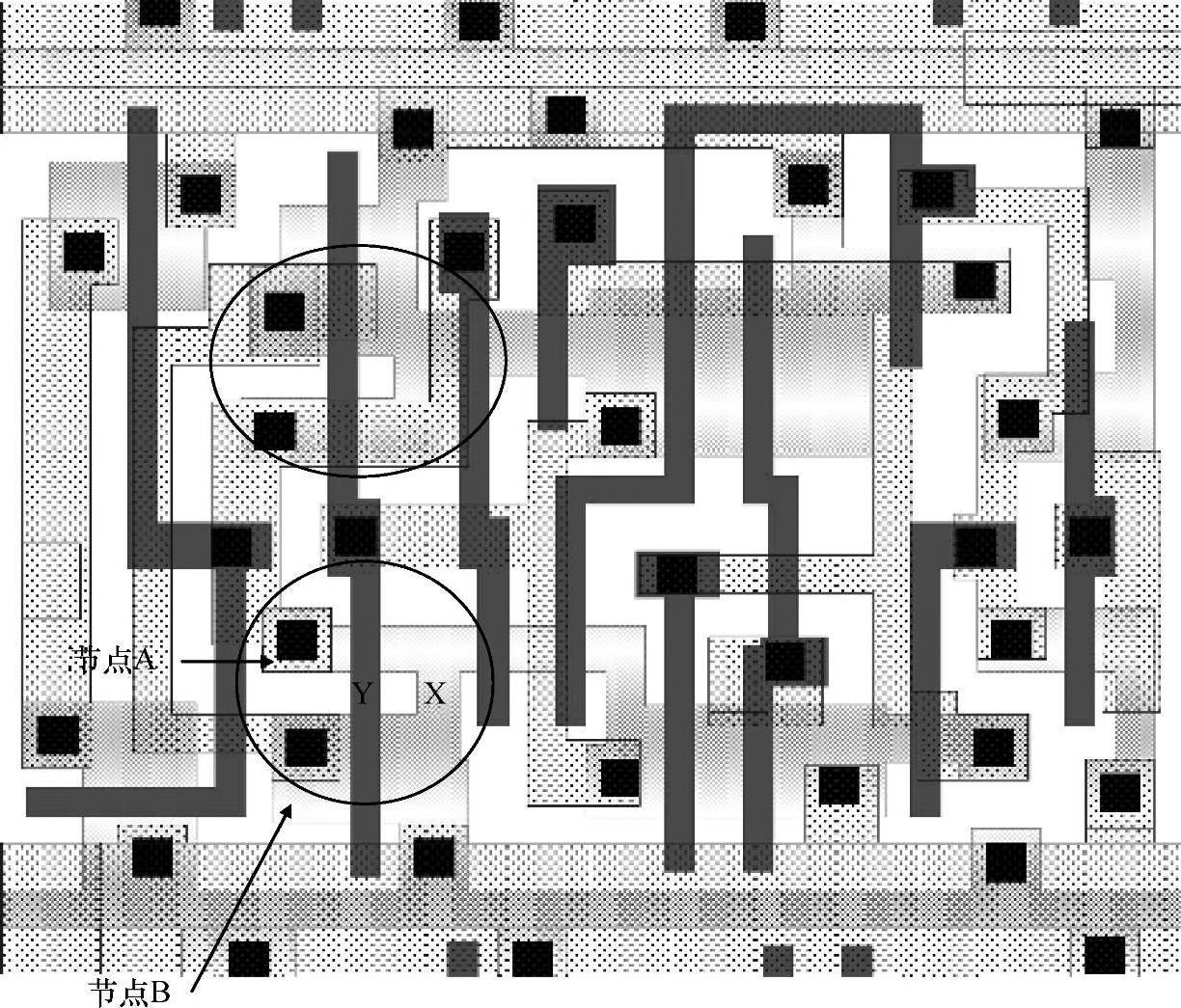

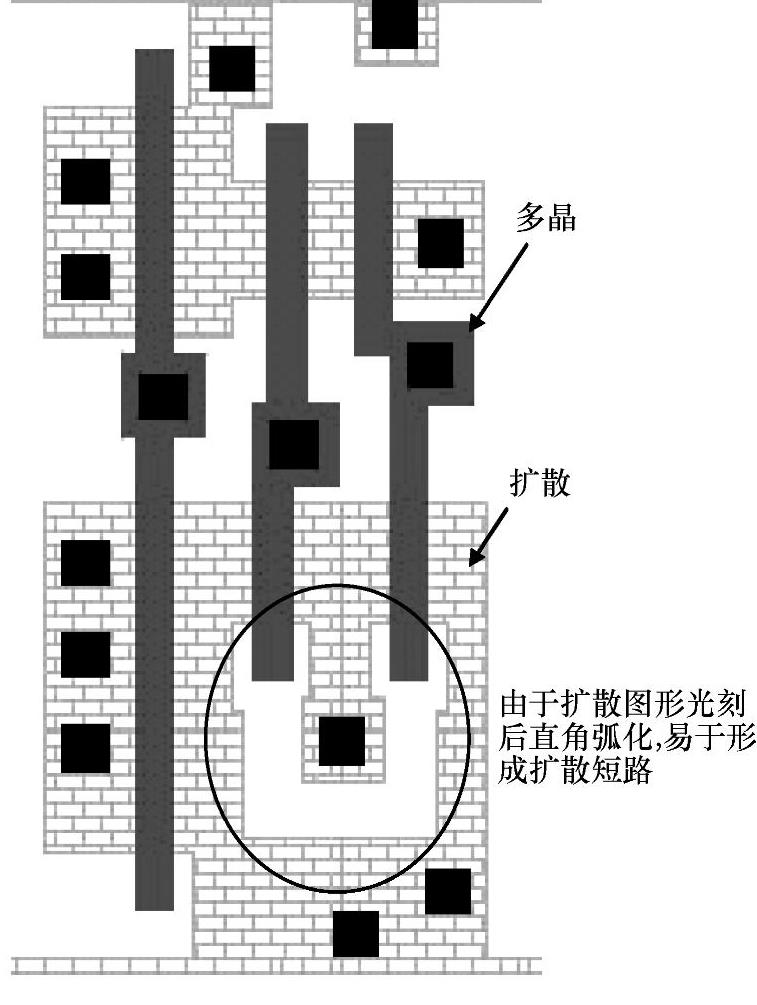

图10-6所示为由于未对准和扩散图形光刻后直角弧化导致短路的版图。图中节点X处是扩散图形光刻后直角弧化,如果存在未对准情况使得多晶Y与节点X处的扩散交迭,就会引起节点A和节点B短路。这个版图上有两个地方会发生这种情况,如图10-6中圆圈所示的范围。(https://www.xing528.com)

图10-6 导致短路的版图

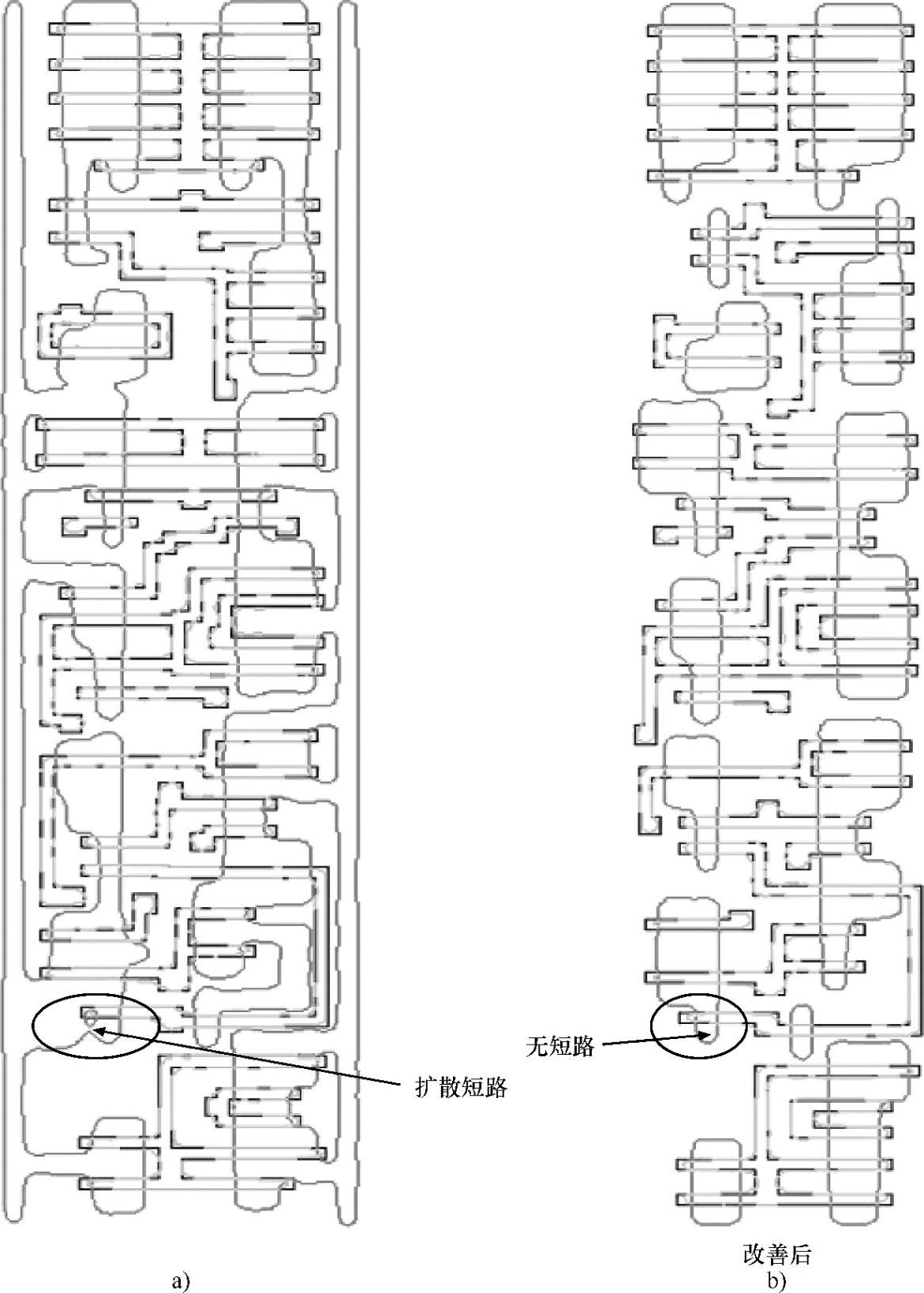

图10-7a所示为一个设计得很差的触发器的光刻仿真虚像。这个触发器的版图如图10-8所示。图10-8中所示的采用最小扩散间距的C型扩散会因为扩散图形光刻后直角弧化而发生扩散短路。这个短路在图10-7a所示的虚像中非常明显。改进后没有C型扩散区的版图则不会引起短路(见图10-7b)。

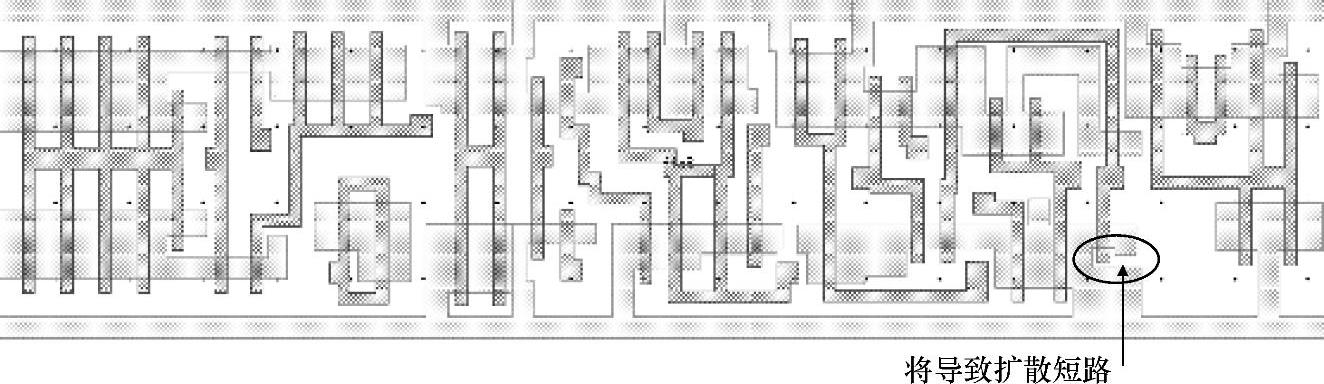

图10-9所示为另一种对光刻工程师来说具有挑战性的版图。最小的U型扩散槽不仅很难被光刻出来,而且也很难被缩小到下一个工艺节点中。由于扩散图形光刻后直角弧化,像触发器例子中的C型扩散区那样(见图10-8),它也易于形成短路。

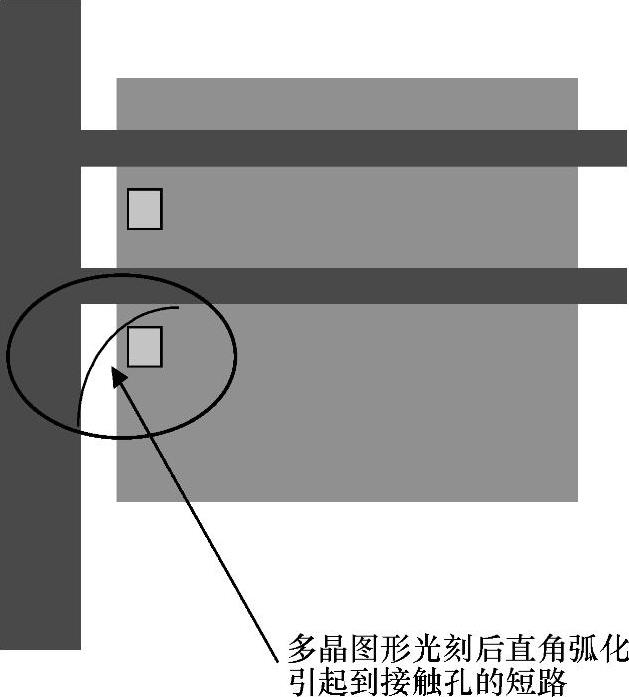

图10-10所示为一个接触孔太靠近扩散区边界的情况,这里扩散与T型多晶之间采用的是最小间距。多晶图形光刻后直角弧化加之未对准就会导致多晶与接触孔短路。这些问题的解决方法是增大多晶到扩散边界的间距,从而多晶图形光刻后直角弧化不会扩展到扩散上。

图10-7 a)一个设计得很差的触发器的光刻仿真虚像 b)改进的版图

图10-8 图10-7中触发器版图

图10-9 形状较差的扩散槽

图10-10 接触太靠近扩散边界的版图

在纳米CMOS技术中,即使对版图——光学相互影响方面经验非常丰富的设计者而言,光学仿真也是必需的。这将有助于关键层的版图设计以及接触孔、多晶、扩散和通孔的合适布局。

在一些敏感的情况下,甚至接触孔和通孔的金属化覆盖都会成为问题,因为金属最小宽度和间距变得更小了,因此在90nm节点中要求采用OPC和相移掩膜版(PSM)技术。基本原则是保持多边图形简单,不要采用复杂的急弯,并且在不增大单元面积的情况下使多晶转弯尽可能远离扩散边界。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。