1.运行阶段的低功耗SRAM

(1)通过SSI抑制外围电路泄漏。存储器外围电路是由多个相同的电路模块组成的,在待机期间,由于总沟道宽度很大,这些模块将成为多条很严重的泄漏路径。即使在动态工作模式下,除了一小部分被选的模块,这些电路中的其他大部分都处于非激活态。这些特点使采用简单而有效的亚阈区电流控制成为可能。许多降低逻辑电路泄漏电流的技术,如栅——源背偏、衬底——源背偏、多Vth和功率开关技术都已在存储器外围电路泄漏抑制中得到了广泛使用[91]。作为这些技术应用的一个实例,图9-15所示为源极开关阻抗(Switched-Source Imped-ance,SSI)方案[77],它关断了空闲期间的控制电路泄漏路径。图9-13b中采用电平固定的输入缓冲器将内部节点驱动到预定的电平。图中的MC、MS和标为阴影的反相器都是高Vth开关。

图9-15 SSI方案和它在存储器中的应用

a)SSI电路结构 b)应用到存储器外围电路泄漏抑制中的SSI(来源于参考文献[77])

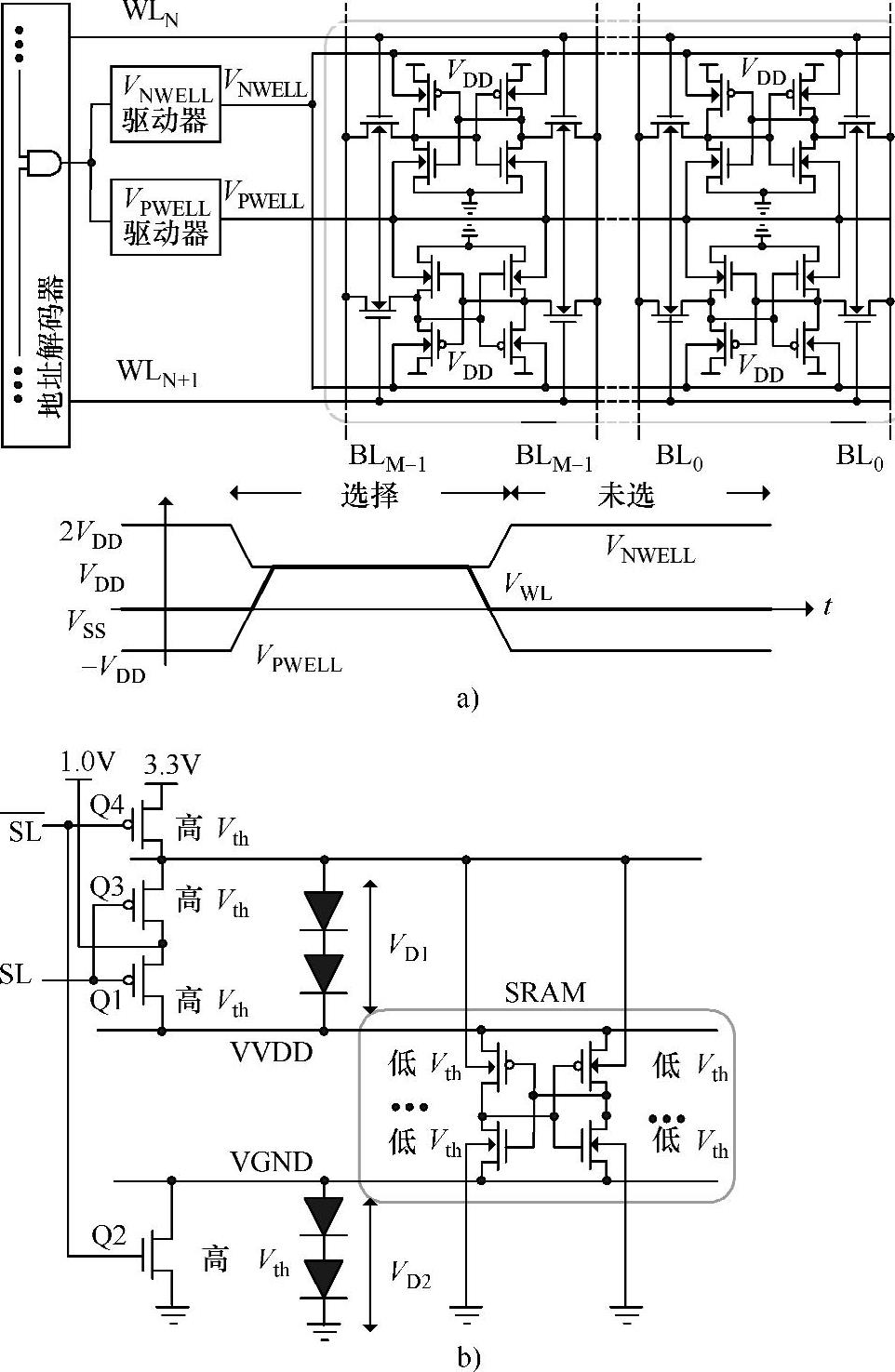

(2)可变阈值的泄漏抑制方案。在电路级泄漏抑制措施中,可调节的体偏置控制具有保持存储在锁存电路中数据的特性,因此被应用在存储器阵列中以减少亚阈区泄漏电流。与VTCMOS技术相似,未被选中的存储器单元的衬底电压被反向偏置以获得待机时的高Vth。图9-16a所示为是动态泄漏关断(Dynamic Leakage Cutoff,DLC)方案的电路图和时序图[78]。DLC使未被选中的SRAM单元的衬底施加偏置,对VNWELL大约为2VDD,对VPWELL约为-VDD。图9-16b所示为自动背栅控制MT-CMOS(Auto-Backgate-Controlled MT-CMOS,ABC-MT-CMOS)技术的配置[79]。在Q1、Q2和Q3开启而Q4关断时,动态工作电压为1V。在待机模式下,Q4开启而其他管子关断。ABC-MT-CMOS的VDD轨和地轨被二极管D1和D2钳位。在反向偏置电压VD1=VD2=1.15V时,泄漏电流被减小到20pA/cell。

(3)门控电源和超低待机电源电压方案。在结构级,降低SRAM运行期间泄漏电流的技术包括门控关断闲置部分存储器的电源电压或者使得使用频率很低的部分进入睡眠待机模式。这些方法使泄漏功耗的降低与VDD成二次方关系,并且在编译器级的缓存活跃率分析的帮助下实现了优化的功耗——性能折衷。缓存延迟技术在缓存互连门控中应用了适当的时序策略,以适当的性能损失节省70%的泄漏[28]功耗。如图9-17a所示,为进一步开发利用控制缓存泄漏电流技术,可以采用将未激活的缓存单元分配到低功耗模状态下,使Vdd得到降低,但是仍然可以保持存储器中的数据[29]。图9-17b所示的双轨待机方案是为超低功耗应用提出的,在待机期间,整个SRAM模块被推入到待机电源电压为300mV的深度睡眠。在这种超低的数据保持电压下可以减小超过90%的泄漏功耗[30],同时也说明了0.13μm工艺中300mV电压就可以实现稳定的数据保持,而数据保持电压(Data Retention Voltage,DRV)与阈值电压和沟道长度的工艺波动之间近似呈现出线性增加的关系。

图9-16 动态泄漏关断和自动背栅控制MT-CMOS

a)DLC方案的电路图和时序图 b)ABC-MT-CMOS电路的配置(a来源于参考文献[78]b来源于参考文献[79])(https://www.xing528.com)

2.运行阶段的低功耗DRAM

(1)外围电路功耗的减小。正如前面提到的,逻辑电路泄漏电流降低技术,如栅——源背偏、衬底——源背偏、多Vth和功率开关方式等,对存储器外围电路泄漏抑制来说是很有效的方法。另外,提高片上电压转换器的转换效率并且使它们的待机电流最小对低功耗DRAM设计非常重要。这是因为高速低压DRAM设计严重依赖于提升各种电流驱动和抑制亚阈区电流的方法。这些方法一般要求多个电平,例如背偏置、基准和预充电电压[6,90,91]。

图9-17 采用超低待机电源电压的SRAM泄漏抑制方案

a)处于睡眠的存储器电路 b)双轨SRAM待机方案和工艺对DRV的影响(a来源于参考文献[29];b来源于参考文献[30])

(2)刷新时间延长和循环充电。如9.2.3节提到的,延长刷新时间间隔可减小刷新电流。该方法通过部分数据线激活技术来实现,可为阵列操作提供灵活的控制[87]。循环充电是在刷新期间减小容性数据线功耗的另一种方法。其中,在一个阵列中使用并且在传统情况下每个周期泄放的电荷被转移到另一阵列得到再利用[90]。

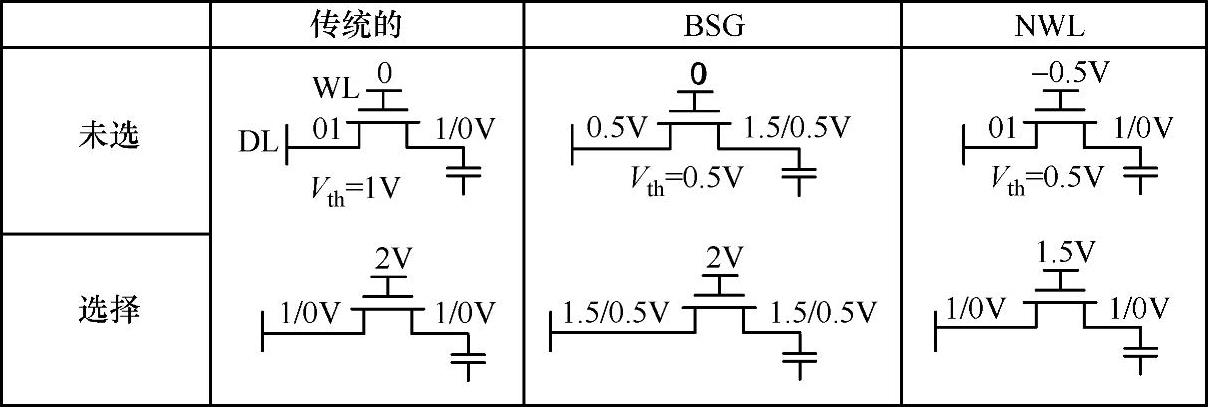

(3)DRAM单元的栅——源补偿驱动方案。提升的读出地(Boosted Sense Ground,BSG)和负字线(Negative Word-Line,NWL)技术作为DRAM单元中应用的栅——源补偿驱动方案已广为人知。这两种技术都通过动态的改变DRAM单元中晶体管的Vth来得到期望的动态驱动电流和较小的亚阈区电流。如图9-18所示,在待机期间,BSG将未选中单元的数据线电压抬高了ΔVDL,而NWL将栅电压减小了ΔVWL。在待机状态下增加的Vth可以抑制单元的泄漏电流并使DRAM单元中低Vth晶体管的使用成为可能。在上述对比中,常规方案的Vth取为1V而BSG和NWL则为0.5V。NWL中ΔVWL的产生相对容易些,因为与BSG中数据线电流沉相比,NWL中有字线放电电流。但是,这两种方法都增加了未选中单元的栅氧应力[92]。

图9-18 DRAM单元驱动方案的对比(假定Vth0=1V,并且存储电压为1V)(来源于参考文献[92])

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。