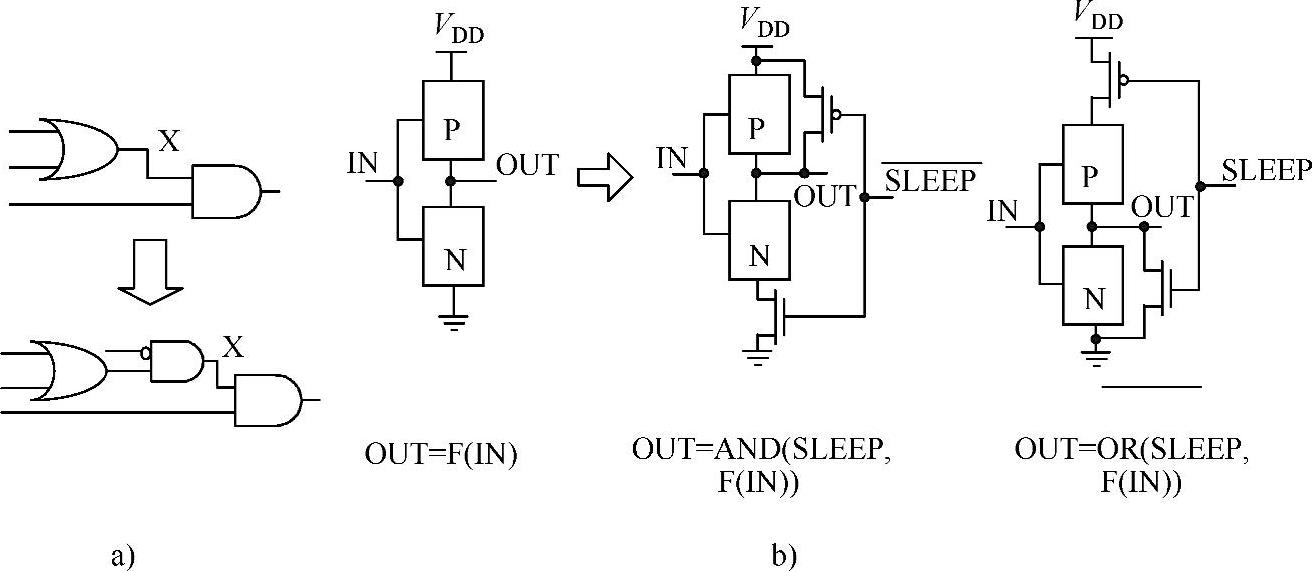

图9-13 应用输入向量控制电路内部节点的方法

a)插入多路复用器(简化为与门) b)门调整使输出控制成为可能。(来源于参考文献[45])

1.在运行阶段使用层叠效应

与设计时将单个器件变为层叠器件的强制层叠方法相似[27],针对运行阶段的各种其他低功耗技术通过将待机模式下的电路转换为层叠结构也能从层叠效应得到好处。考虑到在不同的输入向量作用下电路的泄漏功耗在较大范围变化较宽广[42],这些技术的目标是通过使待机状态的器件采用低泄漏输入向量的方法来减小门泄漏。为了获得与最小泄漏功耗相对应的输入向量,业已提出了大量的算法,包括置信水平给定时的随机采样[42]、原始估计[43]、以及基于可观察性泄漏测量[44]和布尔网络建模[45]的启发式搜索。对32位静态CMOS Kogg-Stone加法器,如果在输入端施加一个特定的输入向量,可以实现高达20%的泄漏减小[46]。对于具有较大逻辑深度的电路,已使用基于多路复用器插入和栅调整的方法来对内部节点实施控制[45]。如图9-13a所示,多路复用器的插入可以实现对内部节点X的存取。图中采用一个与门作为多路复用器,因为多路复用器的一个输入电平是固定值。图9-13b介绍了两种调整全互补CMOS门的方法,使得在待机状态下,器件输出端连接到1或0。采用这种方案,层叠效应使调整后的门和它的扇出门的泄漏得到减小。采用这两种方案的应用输入向量控制的基准电路以降低速度和增大面积为代价,节省了10%~70%的泄漏功耗[45]。除了这些针对内部节点的方法,另一种方式是在高泄漏状态下给这些内部门插入一个串联的低Vth开关[44]。在待机期间,这个串联泄漏控制开关切断了那些输入向量控制不能控制的泄漏门。

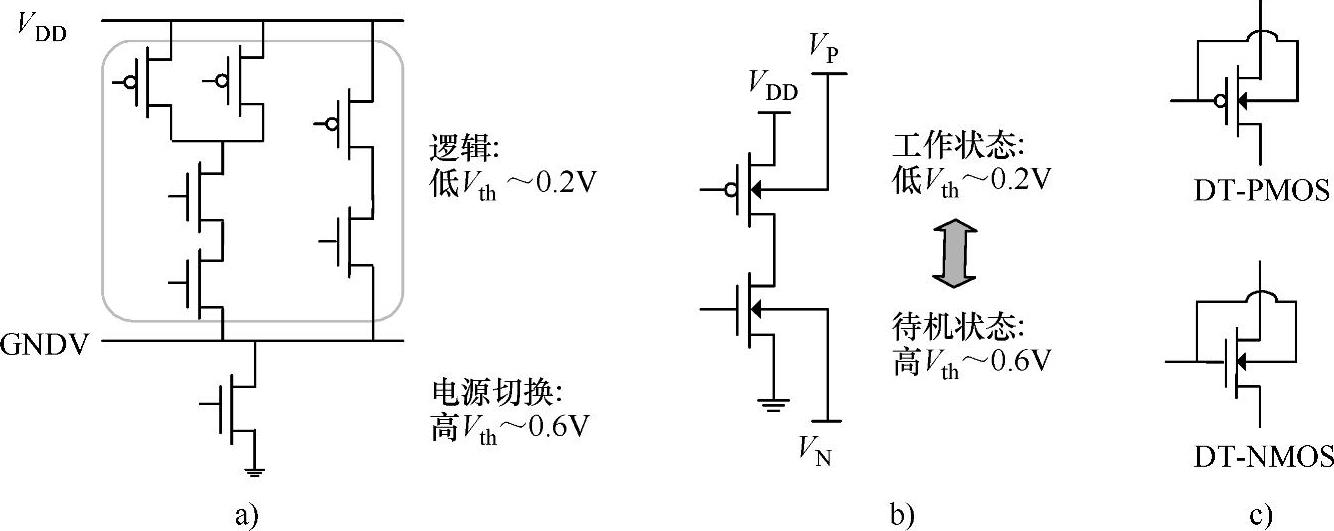

2.多阈值CMOS(Multi-Threshold CMOS,MTCMOS)

在电路级,有代表性的针对运行阶段低功耗技术是多阈值CMOS(MTC-MOS)[64]、可变阈值CMOS(Variable-Threshold CMOS,VTCMOS)[65]、动态阈值CMOS(Dynamic-Threshold CMOS,DTCMOS)[66]和其他的衍生技术。这些技术通过在待机模式下插入串联电阻或者增加器件阈值电压Vth的方法来减小待机泄漏电流。如图9-14a所示,MTCMOS通过串联高Vth功率开关的方式关断了低Vth逻辑模块。为了平衡工作时延和面积开销,需要一个尺寸合适的高Vth开关。为此,人们开发出了一种层次化的尺寸确定算法,针对给定的时延约束,使总的硅面积最小[67]。MTCMOS技术已成为众多低功耗设计中的一项非常有效的技术。然而,当VDD减小到1V以下时,由于高Vth器件的开启电压要求较高的电压,将导致MTCMOS的效率不断降低,并且最终会失去作用。对未来的低压工作条件,先后提出了包括超级截止CMOS(Super Cutoff CMOS,SCCMOS)[68]和栅压升高MOS(Boosted-Gate MOS,BGMOS)[69]在内的改进结构,使基于功率开关的泄漏抑制方案可以继续发挥效用。SCCMOS方法是给待机模式下的低Vth开关施加负的栅源偏置电压,而BGMOS方法则使用升高的栅源过驱动电压以加速高Vth开关的动作。这两个方法都有效抑制了低VDD时的泄漏电流,但是以额外的电平设计开销为代价。另外,曲折型超截止CMOS(Zigzag Super Cutoff CMOS,ZSCMOS)和曲折型栅压升高CMOS(Zigzag Boosted Gate CMOS,ZBGCMOS)方法作为SCCMOS和BGCMOS的衍生技术也被提出来以改善上电时间[76]。

3.VTCMOS(https://www.xing528.com)

VTCMOS技术如图9-14b所示,针对不同的工作模式,通过调整工作电路的衬底偏置来得到期望的阈值电压。与MTCMOS相比,VTCMOS要求的面积开销更小,并且衬底中的瞬态电流远小于从电源中抽取的动态电流。因为VTCMOS的动态工作不受泄漏控制的影响,因此VTCMOS的应用不会受到电源电压缩小的限制。然而,随着技术朝更小的沟道长度发展,衬底偏置控制对Vth的影响变得更弱[70]。衬底反偏置对短沟器件的影响,增加了芯片内Vth的分散性,从而减小了这一技术的有效性[71]。其结果是,使用正向偏置就成为未来实现VTCMOS的首选设计选择[6]。

图9-14 针对运行阶段的电路级低功耗工作方法

a)MTCMOS b)VTCMOS c)DTMOS

4.DTCMOS

虽然像MTCMOS和VTCMOS这类常规低功耗电路技术一直在不断发展以满足未来设计的要求,但DTCMOS技术则是在搁置了十年后才获得了电压低于1V电路设计的青睐。如图9-14c所示,1994年提出的DTCMOS技术采用的是将栅和衬底相连这样一种新颖的MOSFET工作方式[72]。这种连接方式使器件的Vth与栅压密切相关。在动态工作期间,Vgs增加时,Vth会降低,从而能够提供比采用低VDD的标准MOSFET更大的电流驱动能力。另一方面,空闲时的零Vgs会使Vth升高,可以有效地抑制泄漏电流。但是,为了防止过大的衬底电容和衬底电流,DTMOS的栅压必须小于约一个二极管正向电压(在室温下为0.7V),这就限制了这一技术在采用较高VDD的设计中的应用。采用SOI有助于减小结横截面积,缓解正向偏置的危害。已经提出了几种方法来消除低电压工作的限制,包括使用辅助的MOSFET或二极管将衬底-源钳位为正向偏置、或限制它的瞬态效应[73]。当未来的低功耗设计要求低电压工作时,DTCMOS将成为一项有竞争力的技术。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。