基于如工作负载这样的实时操作信息,运行阶段的系统级低功耗技术主要用来优化系统管理策略。这些技术包括与功耗相关的不同动态安排方案(根据估计的执行时间来安排任务[21])、动态功耗管理(Dynamic Power Management,DPM)(动态地重新配置一个电子系统,以最小数量的有源元件提供要求的服务[22])、以及通信网络应用中与功耗相关的布线[23]。

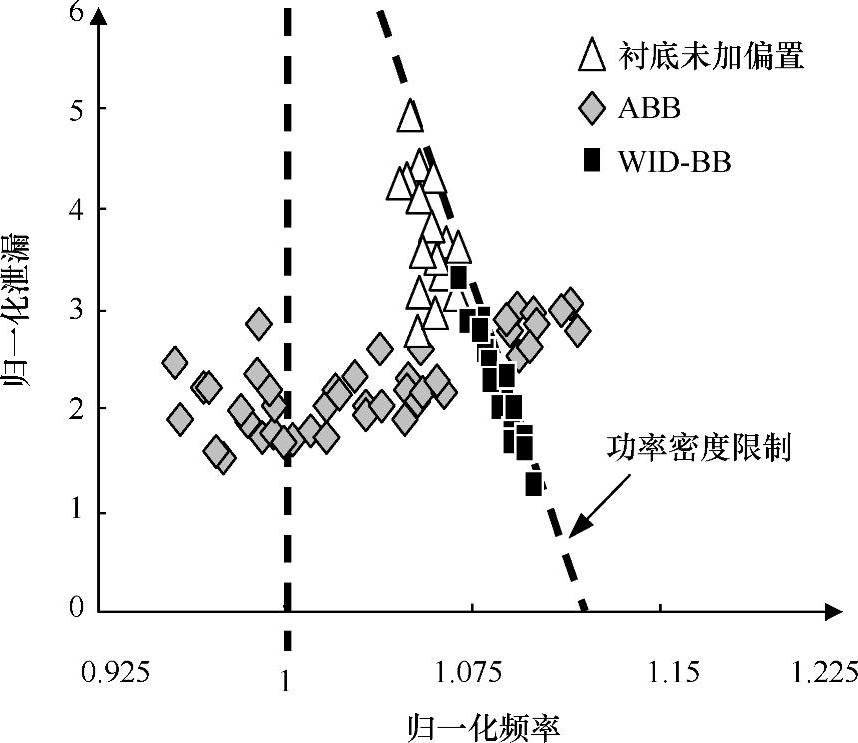

在结构级中,如果是通过反馈环路控制VDD和系统时钟频率来执行一个特定的任务,采用动态电压和频率缩小技术(Dynamic Voltage and Frequency Scaling,DVS,也称为DFS和DVFS)[24]是广为人知的功耗减小方法。为了进一步减小空闲期间的泄漏,可以采用动态Vth缩放(Dynamic Vth Scaling,DVTS)[25]方法,通过体偏置控制的方式实现阈值电压的自适应调整。衬底正偏(Forward Body Bias,FBB)和定向自适应衬底偏置(Adaptive Body Bias,ABB)已用作为通常衬底反偏(Reverse Body Bias,RBB)控制的增强技术。FBB具有我们期望的改善晶体管短沟道效应的效果,这样就减小了对特征尺寸变化的敏感度[85]。为了补偿芯片范围内的参数波动效应,提出了芯片内ABB(WID-ABB)技术。该技术集成有相位检测器并且分别给每个电路模块提供合适的衬底偏置。ABB和WID-ABB的作用效果如图9-11所示。只采用ABB技术就可以使芯片范围频率分布的标准偏差σ减小7倍,结合采用WID-ABB技术,可以使σ再减小三倍,从而在最高的频率窗口下几乎100%的芯片都满足要求[86]。VDD和Vth跳跃技术与DVS技术类似。该技术将VDD和Vth调整为由软件反馈环控制的几种离散值[26]。

图9-11 ABB和WID-ABB控制对泄漏与频率分布的影响(来源于参考文献[86])

FBB和ABB技术不是没有问题。衬底噪声将对电路性能产生影响,除非对衬底偏置电源进行很好的去耦处理,使其像一个独立的电源。但是去耦需要占用布线资源,同时去耦电容还会增大芯片面积。如果FBB将体电压抬升得太高,使晶体管的结正向偏置,还会有发生闩锁的危险。FBB也会增加结电容并增加芯片的动态功耗。自适应衬底负偏置是低功耗设计愿意采用的方式。衬底负偏置减小了结电容和亚阈区泄漏,因此能改善动态功耗和待机功耗。

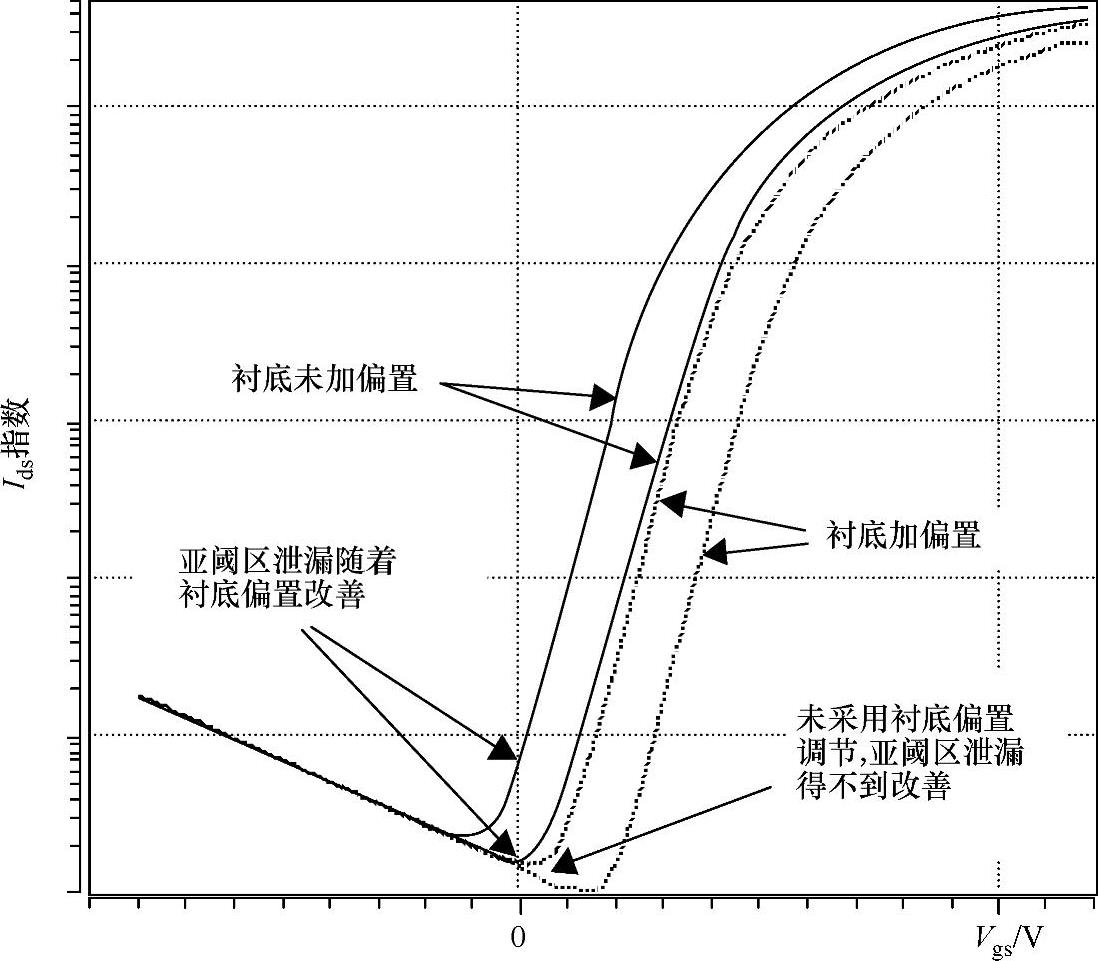

为了使衬底偏置能起到作用,必须使晶体管在较高的体效应下才会开启,这样负的衬底偏置将会提升Vth,从而减小泄漏电流。栅感应漏泄漏(GIDL)在90nm节点和尺寸更小的工艺中影响将会明显。GIDL改变了器件的亚阈区曲线,使得泄漏电流随着栅驱动的减小而增加。衬底偏置加剧了这个效应,使衬底偏置起了负面作用(见图9-12)。(https://www.xing528.com)

图9-12 为了使衬底偏置效应发挥作用,晶体管必须进行调整

对于可靠性要求较高的服务器类高性能微处理器,需要进行可靠性老炼。许多情况下,由于电源功率有限,为了防止老炼过程中只有一部分得到老炼,就要限制同时老炼的器件数。这严重限制着老炼的产量,迫使设计者通过牺牲性能的途径来减小功耗,使得同一个烘箱中,器件中更多的部分可以同时得到老炼。如果采用衬底负偏置可以用来减小老炼中的亚阈功耗,这样设计者就无需牺牲性能来方便微处理器的老炼[104]。

时钟分布网络是另一个主要的功耗源,特别是在高性能微处理器设计中。在72W 600MHz的Alpha处理器中,一半功率消耗在时钟网络上[93]。在解决这个问题的各种方法中,时钟门控[75]是一项重要的针对运行阶段的结构级低功耗技术。该技术通过阻止逻辑模块中的不必要活动以及消除时钟网络中不必要的功耗,使得与时钟有关的有源功耗得到有效的最小化。虽然只要在电路中插入开关就可以很方便地实现时钟门控,但是给结构级优化带来了许多问题,包括采用最少总互连长度的时钟树构建、时钟的时序约束管理、门控时钟网络不对称的最小化等。除了时钟门控,还提出了新的共振时钟结构,使用耦合行波和驻波振荡器或者基于螺旋电感的共振网格[94-96]。在这些方法中,电磁能量在LC系统中振荡而不是像RC那样转化为热,因此,减少了功率损耗。在谐振频率为1.1GHz时,可以获得高达80%的时钟功率节省[96]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。