单片随机存取存储器(RAM)和嵌入式RAM具有高密度、低功耗和低成本的特点,为不同电子系统的改善起到重要作用。现今,微处理器设计中融合了大量的存储器单元,而存储器将消耗系统功耗预算的很大部分。例如,Alpha 21246功耗预算的30%和StrongARM功耗预算的60%都用于缓存和存储器结构[60]。对采用电池供电并且具有低占空比的设备,存储器漏电流功耗甚至可以占据系统总功耗的主要部分并且决定电池的寿命。各种应用中对系统功耗优化的需求,使得低功耗存储器的设计成为一个发展迅速、硕果显著的领域。9.2.3和9.3.3节将分别介绍低功耗SRAM和DRAM的设计技术和运行技术[6,31]。

1.低功耗SRAM设计

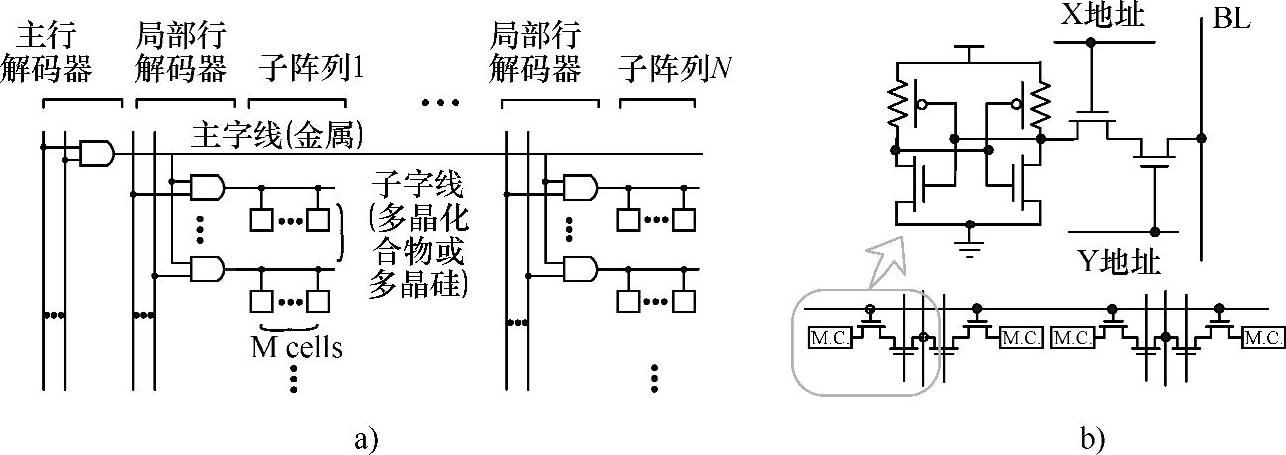

(1)按块划分的字线和位线的局部激活。局部激活是减小SRAM中大负载的字线和位线充电电容的极为有效的方式。只要将存储器阵列简单地分割为子模块[14],就可以极大地减小字线和位线的负载。然而,由于需要附加的控制逻辑和布线,使得这个技术有极大的局限性。其他技术则保持了存储器阵列的完整性,而重点在于译码逻辑的重构。如图9-6a所示,分割字线(Divided-Word-Line,DWL)方式[15]采用两级分层行解码器结构。在每次访问存储器期间,只有一条子字线被激活,这样,相比未分割的主字线模式,一般只有10%~25%的电容引入电路,这就就相应地减小了功耗和字线时延。DWL方式在1MB以及更高密度的SRAM中已被广泛地使用[14]。为了进一步减小电容,还可以采用将DWL和多行解码器及三级分层行解码方案结合起来的方法。还有一种单个位线交叉点单元激活(Single-bit-line Cross-point cell Activation,SCPA)结构[59]的方式,即通过单个单元激活来实现位线电流最小化。如图9-6b所示,存储器存取仅激活X和Y地址控制的交叉点上的那个SRAM单元。据报道,与传统的DWL结构相比,采用SCPA实现的16MB SRAM可以减小36%的激活电流和10%的面积。

图9-6 按块分割字线的局部激活方案

a)DWL结构 b)SCPA结构使用的SRAM单元(a来源于参考文献[15];b来源于参考文献[59])

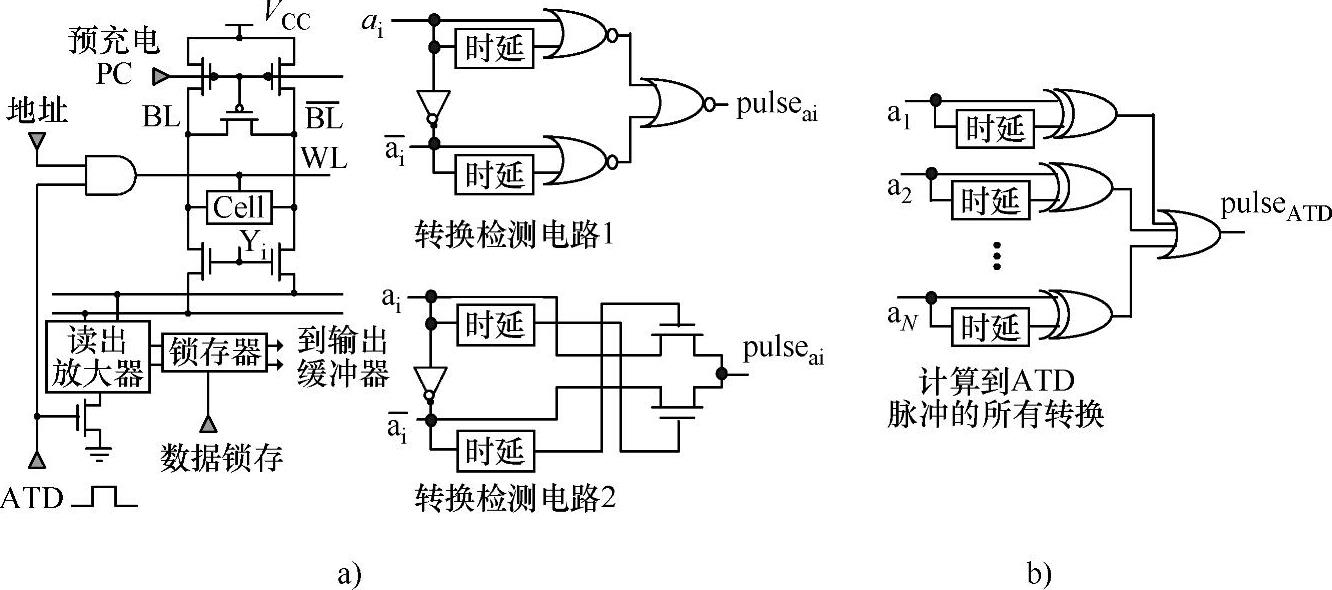

(2)脉冲操作。脉冲字线(Pulsed Word Line,PWL)操作可以将工作时的占空比降低到读和写操作所需的最小时间[61],因此就减小了存储器存取期间的动态功耗。图9-7a显示的是PWL的部分电路图和时序图。该电路中的地址转换检测(Address Transition Detection,ATD)[6]单元用来检测地址和检测信号转换,并产生脉冲信号。电路图中所示的XD脉冲在ATD上升时形成,并通过X解码器和读出放大器控制字线操作。ATD脉冲产生电路如图9-7b所示。这个脉冲电路也可以用于高容性负载预解码线、写总线、位线和读出电路[16-20]。

图9-7 PWL操作

a)部分电路和时序图 b)ATD脉冲产生电路

(a来源于参考文献[61];b来源于参考文献[6])

(3)降低VDD时的单元驱动方案。减小电源电压能够有效地抑制SRAM的动态和静态功耗,因此,在过去的十年间,出现了许多工作电压低于1V的低功耗SRAM。为了在电源电压为0.5~0.8V时实现100MHz操作,设计中采用了各种

图9-8 DSL和NWD方案

a)DSL单元和读/写周期时序图 b)NWD单元和读/写周期时序图(a来源于参考文献[11];b来源于参考文献[12])(https://www.xing528.com)

各样的单元驱动形式,如驱动源极互连(Driving Source Line,DSL)[11],负字线驱动(Negative Word-line Driving,NWD)[12]以及升压接地补偿数据存储(Boosted Offset-Grounded data Storage,BOGS)[13]。图9-8显示的是DSL和NWD的单元电路图以及工作波形。DSL方式是在读取操作期间,将交叉耦合反相器的源极互连连接到负电压VBB上,而在写操作期间源极互连悬空。这样,单元的读取时间由于栅源电压增加和晶体管源——衬底结的正向偏置的提升而得到了改善。由于交叉耦合反相器对中的NMOS晶体管处于未激活态,写周期也同样得到了改善。NWD方式使用了截止栅压为负的低Vth导通管(Q1和Q2),和提升了栅压(VCH>VCC)的高Vth交叉耦合反相器对来实现存取时间的改善和待机泄漏电流的减小。通过对栅源偏置和Vth的控制,与常规的单元相比,DSL和NWD方式在低于1V的电源电压下提高了存储器的工作速度,并且抑制了静态待机泄漏电流。然而,这些方案的应用中包括了几种系统开销,如DSL方式下产生负电源电压的电荷泵运行效率低和NWD方式下从提升电压增加的存储节点到位线的高泄漏流。BOGS就是为解决这些问题而提出的另外一种单元驱动电路。其中将数据存储节点对的电势从0.5V/0V变到1.3V/0.65V,这样就消除了产生负的源极互连电压的需求。调整位线预充电和字线驱动之间提升的电势,可以避免从电压增加的存储节点到位线的泄漏。该方法同样也使用了循环充电的方式以节省源线电压控制电路的功耗。

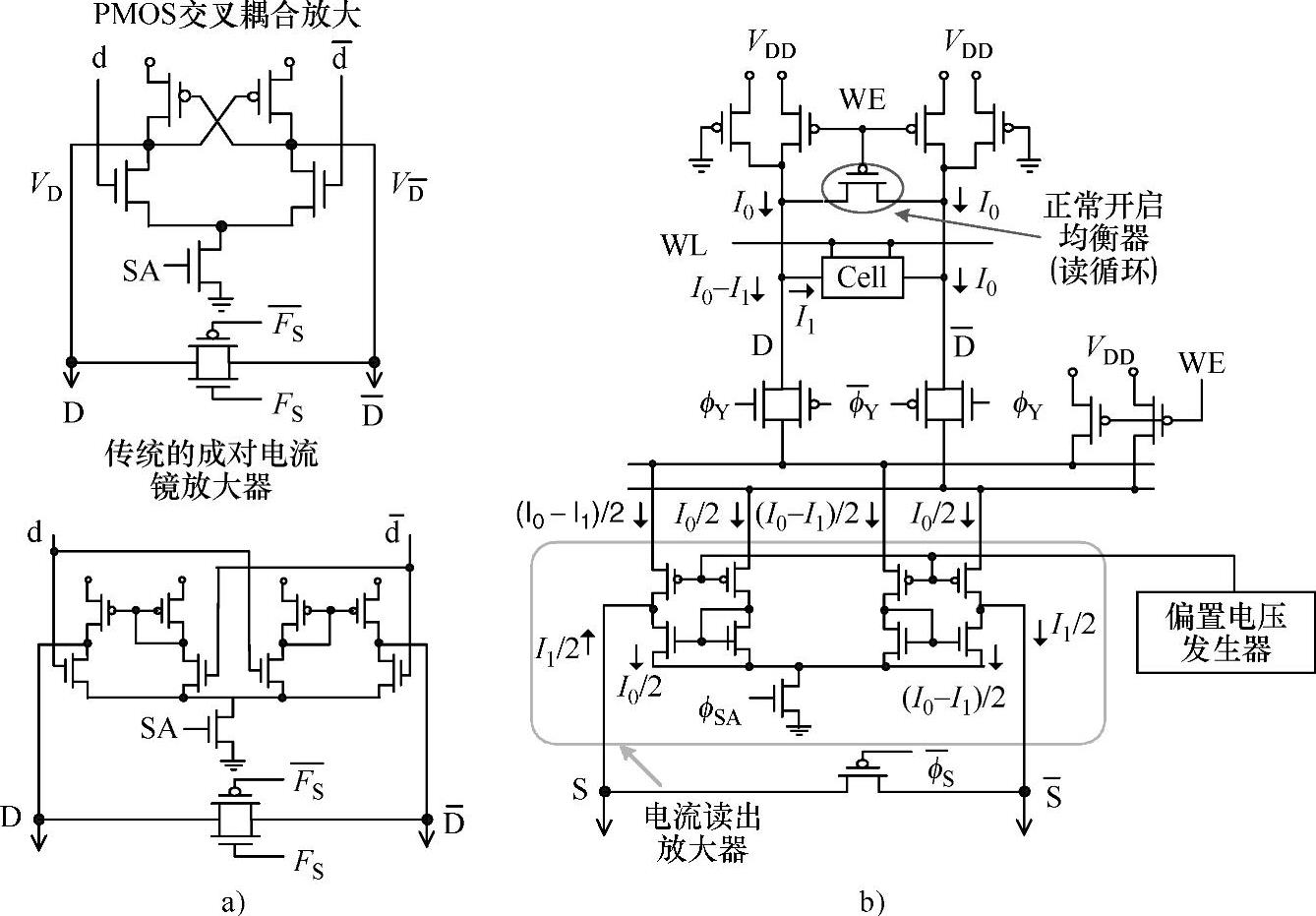

(4)低功耗读出放大器设计。I/O线上的读出放大器一般消耗1~5mA的直流电流[6]。为了获得更高的数据流量,高速处理器会增加其I/O线的数目,这样读出放大器上的功耗将成为芯片总功耗中一个很大的组成部分。如图9-7所示,通过仅在脉冲高电平期间使电路工作,这种脉冲操作方案可以有效地减小读出放大器的功耗。图9-9a所示为一种1989年提出的锁存型PMOS交叉耦合读出放大器设计[62]。与通常的电流镜运放对相比,这种设计使读出时延减小了50%,并且使全输出摆幅时的电流减小了80%。为了稳态工作,需要精确的时序来控制均衡器,从而使该放大器输出达到平衡。图9-9b所示为另一种高速读出放大器的设计[63]。该放大器读出的是位线电流差异而不是电压差。采用这种设计,可检测的数据线电压摆幅降低到小于30mV。与常规的要求电压摆幅为100~300mV的电压型读出放大器相比,在延迟时间固定为1.2ns的情况下,这种电流型读出放大器设计节省了60%的功耗[64]。因为这种设计中的位线电压保

图9-9 高速低功耗读出放大器设计

a)PMOS交叉耦合放大器设计 b)电流读出放大器设计(a来源于参考文献[62];b来源于参考文献[63])

持相等,读出放大器本身拥有均衡的功能,因此简化了工作的时序控制。

2.低功耗DRAM设计

在过去的10年中,电路技术的持续发展,使DRAM在容量不变的前提下,功耗减小了两到三个数量级。与SRAM的情况相似,DRAM中减小的动态电流有助于实现低功耗、低结温和低成本封装。充电电容和工作电压的减小已成为控制DRAM动态功耗的主要技术。同时,亚阈区电流抑制措施,如待机负栅源偏置等,将是未来电池供电的DRAM系统中必不可少的[6]方法。

作为VLSI存储器系统中的关键部件,DRAM和SRAM在工作、结构和功耗产生原因等方面都是相似的。因此,它们可以共享许多相似的降低功耗技术。因为本章节已对低功耗SRAM设计进行了讨论,因此,下面只对DRAM设计阶段和运行阶段的功耗控制进行简要叙述,而着重于专门针对DRAM结构的设计技术。

(1)充电电容的减小和刷新时间的延长。与SRAM中的DWL[15]和SCPA[59]相似,分块的数据和字线的局部激活技术可以用来减小充电电容。这就降低了动态功耗,并提高了存储器访问时的信噪比。图9-10a和图9-10b分别所示为采用DRAM数据线和字线局部激活的电路示意图[87,88]。在这些方法中,数据和字线被分割成多个部分。这些子块由附加的控制逻辑激活,例如部分数据线激活中的Y解码器和部分字线激活中的行选择线RX。共享的I/O、读出放大器和解码逻辑有助于减小控制电路的系统开销[87]。配合部分激活方案一起使用的另一种静态电流减小技术是刷新时间的延长[87]。通过灵活地控制数据线的子片段,可以延长存储器刷新时间而不会影响正常的操作。这是通过在刷新周期控制数倍于普通周期中同时激活的阵列数实现的。自刷新时间的延长使得刷新电流和DRAM静态功耗均得到减小。

(2)工作电压的减小。受面积尺寸和低功耗需求的驱使,DRAM电源电压已经从20年前的12V减小到现在接近1V的水平。然而,进一步缩小到sub-1V范围则面临着巨大的挑战,因为此时将会产生工作速度的衰退和Vth的减小引起泄漏功耗的恶化。克服这些困难的关键在于高速读出放大器与存储器操作的设计以及有效的亚阈区泄漏抑制策略,这些内容将在后面的运行阶段的存储器低功耗技术部分进行介绍。另外,对数据线采用VDD/2预充电的方式[89],在减小电压摆幅的情况下可将数据线功耗减小一半。同时,存储和预充电时引起的较大尖刺电流也被减半,从而可以实现低噪声操作。最后,在各种各样的存储器功耗控制技术中必不可少的一项技术就是片上降压转换器,可以产生所需的不同电压,如(VDD/2)数据线操作方案中的预充电电压。这些转换器在负载电流快速变化的情况下提供稳定且精确的输出电压[6]。

图9-10 DRAM功耗减小的部分激活方案

a)多次分割数据线的部分激活 b)多次分割字线的部分激活(a来源于参考文献[87];b来源于参考文献[88])

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。