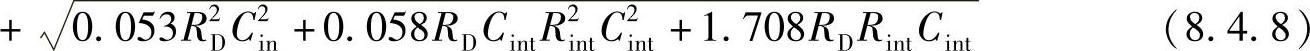

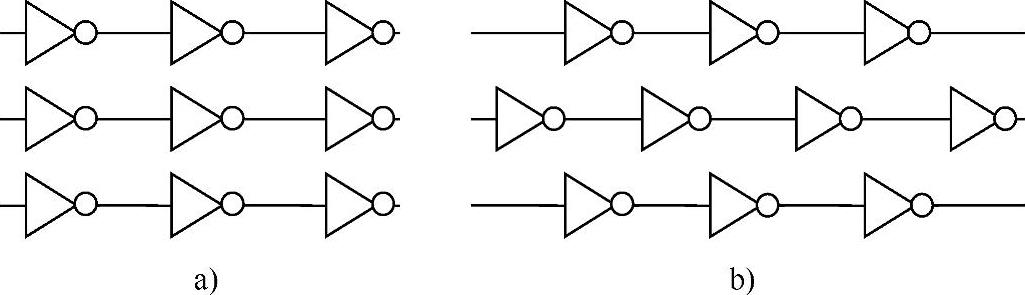

插入转发器 插入转发器(缓冲器)技术对减小长互连的长时延是很有效的,但是要付出的代价是芯片面积和功耗的增加。该技术是将长互连分割,并在各个片段之间插入驱动器(转发器)(见图8-20),可以使互连长度与时延关系从平方降为线性,从而极大地缓解了长互连的时延问题。因为CMOS驱动器的特性,插入转发器也极大地改善了远端驱动器的信号压摆率。因为实际情况下,驱动器和接收器的尺寸与转发器的尺寸不同,除了路径上第一个和最后一个片段外,转发器一般以均匀间隔插入。另外,在实际设计中,转发器一般也是采用级联反相器对实现,以尽可能地减小时延。

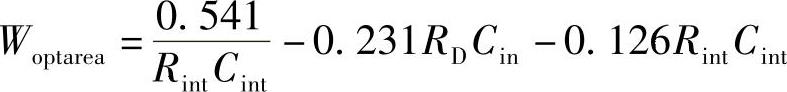

对RC互连,普遍采用的最优缓冲器尺寸表达式是Bakoglu方程[34]。最优转发器的个数是

式中,R0和C0分别是最小尺寸转发器的输出电阻和输入电容。转发器的尺寸为

然而,由式(8.4.7)计算得到的结果经常太大以致于不太现实。典型的标准单元库中包括的是最小尺寸50~100倍的反相器或缓冲器,而式(8.4.7)给出的结果范围则高达最小尺寸的400~700倍。实际上,为了承受较大的时延,一般是插入适当的转发器而不是最优的转发器。参考文献[59]中给出的表达式优化的是加权时延-面积积,而不是纯粹的时延度量。其结果比式(8.4.7)给出的小了50%~60%量级:

基于式(8.4.8)的时延较高,但是面积和功耗的成本相对较小,如果再优化能量-时延积,其值将会更小。

图8-20 通过插入转发器减小RC互连时延

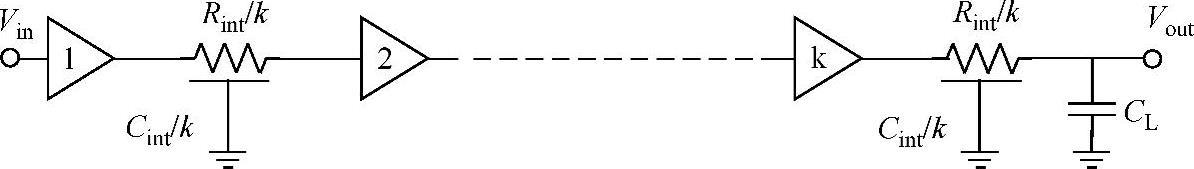

如果将一条互连分成更多的较短片段,则网络具有更强的抗噪声能力。转发器的插入减小了互连的平行长度,从而强烈地影响着串扰噪声。图8-21表明了采用和未采用转发器两种情况下噪声对受害线网络的影响。上面的互连是攻击线网络,下面的互连是受害线。如图所示,插入缓冲器后在插入缓冲器的输入端出现的噪声脉冲(见图8-21b)比图8-21a中接收器输入端的噪声脉冲要小。由于缓冲器的特性,这个较小的噪声很容易得到抑制。对感性噪声耦合,由于原先的电流返回路径现在经由转发器返回,这就缩短了电流返回路径长度,使得电流回路变小,从而感性耦合也变小。不过,因为LC互连的时间常数 与互连长度近似成线性关系,而不是RC情况下的平方关系,插入转发器对RLC互连时延的减小基本没有作用。

与互连长度近似成线性关系,而不是RC情况下的平方关系,插入转发器对RLC互连时延的减小基本没有作用。

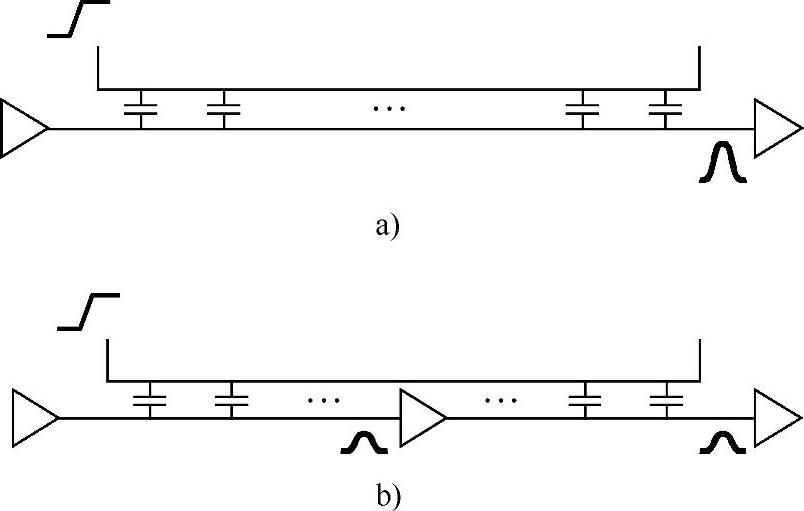

在相邻互连上分别插入转发器时,使插入的转发器相互错开可以使耦合电容对时延和串扰噪声的影响最小(见图8-22)[8]。转发器的偏移错开放置要求是使每个门位于它邻近门互连负载的中间。因为潜在的最坏邻近互连同时开关情况针对的只是受害线长度的一半,所以有效的开关因子被限制到1以内。而由于对称的缘故,受害线的另一半将经历属于最好情况的邻线开关活动。采用错开的转发器,可以极大地减小由邻近互连开关活动引起的时延不确定性。

图8-21 转发器有助于抑制受害线网络上的耦合噪声

a)无转发器情况 b)有转发器情况(来源于参考文献[63])

图8-22 错开转发器以减小开关模式引起的时延波动(https://www.xing528.com)

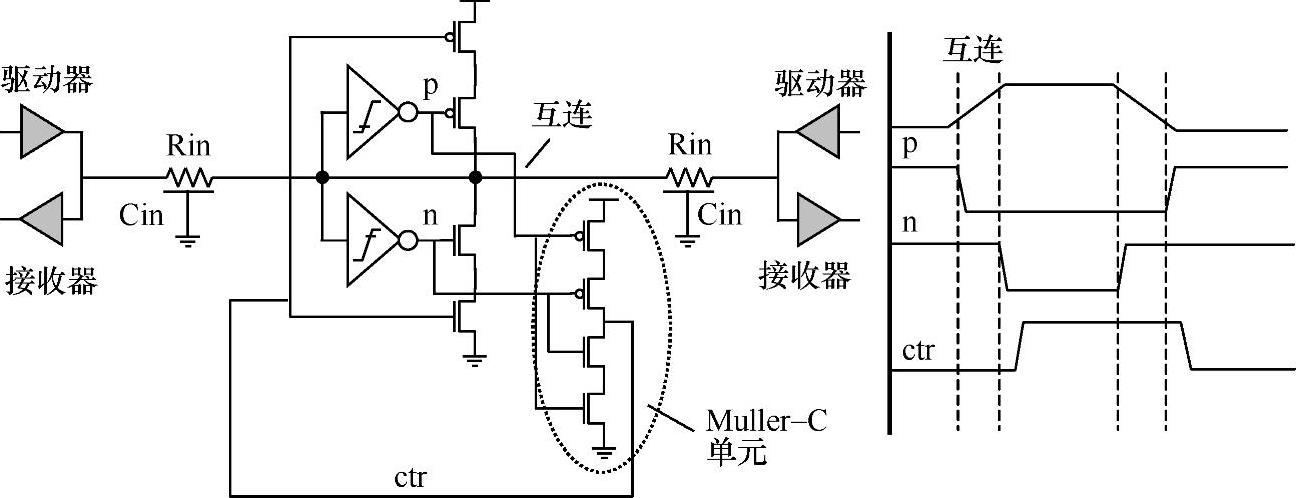

最新研究表明,转发器占用了越来越大的面积、功耗和设计资源,并且关键在于它们对性能的改善是有限度的。最近几年出现了一些关于更有效地驱动长互连方面的创新设计,包括可恢复的提升器[60,61]。与转发器不同,提升器是沿着互连加上去以局部地增强所传输的信号,它并不改变互连布线。提升器能够即时感受到互连上电压的跳变,提供一个额外的电流提升以加速跳变。提升器的电路原理图和时序图如图8-23所示。该提升电路有两个错位的反相器,用以在跳变尚未到达正常反相器之前检测到跳变。由它们再驱动一条反馈路径从而局部加速开关信号。另外,又引入一个Muller-C电容元件以防止在VDD和GND之间形成直接通路。这个提升电路的一个优点是它的性能对布局的变化不敏感,并且几乎可以被放置在总线上的任何一点;这样基本的信号布线约束对它们的影响很小。另外,它不改变信号的极性,支持双向传输和多驱动源配置。一些实验已经表明,使用恢复提升器技术能驱动更长的互连,并且比转发器方案节省面积和功耗。然而,设计提升器的主要难点是潜在的亚稳定性问题,这是具有正反馈的电路所固有的,其禁止具有不同脉冲宽度的信号传输通过。

图8-23 提升电路实例

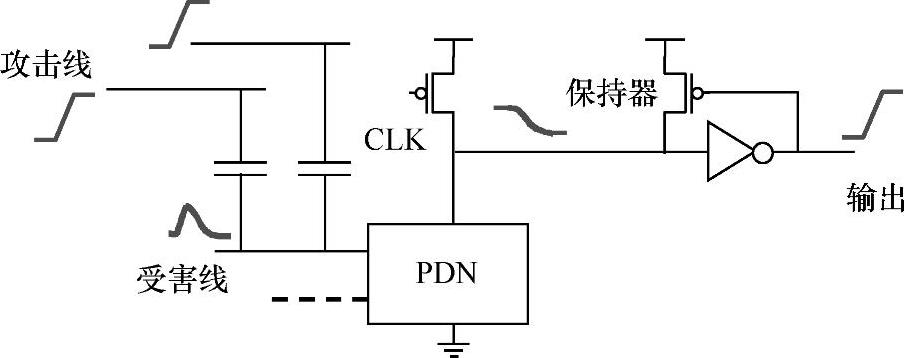

保持器电路 在微处理器的关键性能单元和其他高性能VLSI电路中经常采用动态门。与静态CMOS门不同,在动态节点上由于噪声引起的电荷损失是不能恢复的,从而动态门比静态CMOS门更易受到噪声的伤害。采用称作保持器的上拉和/或下拉器件形成静态通路,可以避免动态门节点的浮空(见图8-24)[62]。保持器电路可以恢复由耦合噪声、电荷共享和亚阈值漏电流引起的电荷损失。然而,随着噪声和漏电流的不断增加,必须相应地加大保持器的尺寸,这会使动态电路的性能明显下降。

图8-24 保持器可以恢复动态电路损失的电荷

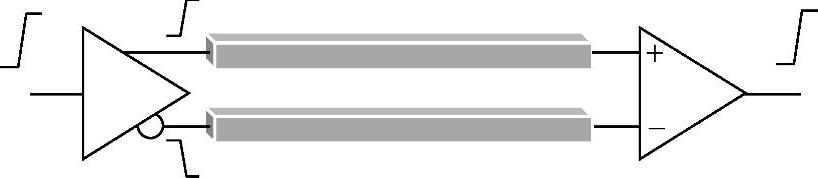

图8-25 差分信令

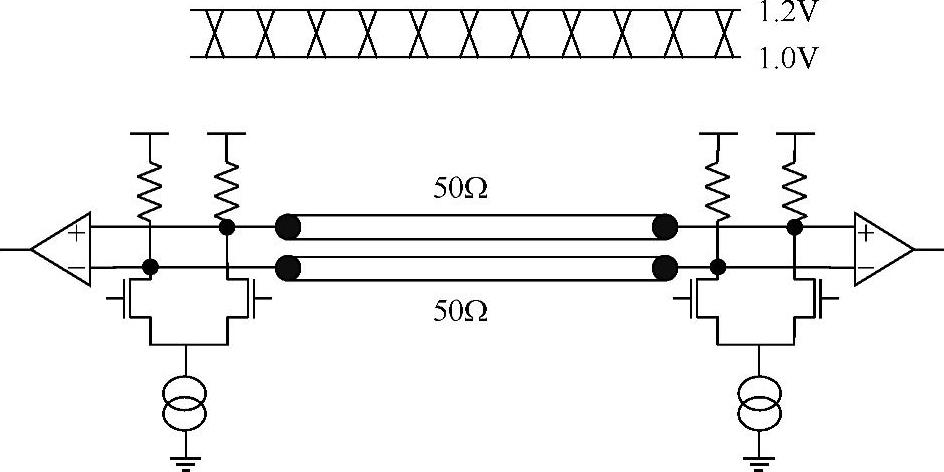

差分信号 与单端信号相比,差分信号自然就具有更鲁棒的抗噪声能力。差分信号的基本概念如图8-25所示,其中两条紧耦合的互连以差分的方式传送数据。在接收处,将这两个信号加以比较以确定它们的逻辑极性。差分信号可以用电压模式和电流模式实现。

差分信号机制具有高抑制共模干扰能力,这些干扰包括串扰噪声和电源轨波动。它也提供了一些单端信号所不具备的其他优点,包括:

(1)对每条信号线,它有一条很邻近的内建返回路径,因此几乎没有耦合到其他网络的噪声;

(2)因为具有的抗噪声能力高,就可以采用较低的信号摆幅,达到减小功耗的目的——已经证明,摆幅低至200mV的情况也能正常工作;

(3)信号与电源轨及其相关噪声隔离,使差分接收器受到的所有电源噪声都是共模形式,而差分接收器又都设计有非常好的共模抑制能力。因此,差分信号可以工作在噪声更大的环境中,并且可以工作的信号速率比单端电路更高。然而,实现这个技术需要付出巨大的代价。因为N个信号需要2×N条布线通道。发送器和接收器也要有大量的设计管理,并且容易受到时钟错位和抖动变化的危害。

将差分信号与电流模逻辑结合的技术已经广泛应用到片外互连中。图8-26显示的是工作于6.4GHz的电流模双向差分信号实例。下一代的高性能电路,当芯片工作频率升高或电源噪声产生的错位太大,导致感性噪声是片上的主要问题时,这一技术会成为片上互连一个很有前途的解决途径。

图8-26 双向差分信号实例

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。