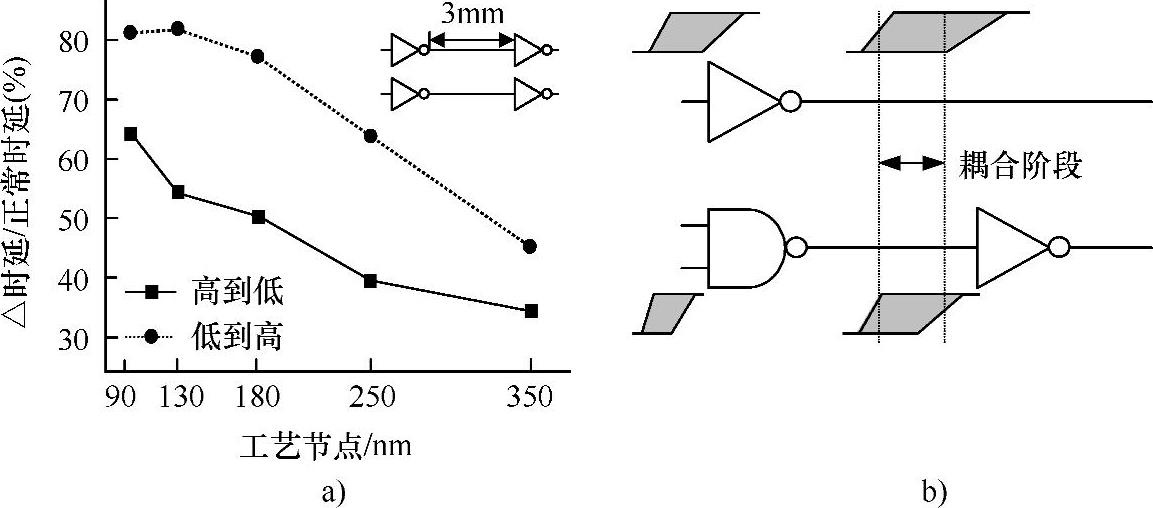

如果设计中采用的金属节距更近、纵横比更大和工作频率更高,就更容易受到互连耦合效应的影响。过大的串扰噪声会引起受害线网络出现错误的开关动作;即使是较小的噪声也能极大地改变受害线的时延,引起时延抖动。当某一级(包括门和互连)的时序,由于附近门的开关活动形成时延抖动,就会导致这种时序的不确定。由于CMOS逻辑具有恢复特性,只有大于接收器开关阈值的噪声毛刺才会引起逻辑功能故障。相比之下,对于较短的互连(小于500μm),时延抖动则更加普遍,并且很容易大于标称时延的20~30%[51]。图8-15a所示为各工艺级别中3mm全局互连时延不确定性的增加情况。该例中,最坏情况是,纳米领域归一化的时延抖动已经接近80%(注意,在从低到高的跳变中,时延抖动更严重,因为此时受害的PMOS比攻击的NMOS更脆弱)[51]。像这样巨大的时延不确定性给具有更严格时序预算的高性能设计提出了严酷的挑战。

图8-15 使用开关窗口法进行的考虑噪声耦合效应的时序分析

a)噪声引起时延抖动的发展趋势 b)基于开关窗口的时序分析(阴影区代表可能开关活动的时间窗口)

为了避免最坏耦合情况下的芯片时序故障,最重要的是在进行静态时序分析(Static Timing Analysis,STA)时应考虑时延抖动,并预留足够的容限以能够承受时延的波动。在RC分析中,广泛采用的一种计算最早和最迟串扰时延的方法是,利用开关因子(其取值区间为[0,2],或更精确的是[-1,3]),将各个关键路径上的耦合电容折算为等效到地电容。这一技术既稳妥又容易实现,而且不需要邻近网络的信息。然而,虽然这种简化降低了分析的复杂度,但是它会导致过分悲观的估计或过分严格的布线间距,因为事实上串扰噪声只是当攻击线和受害线同时开关时才会影响信号时延。如果攻击线和受害线的开关没有重叠,那么就不需要考虑时延抖动。因此,常规的方法往往过高地估计了时序的界限并浪费了计算时间。

改善噪声敏感STA精度的关键是应该包括关于信号网络的时域和功能信息。这可以通过引入开关窗口(又称时序窗口)的概念加以实现。这一窗口是指节点发生跳变的那段时间,如图8-15b[52,53]所示。两个耦合节点的信号时延只有当它们开关窗口重叠导致串扰噪声时才可能出现变动;否则信号时延不受时延抖动的影响(见图8-15b)。剩下的问题就是如何确定每个节点的开关窗口。为此,虽然可以直接采用攻击线的时序信息,但是攻击线的开关窗口又要受到受害线开关窗口的影响,这就是典型“鸡和蛋”的问题。虽然有多种方法可以化解这个循环,一个比较普遍的方案就是反复的计算迭代[53,54]。首先,我们可以为网络假定一个初始耦合情况(例如最坏情况耦合),运行时延引擎以估计每个节点的时延界限(即开关窗口),再根据开关窗口之间的相互关系重新估计耦合情况。重复这个过程直到时序窗口收敛[52]。(https://www.xing528.com)

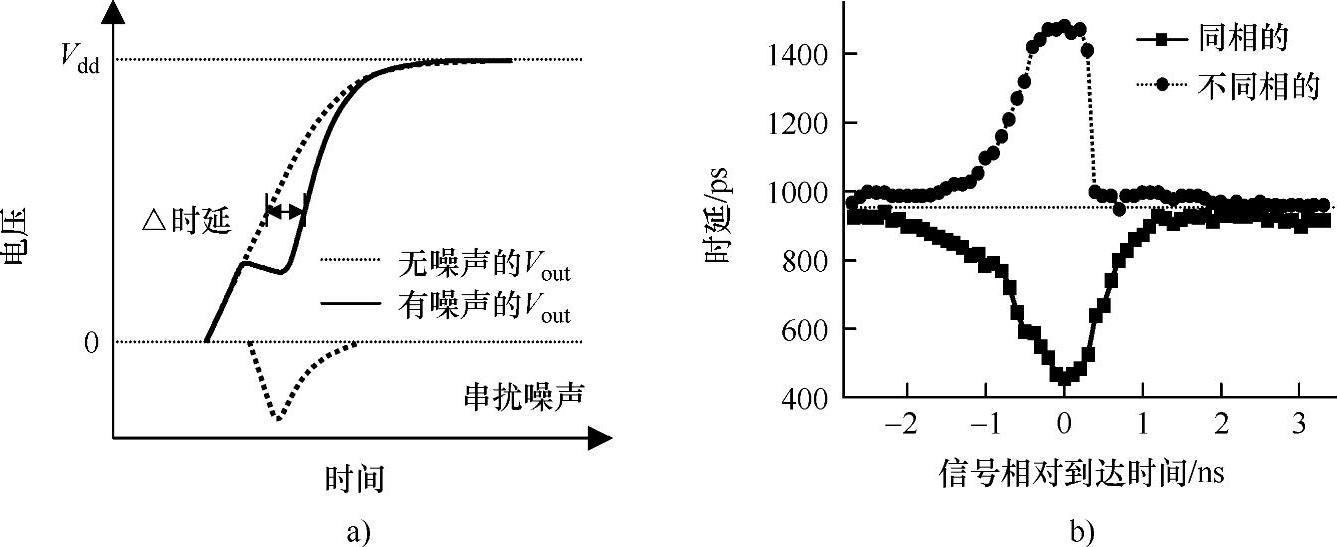

使用基于开关窗口的噪声敏感时序分析可以极大地减小时延界限估计的悲观性。在这一框架下,根据对串扰和时延抖动基本关系的认识,在改善时序窗口计算的效率和精度方面已经取得不少进展。如图8-16a所示,受害线时延在串扰噪声出现时会发生变化,因为噪声波形耦合到受害线后使得初始的电压传播发生失真。随着噪声注入位置的不同,可以观察到时延的不同变化。如果知道开关电压和噪声毛刺的标称特性,又知道攻击线和受害线的输入时序信息,就可以采用波形重叠方法预测这一级输出的时延抖动。时延变化曲线(Delay Change Curve,DCC)验证了这一想法。DCC表示的是时延与攻击线和受害线之间信号相对到达时间的关系[51,55,56]。图8-16b所示为0.35μm工艺中长度为6mm的全局互连的DCC测量结果[51]。通过使用DCC,与传统的使用开关因子估计的时延区间相比,输出时序窗口已经准确地变小,结果与DCC中的峰峰值比较吻合。实际中,可以从分析波形重叠中有效地获得DCC[51]。

图8-16 用于时序窗口估计的DCC

a)波形重叠引起的时延变化 b)测量获得的时延变化曲线

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。