虽然电感效应对片上互连的建模日益重要,但是RC等效电路对片上大多数互连建模而言仍然足够精确,特别是局部层和中间层互连。这种参数提取对设计前期和版图后期而言都是必需的。在早期的自顶向下设计流程中,为了便于设计综合并发现主要的时序及信号完整性问题,将互连寄生参数考虑进来是至关重要的。当分层设计最终转化为平面设计后,需要从版图提取互连寄生参数值以验证设计要求是否得到满足。一般情况下,对一个定义明确的版图图形,应用三维电磁场求解技术可以获得RC和L值。在实际的设计周期中,这些数值方法(如有限差分法、有限元法、矩量法)可以实现非常高的精度,但是其面临着两个重要的限制。首先,在前期的设计规划阶段,不可能为这些场求解器提供详细的版图信息,因此这种方式的灵活性就受到限制。其次,当一个芯片上晶体管的总数超过几百万个时,全电容矩阵的计算极其耗时,实际上很难采用。由于这些原因,人们在设计时采用解析模型或查找表方法,并结合版图模式识别算法来获得运行高效的参数提取。这些解析模型或查找表模型的精度与需要花费很大代价从三维场求解器或测试结构测量结果中获得的数据相比并不逊色。

RC提取的建模方法 片上互连结构一般由矩形横截面的金属互连构成,在各层间使用曼哈顿布图方式(见图8-1)。这种结构不仅简化了制造过程和布线算法,而且极大地减小了RC建模工作的复杂度。对宽度为w、厚度为t的金属(见图8-1b),可采用下式计算其单位长度的直流电阻R:

式中,ρ为金属电阻率(铜:ρ=2.2μΩ·cm,铝:ρ=3.3μΩ·cm)。例如,典型的w=0.8μm和t=0.8μm的3mm长全局互连,在直流条件下可以建模为103Ω的电阻。除了金属互连,垂直连接多层金属的通孔也对路径电阻有贡献。在90nm工艺节点,单位面积的通孔电阻大约为 。因此0.25μm×0.25μm的通孔可以建模为1.6Ω的等效电阻。随着金属层数的稳步增加和通孔尺寸的不断缩小,不能再忽略通孔电阻对时序模型的影响;它会给关键路径总时延带来额外10%的时延[8]。

。因此0.25μm×0.25μm的通孔可以建模为1.6Ω的等效电阻。随着金属层数的稳步增加和通孔尺寸的不断缩小,不能再忽略通孔电阻对时序模型的影响;它会给关键路径总时延带来额外10%的时延[8]。

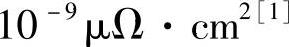

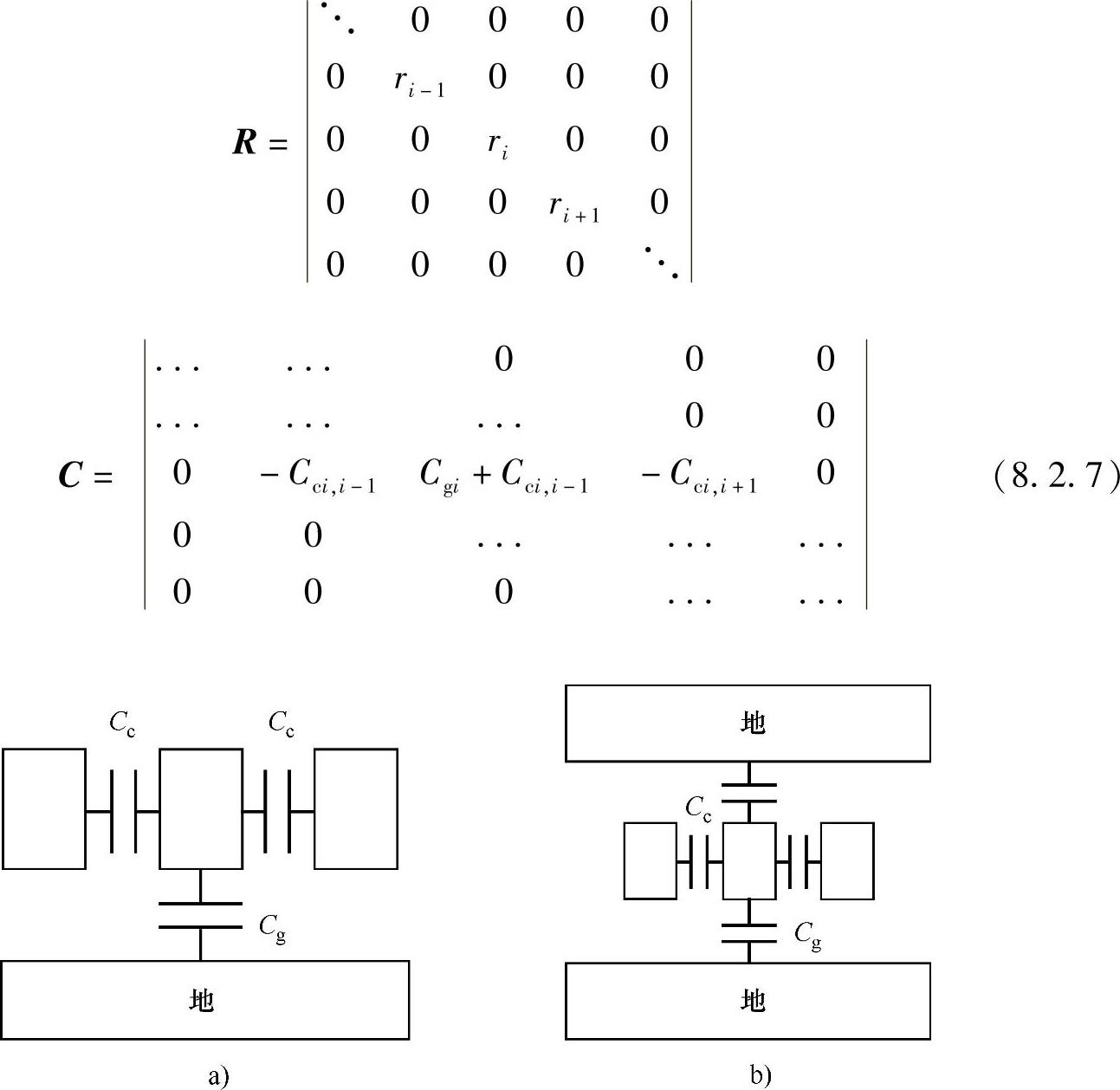

金属电容描述了互连之间经由电场的耦合程度。根据耦合互连是否接地,经常将其称之为金属——地的电容Cg(若耦合互连交流接地);或金属——金属电容Cc(若耦合互连是信号线)。Cg和Cc剖面图的实例如图8-6所示。根据麦克斯韦方程,电场可以被金属互连屏蔽。因此容性耦合是一种短距离效应:当同一层有多条互连时,容性耦合随着互连邻近程度的增加而迅速减弱。例如,在与另一条或者更远的互连之间的Cc(也就是在耦合互连之间至少有一条互连)与最近互连之间Cc相比,一般减少10%。为了简化建模并且同时维持足够的分析精度,仅需要提取并分析最直接相临互连之间的Cc;与更远互连之间的Cc值可以忽略。这样就形成了下面的矩阵,一般被用于共面互连(见图8-6)的RC分析:

图8-6 局部和全局互连的二维电容模型(横截面图)

a)顶层互连 b)局部层互连

每个ri值可由式(8.2.6)计算获得,而Cg和Cc元素可以由解析模型或使用如下面描述的查找表方式产生。

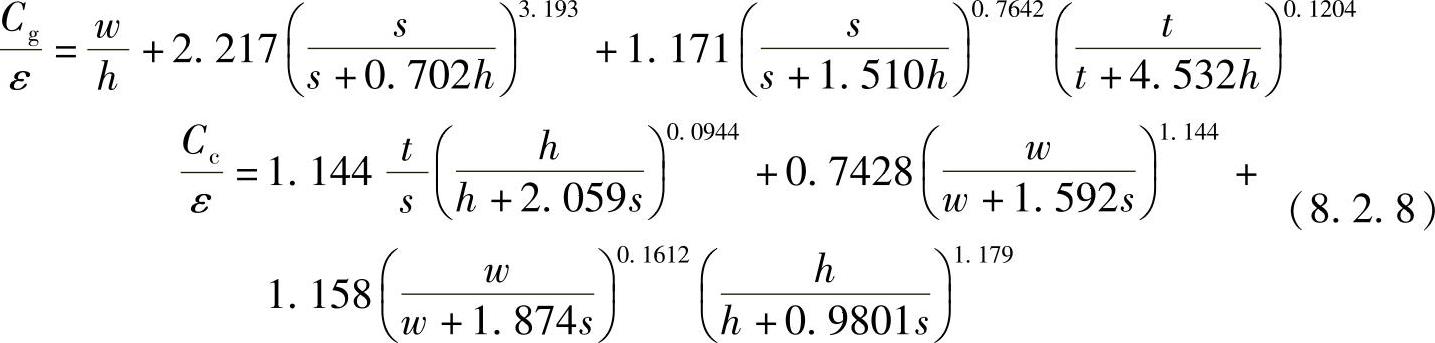

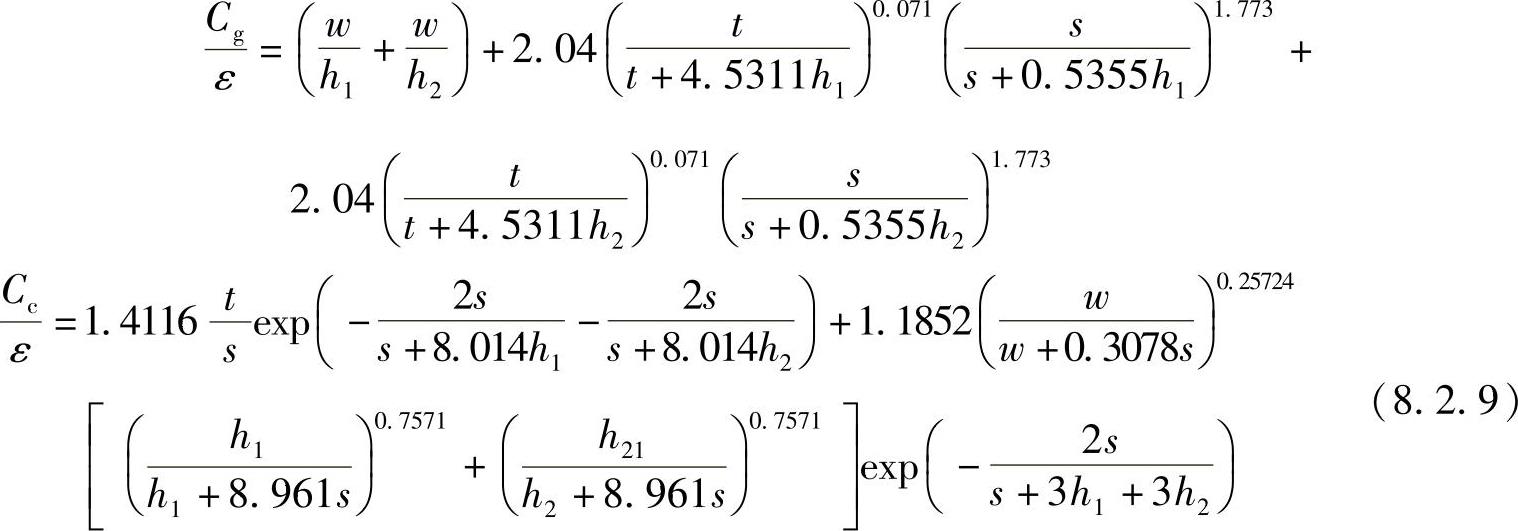

为了有效计算设计综合和版图验证阶段的电容,基于版图模式,多层三维互连经常被简化为二维[9-11]或准三维结构[12]。如果互连上方或下方层中的布线很密集,它们会近似为一个接地等位面,这就形成了图8-6所示的二维模型。这时,Cg和Cc变成了直接与互连横截面面积相关的函数。Cg和Cc解析模型如下所示[11]。(https://www.xing528.com)

对顶层互连(一个接地等位面之上的金属互连,见图8-6a)有

对局部层互连(两个接地等位面之间金属互连,见图8-6b有

式中,ε为介电常数,尺度变量的含义如图8-1所示(式(8.2.9)中的h1和h2分别是金属线上方和下方的介质厚度)。这些模型表达式是基于物理分析,其中的系数值是通过对场求解结果拟合得到的。因此,它们可以很容易地进行缩放,并可以实现误差仅为5%~10%的精度。获得单位长度Cg和Cc的二维值后,再乘以互连长度就得到总的电容。

在更一般的情况下,长互连可以首先被分成几个片段,每个片段可以与预先定义的版图模式匹配。版图模式的选定取决于同一层以及上面一层或下面一层的布线情况[12,13]。采用已经通过场求解器或半导体测量验证过的解析模型或查找表,求出每个片段Cg和Cc[13],就可以构造出C矩阵。然后,再与R矩阵一起,就可以进一步使用分析工具求解RC时序和噪声特性。

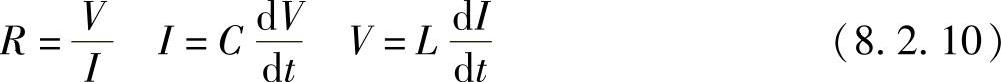

片上寄生参数的表征 寄生参数表征技术,不仅用于模型验证,它对于从半导体测量直接建模甚至更重要。例如,如果有简单适用的技术可以测量电容值,典型版图模式的电容值可以直接从测试结构中提取,并用于建立查找表,从而减小了过程的不确定性和模型误差。因为与片外金属互连相比,片上互连更窄而且更短,所以他们具有更小的电容(小于100fF/mm)和电感(小于1nH),因此,要有一种易实现的高分辨率表征技术。RLC和电气参数(电压和电流)之间的关系为

根据第一个方程,金属电阻值可以容易的从I-V测量获得。片外电容可以通过LCR仪器测量表征。人们更希望能实现片上互连电容的提取,由于它们的值较小。根据方程(8.2.10),基于电荷的电容测量(CBCM)技术已经研发出来并且实现了小于0.1fF的分辨率[14]。这个技术的精度受限于测试电路中的晶体管失配。当电路频率高于GHz时,必须要有在频域(例如S参数表征)和时域对高频阻抗的表征技术[15,16]。这些技术通常可以同时应用于片上和片外RLC提取。然而,测试过程要比一般的本地测试更复杂,并且需要特殊的测试结构。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。