在讨论解决信号完整性问题的设计方法学之前,首先引入通常被用来评价片上互连性能的品质因数(figures of merit,FOM):

1.信号时延和能量损耗

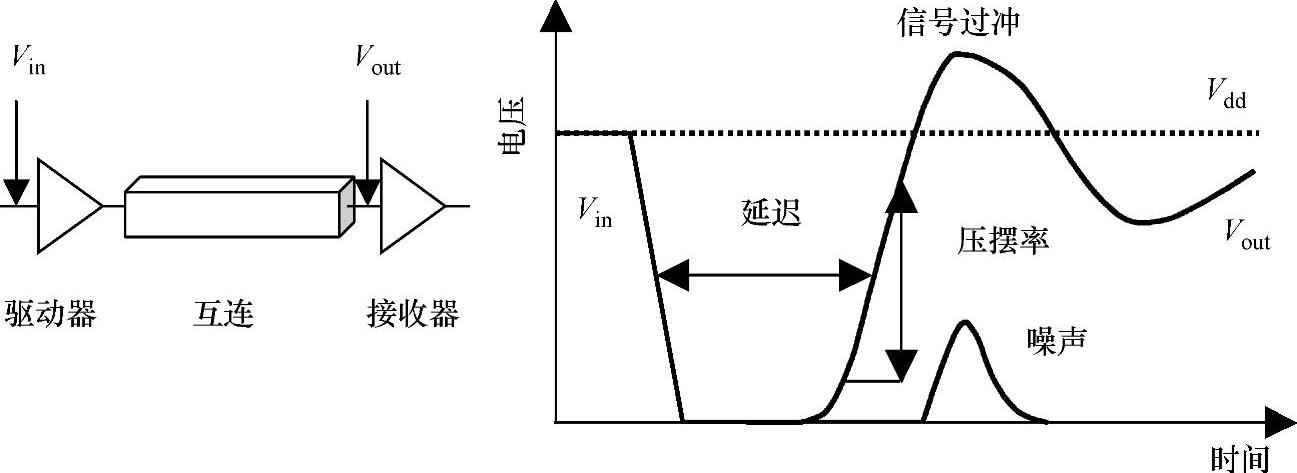

信号时延(时序)是同步设计中主要的品质因数指标。如图8-3所示,信号时延是从驱动门输入信号50%Vdd位置点到互连末端(即接收器的输入)处信号50%Vdd位置点之间的时间间隔。时延是驱动门和互连负载的函数。在0.25μm和高于0.25μm的工艺,主要的互连负载是金属对地的电容,因此互连负载与金属互连的长度成正比。随着工艺的缩小,互连负载的主要部分已经变成了耦合电容。因此,信号时延不仅是局部互连几何尺寸的函数,也与相邻互连的信号开关活动有关。未来设计中的另外一个问题是互连的能量消耗 。为了实现更高的集成度,芯片中互连总长度急剧增加(例如,在45nm工艺节点,可以长达5km),导致了更大的总电容和更大的能耗。要注意互连能耗与总电容以及Vdd的平方成正比,并且基本上与互连电阻和电感无关。

。为了实现更高的集成度,芯片中互连总长度急剧增加(例如,在45nm工艺节点,可以长达5km),导致了更大的总电容和更大的能耗。要注意互连能耗与总电容以及Vdd的平方成正比,并且基本上与互连电阻和电感无关。

2.串扰噪声

一般来说,噪声源于给定互连与相邻互连通过耦合电容或者互感的耦合。在180nm工艺节点,交叉耦合仅仅对高性能的设计有严重影响。然而,当进入100nm以下时,对所有IC设计,互耦合就成为与时序、功耗和面积同等重要的问题之一。串扰噪声严重影响着电路的性能,主要表现在两个方面:首先较大的噪声会触发并引起错误的逻辑开关动作,并且因此会造成故障;其次也是更普遍的问题是串扰噪声使原来的开关波形失真,并且与开关的时刻有关,会引起不同程度的严重时延(在65nm工艺节点会高达80%)。这样,如果设计者继续使用当前的最坏情况设计方法,针对这种时序不确定性来预留合适的容限,结果将是无法承受的过度时序预算,而且还会使性能变得很差。在8.3.4节,我们将讨论对噪声敏感的时序分析。

3.波形完整性(压摆率、过冲和信号振铃)(https://www.xing528.com)

在数字设计中,理想的信号是一个在0和Vdd之间瞬时开关的阶跃函数。然而,这种模型仅是实际开关波形的近似。实际信号的压摆率不会是零,并且可能有信号过冲和振铃。压摆率(或上升边)定义为信号从最终值的10%变到90%(对目前更新的设计,从30%到70%)时需要的时间。由于驱动器强度有限,互连是有损耗的,实际的信号开关会有一定的压摆率,这将延缓了信号的稳定和传输时间。当电路速度快速升高时,需要对这部分的时序预算严加控制。更快的电路速度还会导致其他的高频电磁效应,如不希望的传输线行为和很难实现阻抗的匹配。另外,升高的电路速度也会导致信号过冲(即高于Vdd或低于地)和振铃,如图8-3所示。信号的振铃破坏了趋稳时间;过冲会引起接收器中栅氧的可靠性问题,特别是传输门电路。当工艺缩小的趋势持续下去并且数据通信的速率接近每秒太位时,目前这种互连结构中的波形失真最终会限制带宽[3,4]。因此需要新的互连工艺和设计技术来克服这种限制。

图8-3 片上互连分析时主要的品质因数定义

从设计的角度看,需要仔细研究这些品质因素以防止信号完整性退化。这些指标将贯穿应用到本章的性能分析和设计方案中。受最近的工艺——设计联合优化的推动,这些性能品质因素还会被进一步整合进工艺方案中,以使片上通信的吞吐量最大化。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。