DRAM中存储电容是第一个关键元件。通过与位线电容CBL的简单电荷共享,加给读出放大器的可用信号Vsignal与存储电容Ccell之间关系为

一般位线电容是存储器单元电容的5~10倍。位线电容包括总的存储器电容加读出放大器的电容。DRAM单元的设计者努力将各代工艺的存储器单元电容维持在相同的水平。这样,对存储电荷泄露损失的敏感度就有了可比性。电容分配比也保持为常数。如果位线电容随着工艺的发展而降低的话,甚至能够使电容分配比得到改善。

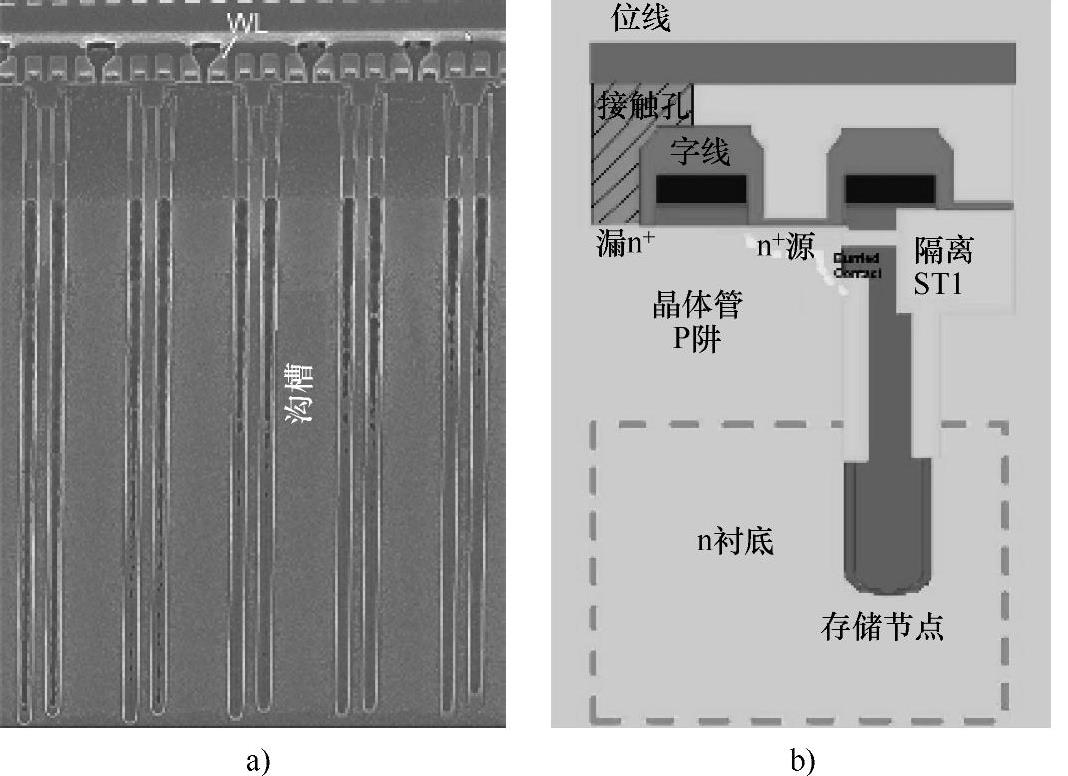

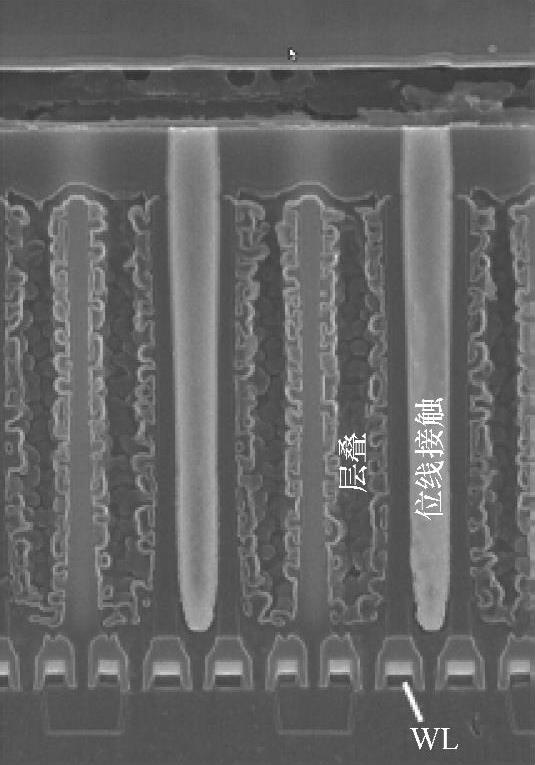

特征尺寸下降到100nm工艺时,实现巨大电容的一个关键技术是三维电容。扩展到第三维的可以采用硅上(层叠电容)技术或深入到硅中(沟槽电容)的技术。这两项技术的实例如图7-5和图7-6所示。

图7-5 a)沟槽电容单元实例:沟槽刻蚀深入到硅中。注意:与定义特征尺寸f的字线的长度相比,沟槽深度比其大数倍 b)字线与相关存储器单元简图

图7-5a所示为一个沟槽电容存储器单元,而图7-5b所示为沟槽单元的示意图。沟槽刻蚀深入到硅中,这极大地增加了基座上的可用电容面积。图7-6是一个层叠电容单元。因为层叠不能做的太高,因此层叠电容结构的面积增强能力小于沟槽方式。如果使层叠太高,对上面介质层进行平坦化处理以便在层叠电容的顶部加工附加金属层将会变得很困难。为了补偿这个缺点,可以采用更进一步的电容增强技术。如图7-6所示,电容可以采用粗糙的表面以增加面积。用更高εr的材料来替代常规的介质层可以进一步提高电容。目前广泛使用的高εr材料是Ta2O5。(https://www.xing528.com)

图7-6 层叠电容单元实例

(注意层叠电容波纹状的表面采用了附加的表面增强技术)

通过持续地改善,这种方法在最近的几代工艺中已经获得了成功。然而,伴随着缩放带来的另一个问题是如何通过电容和(或)接触的串联电阻给单元电容充电和放电。在特征尺寸较小的情况下,刻蚀一个较深的沟槽(见图7-5)意味着总阻抗的急剧增加。对层叠方式,接触孔从位线向下到硅衬底的长位线存在相似的问题。在阵列的字线之间都需要实现位线和层叠接触。

这样,直到100nm时代,主要重点还是针对如何实现足够大的电容。然而,在未来,如何保证实现足够小的阻抗以保持RC常数足够低也将成为必须给予同样关注的重点问题。这将不得不采用低欧姆接触材料和较浅的栅层叠。

另外一种解决问题的努力途径是,保持电容继续缩小,但是使总接触电阻维持在一个电容能被读出的水平。然而,如果单元设计者能够保持电容大致为常数,他们就需要给存储器晶体管提供足够的电流,从而具有足够快速读取单元的能力。因此时下一节的主题就是讨论晶体管的缩放问题。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。