在动态存储器中,数据以易失电荷的方式存储在电容中。由于易失的特性,如果每个存储器单元不能得到定期刷新,存储电荷将会流失。在早期3T1C单元[1]的基础上,出现了优化的1T1C单元[2]。1T1C是英文全称的首字母缩写,表示存储单元中包括一个用于存取信息的晶体管和一个用于存储信息的电容。

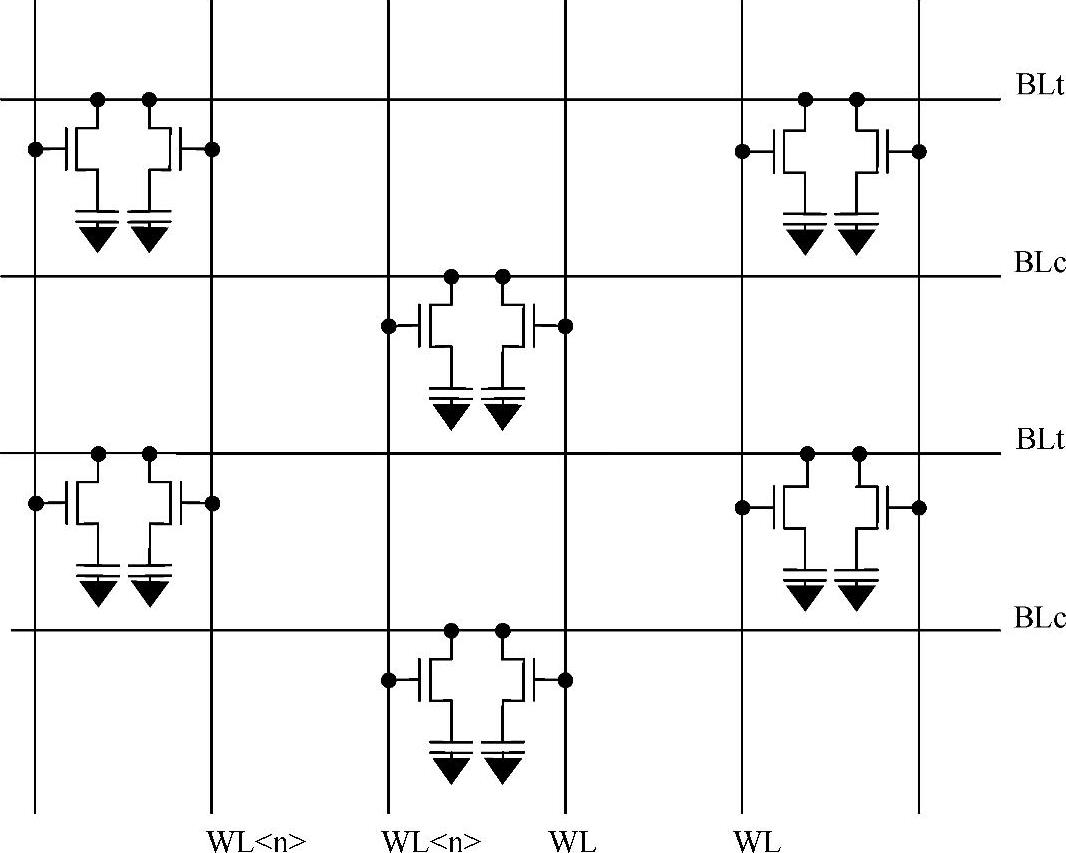

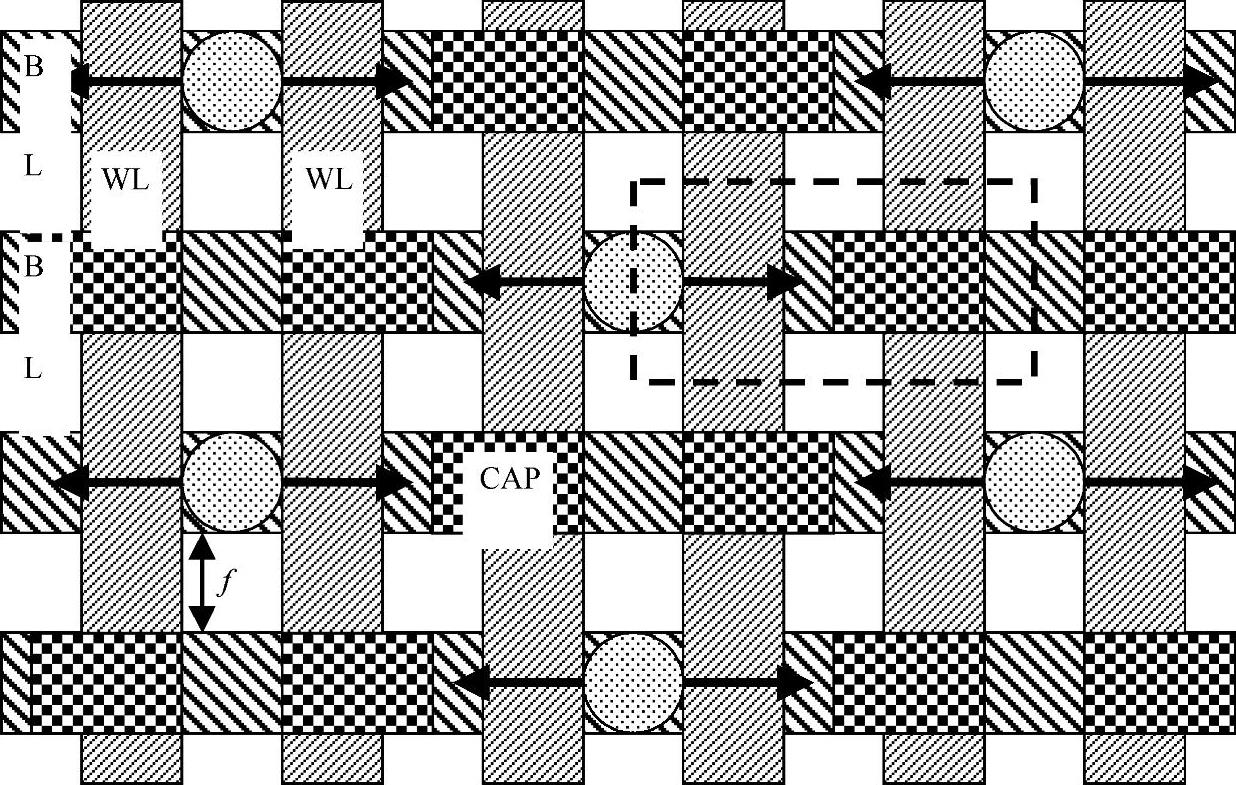

图7-1所示为一个存储器阵列中存储器单元分布的电路图。字线与排成一列的存取晶体管的栅极相连;位线与字线垂直,与排成一行的源极相连。普通电容的理想化版图如图7-2所示,其中没有包括关于如何在硅上实现这种结构的细节。图中反映的相关信息只是每个这种单元版图需要8f2的面积,其中f是工艺的最小特征尺寸。面积为8f2的单元在给定排列下可以高效地实现折叠式位线结构[3]。这种结构中,位线被安排为互补对,位线(t)与互补位线(c)交替排列。字线连接到位于位线或互补位线上的单元(见图7-1)。

现代绝大多数DRAM中(即使不是全部)选择的是折叠式位线结构。在折叠式位线结构中,在位线的每个互补对中有一个精确的差分放大器——读出放大器。当以最近的距离放置差分对时,大多数的阵列噪声以共模噪声的形式出现,从而不会导致差分放大信号的退化。

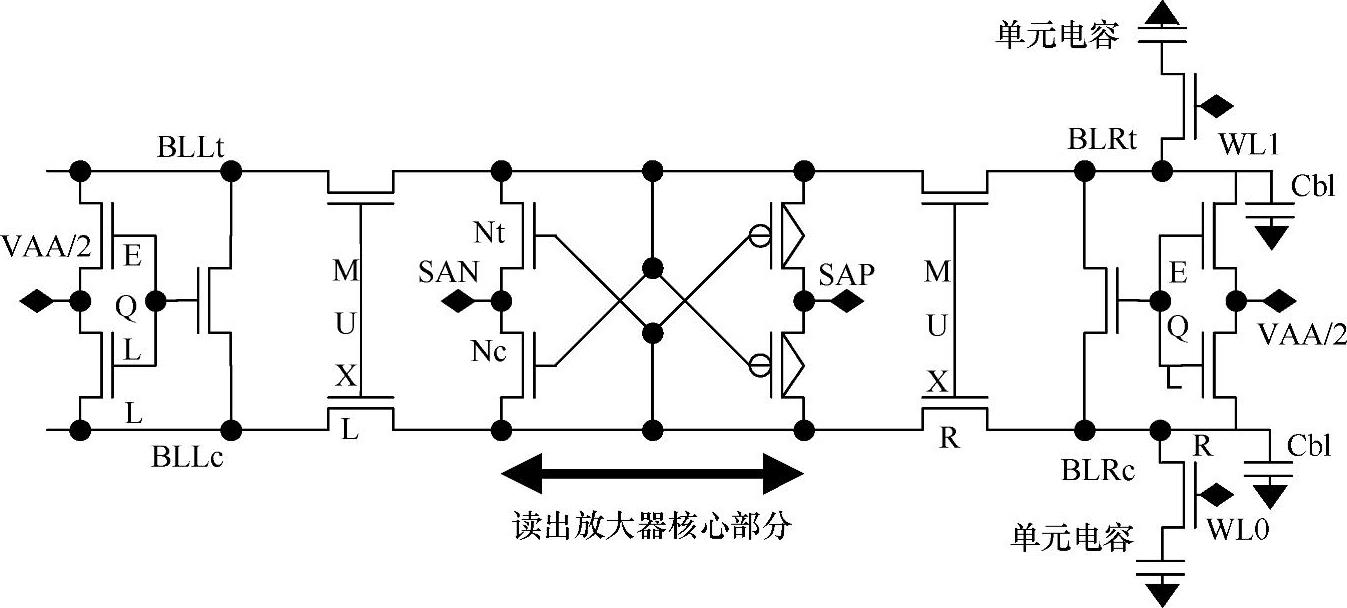

图7-3是一个典型的读出放大器电路图。为了实现面积最小化,一个读出放大器被其左右两个存储阵列共享。通过多路复用器选择被读出的阵列。均衡器晶体管使读出放大器偏置到所期望的电压值为VAA/2的期望的预充电电平,其中VAA是位线电压的高电平。最后,位于中间的交叉耦合对是读出放大器的核心。

图7-1 DRAM阵列电路示意图:垂直方向的是字线(WL),水平方向的是位线(BL)。逻辑上,位线由位线/互补位线对组成

图7-2 面积为8f2的DRAM阵列的理想版图:虚线框为存储器单元的轮廓;箭号代表传输器件中的电流方向;圆表示位线与传送器件扩散区的接触;字线(BL)为垂直走向;位线方向与其垂直。存储电容(CAP方格盘型图案)面积可能超过1f2

(https://www.xing528.com)

(https://www.xing528.com)

图7-3 经典的共享DRAM读出放大器的电路图

(为清晰起见,图中仅显示了一条数据存取器件路径,其没有缩放限制。多路器和预充电器件在左、右阵列之间选择。这样,一个读出放大器可以用于两个相邻的存储器阵列。Nt和Nc是读出放大器n型晶体管,用于实现位线或互补分支的下拉。)

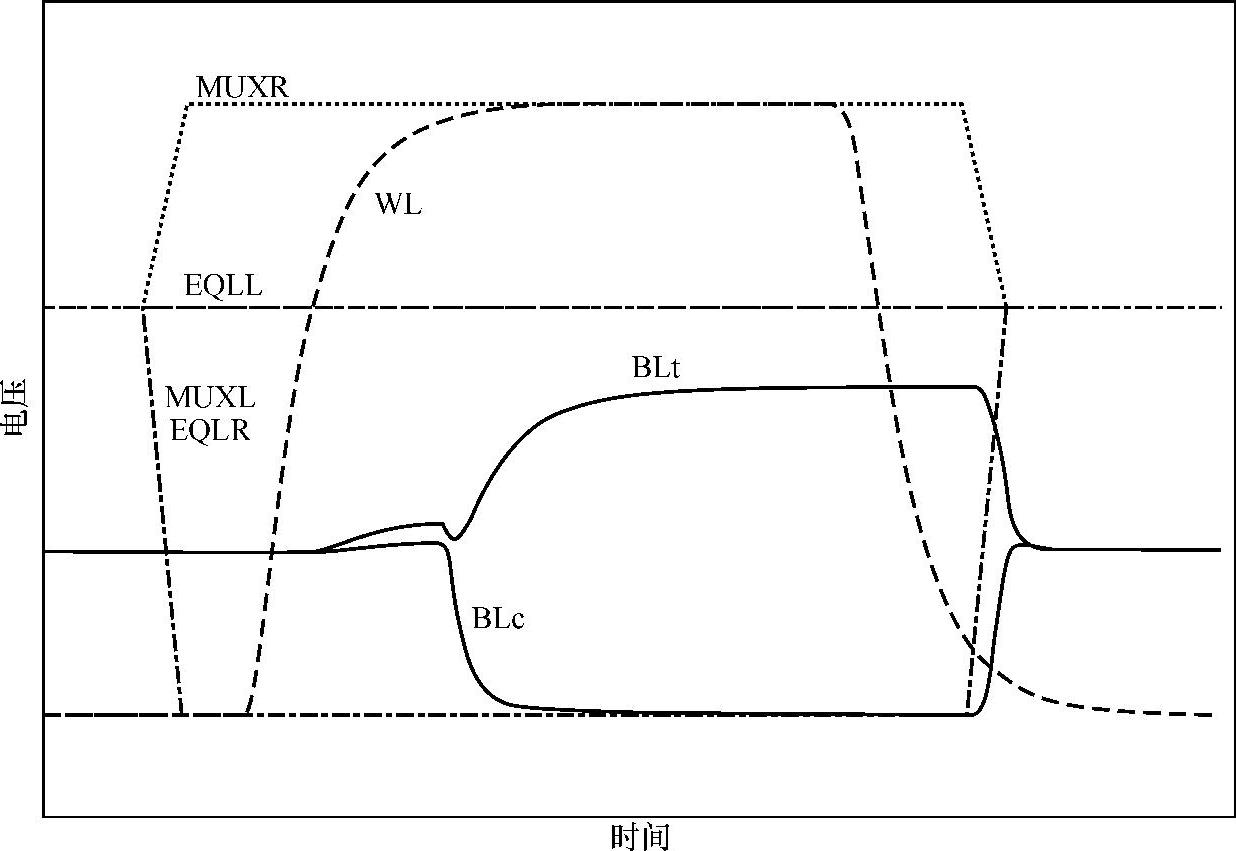

图7-4 阵列中典型的信号波形图

(图中所示的是读1的情况。实线代表位线和互补位线。虚线代表字线信号,点线和点划线分别代表均衡器和多路器信号。MUXL和EQLR相互重叠)

图7-4所示为一个典型的存储器读取周期。最初,阵列保持在预充电状态。所有的多路器门和均衡器门被偏置到高电平并且位线保持在VAA/2。作为激活时序的第一步,首先要选择读出的是右侧还是左侧阵列。在本例中,读出的是右侧阵列。这是通过关闭左侧的多路复用器件(MUXL)和右侧的均衡器(EQLR)达到的。之后,字线会被抬高,存储器单元中存储的电荷转移到位线上。具有均衡电压的位线和存储单元的高(低)电势之间的电荷共享将引起位线电压的增加(降低)。读出后,读出放大器会收到使能信号,放大互补位线对上的差分信号。放大器的使能是通过将SAN从VAA/2驱动到0而将SAP从VAA/2驱动到VAA实现的。这样,存储的信号会自动而正确地被写回到存储单元。这个循环结束后,信号回到它们的预充电电平。

这种读出方案有几个优点。对提供均衡、左-右选择、和放大的电路来说,器件数最少。另外,互连方案也相对简单,可以获得一个较紧致的版图。这对DRAM的芯片尺寸来说极其重要,因为DRAM中需要的读出放大器非常多。除了具有面积优势之外,从功耗的观点来看,这个电路也是非常有益的。在放大期间,只有即将向上走的位线需要从VAA/2充电到VAA,这个过程消耗的电荷为CBL×VAA/2(CBL为位线电容)。在这个周期结束时,电平为VAA的高电平位线和电平为0的低电平位线通过均衡器晶体管被简单的短路,达到常规的VAA/2预充电电平。因此,实现快速均衡,并且不需要附加电流。

这种采用交叉耦合读出放大器的1T1C单元实现了高度的面积优化。因此,当工艺缩小进入sub-100nm工艺时,仍希望保持这种基本结构。然而,要实现它需要解决多个令人困扰的问题。实际上任何情况都有与自身相关的特殊问题。这些将在下面几节讨论。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。