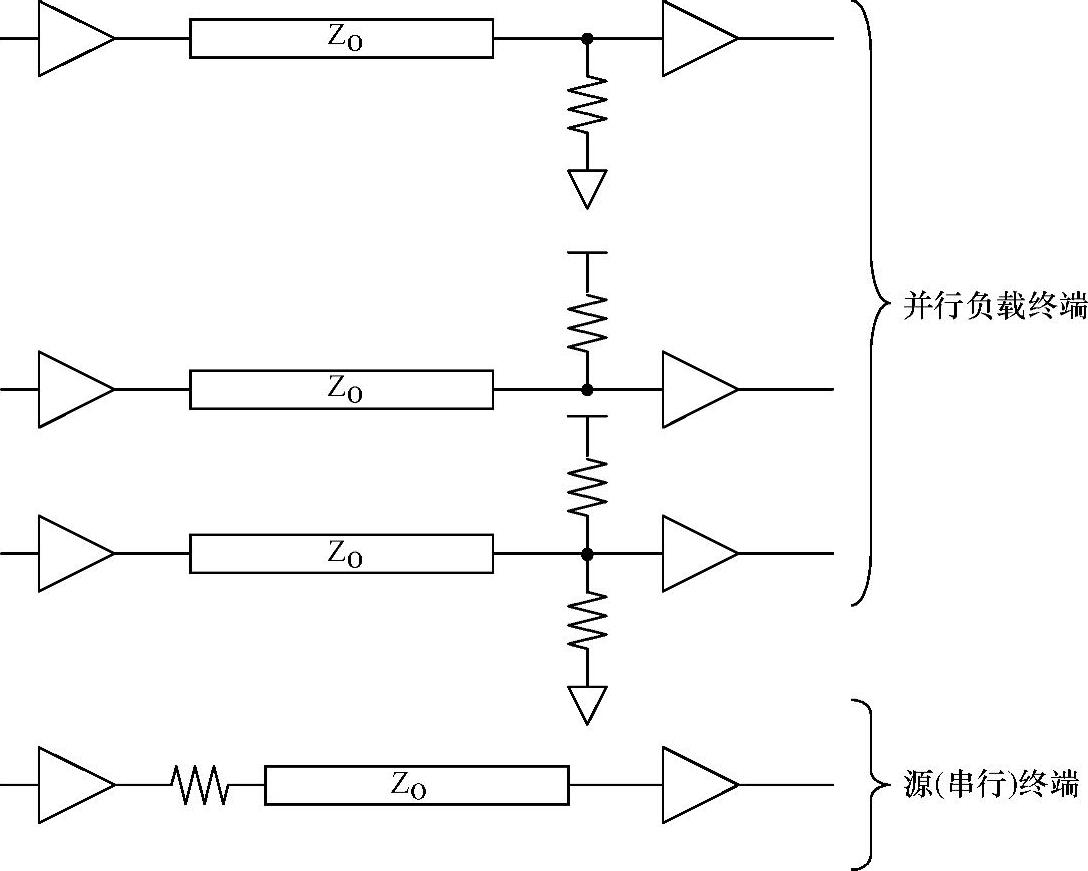

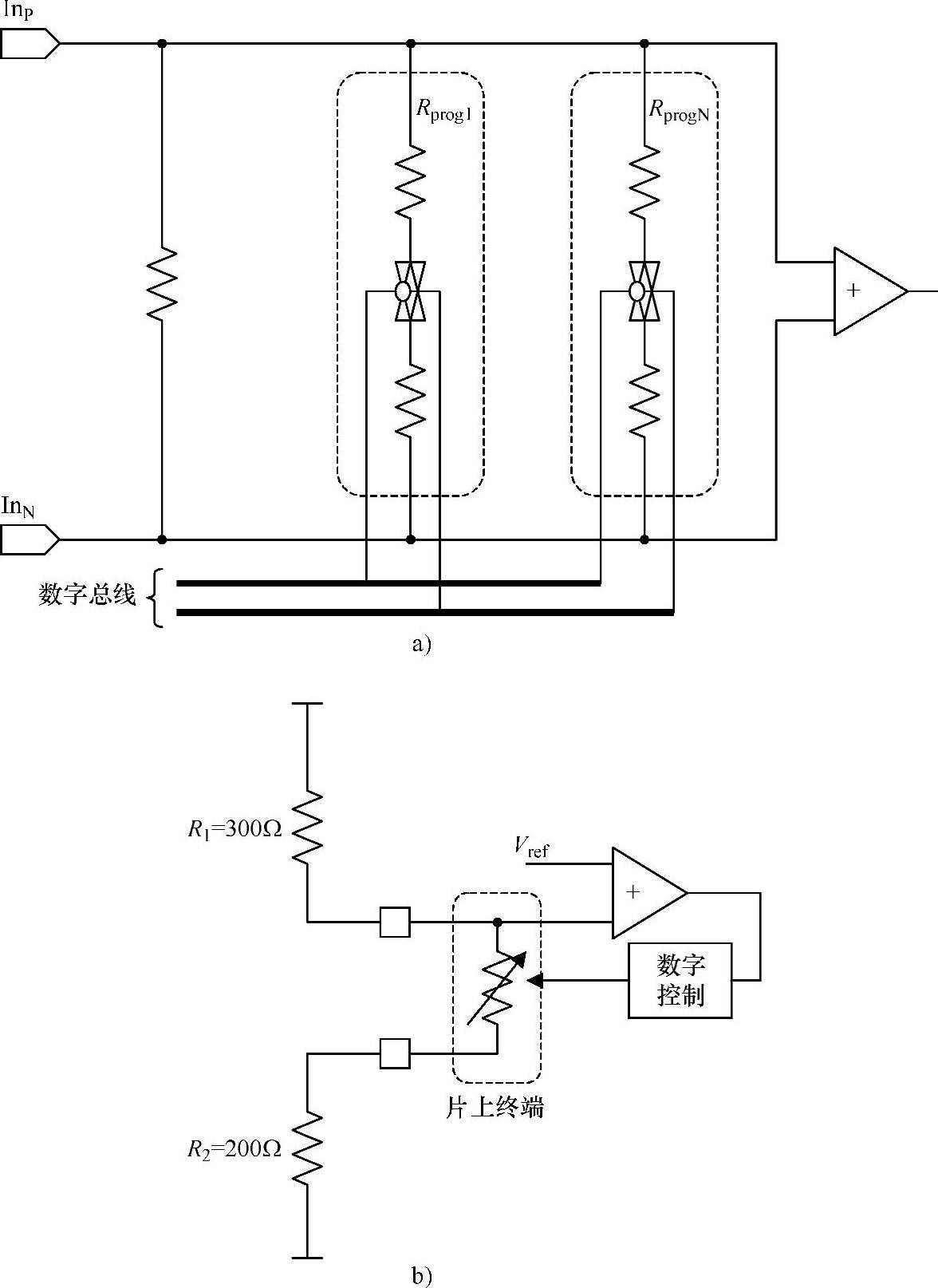

对于单个片上的巨大系统,匹配已经变成一个主要的问题。图6-13所示为一个单端端接方案简图。该端接被用来实现驱动器、传输线和负载之间的阻抗匹配,使得由阻抗不连续引起的反射最小化。这些反射将引起码间干扰。对一定规模的ASIC,有几百个I/O引脚,在电路板上给这些高速接口提供合适的匹配,即使不是不可能的,也极其困难。因为这些引脚密集的元件附近非常拥塞,高I/O速度和剩余的封装与板级残余会引起另外的中断。这些限制迫使IC设计者在晶片上包含有匹配,特别是对速度非常高的接口。这种趋势在每个工艺节点都变得越来越强烈。图6-14a所示为一个差分输入缓冲器可能的输入端接方案简图。匹配电阻被放置在差分输入缓冲器的输入之间。数字总线被用来设定并联电阻的值以获得期望的端接电阻值。因为它们对电压的低敏感性、受控的寄生电容和适当的精度,用未硅化的多晶形成电阻,虽然它们的变化范围仍然在±20%。因此,采用并联的电阻方式来补偿工艺和温度的变化。这种实现方法意味着必须采用几种电路来检查并补偿这些因素。一种经常采用的设计是利用外部电阻得到参考电压,包括一个如图6-14b所示的片上端接电路形式。虽然这个方法有效,但是它要求两个额外的引脚并且将外部元件的精度耦合到整体的电路性能中。第二种方法是使用微调以产生精确的基准。这种方法可以不增加额外的引脚,但是增加了相当的复杂度,并加大成本,因为微调方案必须使用几种熔丝技术(金属或多晶)。另外,当增加片上端接时,必须监测下述关键参数:

(1)工艺、电源和温度变化。这些参数的敏感度必须至少最小化到±10%。

图6-13 单端端接方案

(https://www.xing528.com)

(https://www.xing528.com)

图6-14 a)可变输入端接方案简图 b)校准电阻设定所要求的电路简图

(2)附加的引脚电容。必须使该参数最小化;否则,它将限制接口的最大工作速度。

(3)电容与电压的函数关系。必须使电容与电压的关系最小化,并且变化量应该小于总电容的5%,以确保电压对电容的影响不会严重影响接口的性能。

提供一个精确的端接阻抗以维持与驱动源和传输线的匹配是非常重要的。使端接阻抗具有可配置的特点也正变得更加重要,这样终端用户可以根据自己的特殊用途选择合适的端接。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。