图6-9 16位宽、最大速率为1Gbit/s的并行接口仿真结果 a)有片上去耦 b)无片上去耦

在这些先进工艺中,由于更多的I/O接口数、增加的边缘变化率和增加的工作频率,I/O缓冲器的开关噪声变成了一个相当严重的问题。前几代的设计可以依赖电路板级的去耦,但是现在的高速I/O要求在晶片上实现去耦以满足现代先进系统的严格要求。这一点如图6-9所示。图中显示了一个高速接口的输出,当其余15个I/O采用伪随机位组合触发时,该高速接口能够采用最大数据率(1Gbit/s)触发。如果未包括片上去耦,显而易见会出现码间干扰。没有片上去耦,电源电压降低和地弹会变得非常重要,以至于会引起输出缓冲器失效,特别是所有I/O受到从高电平到低电平或者从低电平到高电平转换的驱动时。实现有效的板级去耦变得很困难,因为引脚数很多,很难将去耦电容放置到与器件足够靠近的位置,特别是需要放在片外时。另外,即使在器件封装上作出了重大的改进以减小寄生电阻和电感,对当前的I/O需求,这仍然是不充分的。总之,必须不断强调的是,在这些先进工艺中,如果要求I/O必须支持各种高速接口,那么芯片上的I/O去耦就是绝对必须的。

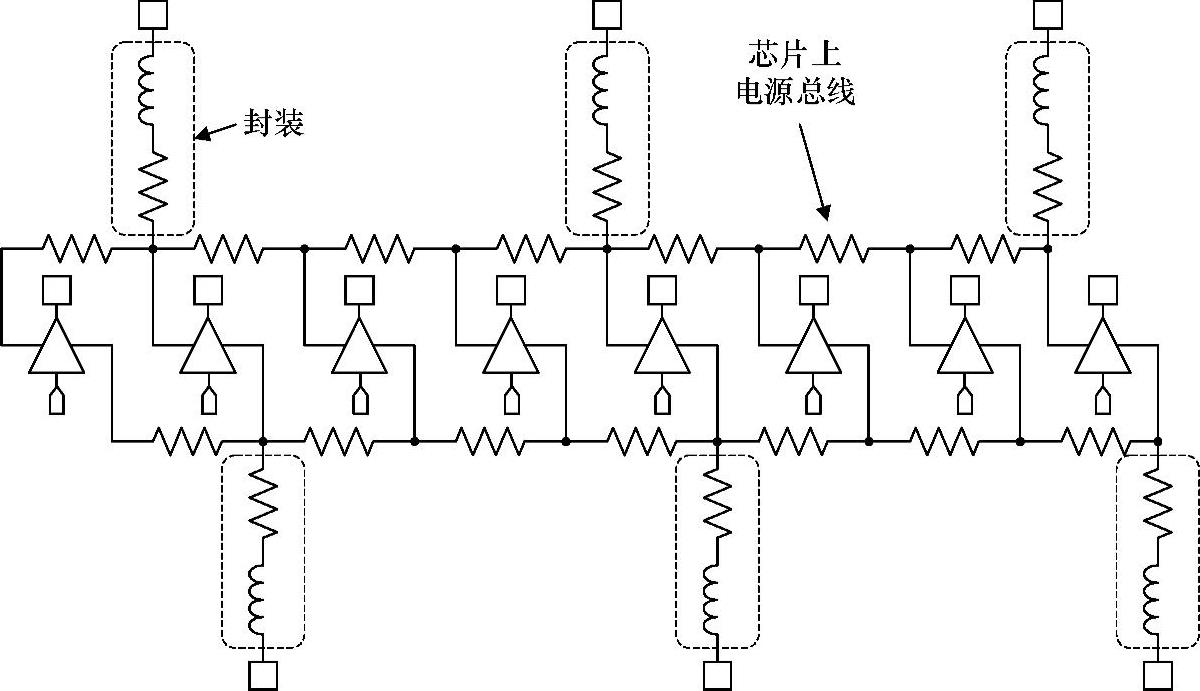

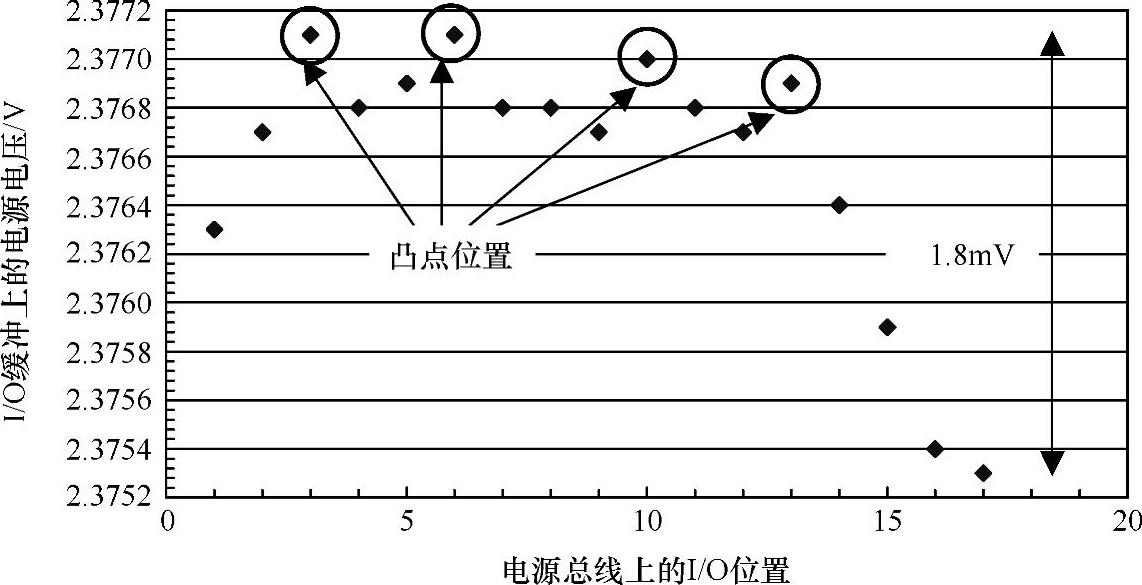

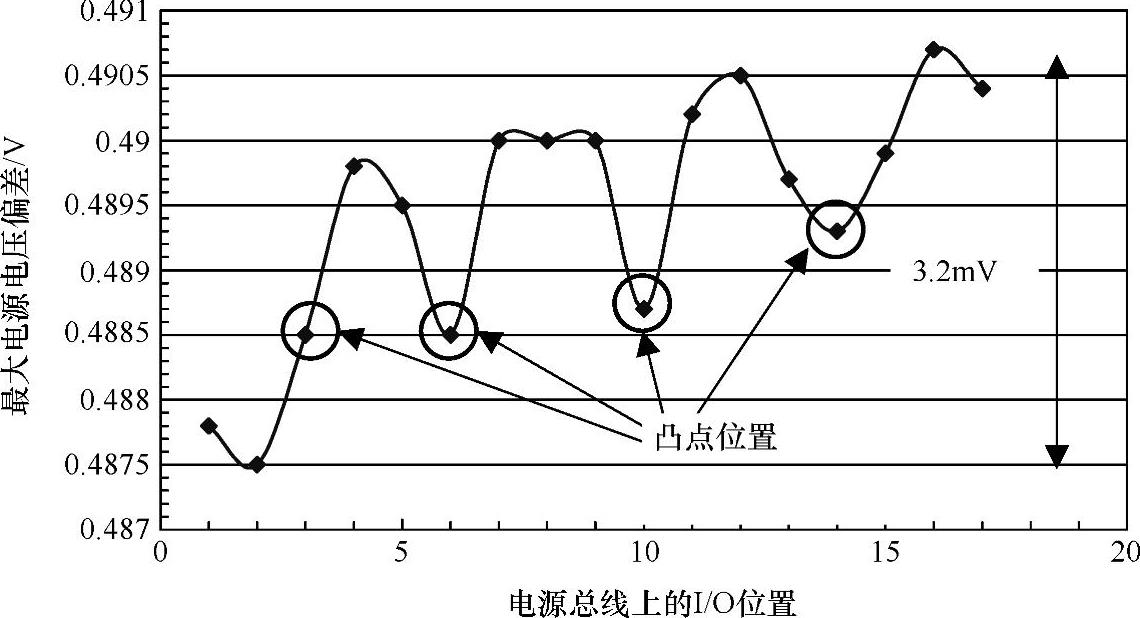

图6-10所示为一排有8个I/O的I/O组合与相关寄生元件的模型简图,其中忽略了封装寄生电容。此图经过扩展,可以对采用倒装焊封装的有68个I/O的实际I/O组合进行仿真。I/O开关对I/O处电源电压的影响如图6-11和图6-12所示。这个模型将I/O分成4簇,以简化仿真。封装和芯片寄生参数是基于90nm工艺估计的。每个I/O采用不同的去耦量以描述片上去耦的重要性。两个图显示的是每个I/O增加9pF的结果。图6-11所示的平均电源电压曲线说明了电源总线未能精确平衡,这也解释了为什么尽管电源差别很小,即平均电源电压几乎为常数,但是一个终端的IR压降大于另一个。图6-12所示的最大电源电压变化是通过在每一个缓冲器组(四个缓冲器一个组形成一个簇)计算VCC和VSS电平差值,并确定最大偏差。表6-1总结了不同去耦程度对I/O组电源电压的影响。

图6-10 包括了寄生元件的一排8个I/O的简图

图6-11 采用100MHz频率开关时I/O上的平均电源电压

图6-12 半数I/O发生开关作用时的最大电源电压变化(具有68个I/O的组中,每I/O缓冲器采用9pF去耦)

表6-1 电源电压变化与去耦程度关系的总结

基于这些仿真明显可见,一个I/O组上局部的感性和阻性压降会变得很重要。即使采用低感性封装,片上去耦仍是使IR压降最小化的唯一有效方法。为了成功设计一个I/O系统,推荐采用下列步骤。

(1)评估每个I/O的抽取电流。获得抽取电流的正确时序以得到精确的建模是非常重要的。应该对每个工艺角都做这些工作。(https://www.xing528.com)

(2)决定I/O主电源线可用的金属层的多少(这一般是基于上一代工艺电源线获得的),为I/O主电源线形成一个实际的电阻网络。这一步必须与第一步结合使用以确保不与电迁移规则相冲突。在这个阶段应该监视电迁移以确保各个级别(晶片上、凸点、封装和焊球)都有合适的主电源线。

(3)评估在凸点和I/O电源网格间形成阻性连接的I/O电源总线凸点走线。这时假定采用倒装芯片封装,但是该方法对金属线键合封装同样适用。

(4)开发/获得凸点模型。凸点的电阻范围为0.01~0.1Ω,电感约为0.1nH,因此它们不能被忽略。

(5)评估封装电阻网络。即使在封装中使用等位面图形(plane),仍然有一定的电阻和电感。

(6)开发/获得封装焊球的模型。焊球的电阻范围为0.01~0.1Ω,电感约为0.2nH以上,因此它们不能被忽略。

一旦完成这些任务,就必须进行折衷研究以观察增加或减小I/O电源总线、增加凸点、减小凸点与电源总线之间的走线、增加封装走线/plane和添加附加焊球等的影响。基于这一分析可以确定凸点和焊球之间的相对位置。另外,可以在增加附加的片上去耦电容、电源总线和封装凸点和焊球之间进行折衷。为了得到适当的折衷,这个分析必须在项目启动之初进行。

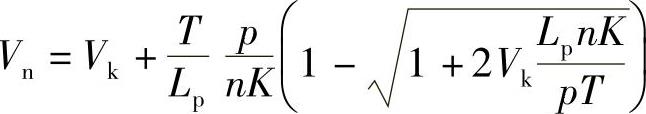

参考文献[16]介绍了考虑电源噪声增加引起负反馈的情况下,I/O开关噪声效应的一般模型。其中电源噪声可以由下式得到:

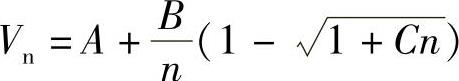

式中,Vk=VCC-Vin;T为输出缓冲器达到最大值时的上升时间;Lp为每个引脚或焊球的电感;p为引脚或者焊球数;n为同时开关的输出缓冲器数;K=μnCox(W/L)。这个简单的方程并不能给详细设计I/O电源组提供必要的精确度,但是这个方程的一般形式对确定多个I/O同时开关的电源噪声效应非常有用。对方程做修正,可以得到:

然后使用SPICE仿真确定系数A、B和C,可能得到一个确定I/O开关噪声效应的简单表达式。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。