ESD已经在第5章做过分析,因此这里仅作简要讨论。对较厚氧化层器件来说,这些先进工艺中的ESD保护问题没有变化。用于0.5μm、0.35μm和0.25μm工艺的保护方案仍然有效。ESD保护方案的主要变化集中于对采用薄氧化层器件的I/O的保护,因为它们对ESD更加敏感。第二个目标是如何减小输入和输出缓冲器的附加电容以改善整个系统的速度。确保电容不会随着所加电压的变化而改变也非常重要。否则,时延会随着电压变化,引起信号的额外抖动。

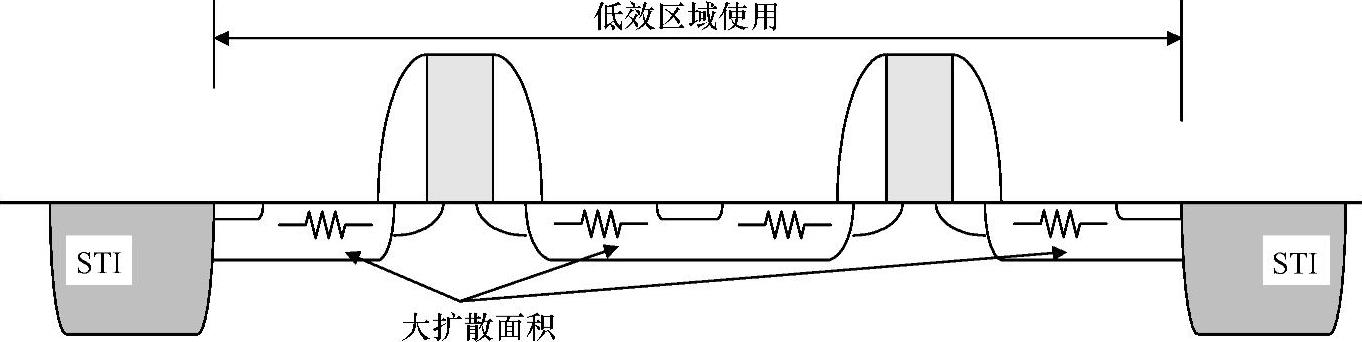

图6-8所示为如何设计输出缓冲器以改善ESD性能的简图[9]。该结构没有使用最小栅到接触间距,而是利用远大于最小设计规则的间距,多数情况下间距在1μm以上。这个技术有效地增加了接触孔到漏和源的电阻,这个电阻起着限流的作用以改善器件的ESD性能。图中器件源和漏两侧均有电阻。一些研究表明漏侧的电阻对器件保护来说就足够了,因为串联电阻减小了漏电压,这最终减小了栅上的应力。这个电阻在二次击穿的回压期间起着减小漏极电流的作用[15]。但是,增加接触孔到栅的间距会增加器件的输出电容,从而使输出缓冲器的性能退化。这个方式的第二个缺点是输出缓冲器占据了很大的面积。最后一个缺点是要求有一个无金属硅化的区域,这就要求增加掩膜层数。

(https://www.xing528.com)

(https://www.xing528.com)

图6-8 采用双“指条”的输出缓冲器晶体管简图

保护输出缓冲器的第二种方式是使用参考文献[14]中介绍的方法,即在输出压焊点上添加一个晶闸管(SCR)结构,保护连接到压焊点的器件免受ESD损伤。只要SCR结构的触发电压小于输出器件的击穿电压,这个方案将非常有效。采用这个方案,输出器件就可以设计得非常小,从而减小引脚电容。采用低电容SCR结构可以进一步减小引脚电容。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。